SC3 Manual

Edit this on GitLab

INTRODUCTION

As a leading manufacturer of smart function modules, NAI offers over 100 different modules that cover a wide range of I/O, measurements and simulation, communications, Ethernet switch, and SBC functions. Our serial communications smart function modules provide high-speed, programmable RS-232/RS-422/RS-485, isolated or non-isolated, communication channels. Each channel has one transmit and one receive signal pair (±) as applicable. This user manual is designed to help you get the most out of our serial communications smart function module.

For a brief description of the module and complete list of specifications, click here for the SC3 data sheet.

|

Note

|

Manual revision B2 marked the introduction of the SC3 product update to include the additional synchronous (SYNC) mode functionality. The SC3 SYNC mode and function capability is available for products identified with DOM > 1/2020, Mod-HW ≥ Rev. B and FPGA/Firmware ≥ Rev. 00001.00003. |

SC3 Overview

NAI’s SC3 module offers a range of features designed to suit a variety of system requirements, including:

Eight Communication Channels: The SC3 module offers eight high-speed, programmable communication channels supporting RS232, RS-422, and RS-485 protocols. These channels can be configured as eight asynchronous (async) channels or four synchronous (sync) channels. In Sync Mode, the module can set up clock signals (clk) on the companion pair channels (CH1-CH4 clk companion channels are CH5-CH8)

General Purpose Input/Output (GPIO): The SC3 module includes General Purpose Input/Output (GPIO) functionality, enhancing its versatility.

Data Transfer Efficiency: For asynchronous communications, data transfers occur within just two baud clocks, ensuring rapid data exchange. Synchronous communications achieve efficient data transfers in as little as 15 baud clocks.

Digital Noise Filtering: The SC3 module features digital noise filtering on receivers, enhancing signal quality and reliability.

Receiver Control: Users can selectively enable or disable specific receivers, providing fine-grained control over the communication channels.

Interrupt-Driven Operation: The SC3 module can operate in an Interrupt-Driven environment, delivering notifications of all events to the system. When flow control mode is selected, the module handles operations automatically with minimal system intervention, streamlining the communication process.

Buffer Capacity: The module boasts 1MBx16 receive and transmit buffers, ensuring ample storage for data transfer.

Built-in Test: The SC3 module comes with a built-in test feature, simplifying diagnostics and maintenance.

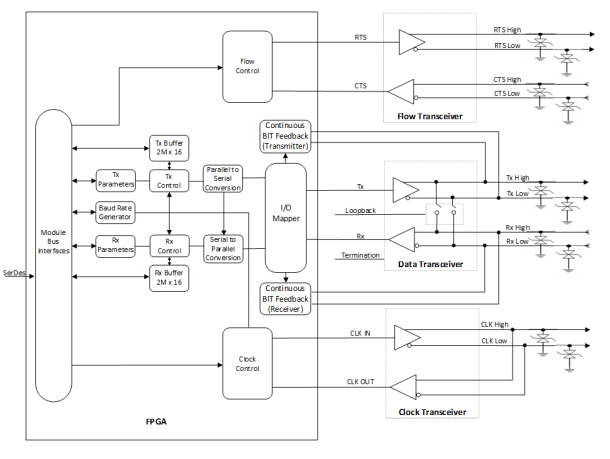

PRINCIPLE OF OPERATION

Each channel of the module can be individually software configured for RS-232C, RS-422 or RS-485 Asynchronous/Synchronous Serial Communications or GPIO. See table below for more specific pinouts between modes. The architecture avoids latency problems because all data transfer is done in hardware and not in software. Any incoming data, no matter how many channels are active, in whatever mode, can be immediately extracted. FPGA design simplifies programming and usage.

- |

RS232 |

RS232 GPIO |

RS232 HW Flow |

RS422/485 |

RS422/485 GPIO |

RS422/485 HW Flow |

RS422/485 Sync |

RxDLo - 1 |

RXD - 1 |

GPI2 - 1 |

RXD - 1 |

RXDLO - 1 |

GPI-LO - 1 |

RXDLO - 1 |

RXDLO - 1 |

RxDHi - 1 |

n/a |

GPI1 - 1 |

CTS - 1 |

RXDHI - 1 |

GPI-HI - 1 |

RXDHI - 1 |

RXDHI - 1 |

TxDLo -1 |

TXD - 1 |

GPO2 - 1 |

TXD - 1 |

TXDLO - 1 |

GPO-LO - 1 |

TXDLO - 1 |

TXDLO - 1 |

TxDHi - 1 |

n/a |

GPO1 - 1 |

RTS - 1 |

TXDHI - 1 |

GPO-HI - 1 |

TXDHI - 1 |

TXDHI - 1 |

… |

|||||||

RxDLo - 5 |

RXD - 5 |

GPI2 - 5 |

RXD - 5 |

RXDLO - 5 |

GPI-LO - 5 |

CTSLO - 1 |

CLKINLO - 1 |

RxDHi - 5 |

n/a |

GPI2 - 5 |

CTS - 5 |

RXDHI - 5 |

GPI-HI - 5 |

CTSHI - 1 |

CLKINHI - 1 |

TxDLo - 5 |

TXD - 5 |

GPO2 - 5 |

TXD - 5 |

TXDLO - 5 |

GPO-LO - 5 |

RTSLO - 1 |

CLKOUTLO - 1 |

TxDHi - 5 |

n/a |

GPO5 - 5 |

RTS - 5 |

TXDHI - 5 |

GPO-HI - 5 |

RTSHI - 1 |

CLKOUTHI - 1 |

… |

Configuration

Before the user can write to any configuration register, certain steps must be followed to ensure the module accepts the user specified configuration. The steps are as follows:

-

Write a 0 to the Enable Channel bit of the Tx-Rx Configuration register to tell the hardware that we are about to change the configuration.

-

Wait for the Channel Configured status of the Realtime Channel Status registers to read a 0.

-

Write all desired configuration registers.

-

Set the Enable Channel bit of the Tx-Rx Configuration register to 1 to notify the hardware that it can read all the configuration registers.

-

Wait for the Channel Configured status in the Realtime Channel Status register to read a 1 before proceeding to send/receive data.

Async/Sync Modes

All eight channels can be configured in asynchronous mode or the first four channels can be configured for synchronous modes. Mixing asynchronous and synchronous modes is also possible.

Sync Mode Channel Pairs

The user can configure any of the first four channel sof the SC3 to operate in any of the following synchronous modes: HDLC, Mono-Synchronous or Bi-Synchronous. When any of these channels are configured for a synchronous mode, the channel will need to pair with another channel to make sue of its transmitter and receiver to handle clock input and output signals. Channel pairs are as follows: 1&5, 2&6, 3&7, 4&8.

Hardware Flow Control

The user can configure any of the first four channel sof the SC3 to operate in hardware flow control mode by setting the RTS/CTS Flow Control bit of the Tx-Rx Configuration register to a 1. When a channel is configured in this mode, the channel pair’s transmitter and receiver will be used for the Request to Send (RTS) and Clear to Send (CTS) signals. The channels pairs are the same as in sync mode.

GPIO Mode

The SC3 is configured for GPIO mode via the Interface Levels register. Setting the GPIO bit to 1, sets a channel to GPIO mode. It is also necessary to choose either RS-232 or RS-422 to determine the GPIO signal level.

|

Note

|

As shown in the table on page 7, single ended RS-232 provides GPI 1, GPI 2, GPO1 and GPO 2. RS-422 provides GPI 1 and GPO 1 only. |

To set an output (GPO) channel to a high state, set the Channel Control register RTS/GPO 1 or GPO 2 bits, to 1. The default is 0 (low). Inputs (GPI) are monitored by the Dynamic Status register, bits CTS/GPI 1 and GPI 2, which provide real-time status monitoring of the GPI inputs. The Latched Status register, bits CTS/GPI 1 and GPI 2, latch when an input is received and are cleared when a 1 is written to the register. The Interrupt Enable register bits CTS/GPI 1 and GPI 2 when set to a 1, will create an interrupt. To invert the GPI/GPO inputs and outputs, set the Tx-Rx Configuration register bits Invert CTS (GPI) and Invert RTS (GPO), to 1. See the Register Descriptions for more information.

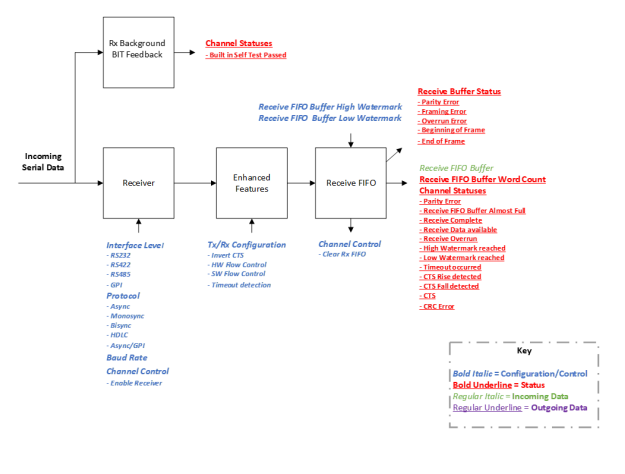

Gap Timeout Status

The Gap Timeout Occurred status gets set when there’s data in a channel’s receive buffer but there’s no activity on a channel’s receiver for approximately three byte-times. To use the Gap Timeout feature, set the Enable Gap Timeout bit in the Tx-Rx Configuration register to a 1. When receiving asynchronous data, monitor the Gap Timeout status bit of the Channel Status register to know if a timeout occurred. The status is cleared after all the data in the receive buffer is read or cleared.

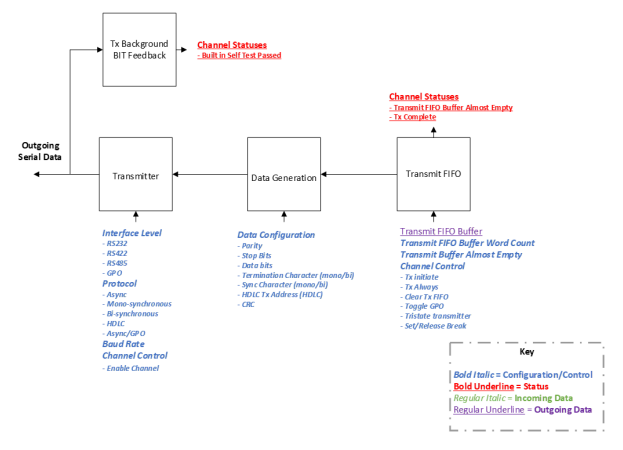

Serial Built-In Test/Diagnostic Capability

The SC3 module supports three types of built-in tests: Power-On, Continuous Background and Initiated. The results of these tests are logically ORed together and stored in the BIT Dynamic Status and BIT Latched Status registers.

Power-on Self-Test (POST)/Power-on BIT (PBIT)/Start-up BIT (SBIT)

The power-on self-test is performed on each channel automatically when power is applied and report the results in the BIT Status register when complete. After power-on, the Power-on BIT Complete register should be checked to ensure that POST/PBIT/SBIT test is complete before reading the BIT Dynamic Status and BIT Latched Status registers.

Continuous Background Built-In Test

The background Built-In-Test (BIT) or Continuous BIT (CBIT) runs in the background for each enabled channel. It monitors the transmit and receive lines using dedicated hardware to detect any differences in the levels. When in synchronous mode the clock lines are monitored for a clock presence. The technique used by the automatic background BIT test consists of an “add-2, subtract-1” counting scheme. The BIT counter is incremented by 2 when a BIT-fault is detected and decremented by 1 when there is no BIT fault detected and the BIT counter is greater than 0. When the BIT counter exceeds the threshold value, the specific channel’s fault bit in the BIT status register will be set, the internal threshold can be scaled via the Background BIT Threshold register. Note, the interval at which BIT is performed is dependent and differs between module types. The “add-2, subtract-1” counting scheme effectively filters momentary or intermittent anomalies by allowing them to “come and go“ before a BIT fault status or indication is flagged (e.g. BIT faults would register when sustained; i.e. at a ten second interval, not a 10-millisecond interval). This prevents spurious faults from registering valid such as those caused by EMI and/or dirty power causing false BIT faults. Putting more “weight” on errors (“add-2”) and less “weight” on subsequent passing results (subtract-1) will result in a BIT failure indication even if a channel “oscillates” between a pass and fail state. Results of the Continuous BIT are stored in the BIT Dynamic Status and BIT Latched Status register.

Initiated Built-In Test

The Initiated Built-In-Test (IBIT) is an internal loopback available for each channel of the SC3 module. The test is initiated by setting the bit for the associated channel in the Test Enabled register or (for legacy applications) setting the Initiate BIT bit of the Tx-Rx-Configuration register to a 1. Prior to initiating the test, the user must disable the channel, and its respective pair, by writing a 0 to the Enable Channel bit of the channel’s Tx-Rx Configuration register. BIT will not run if the channel is enabled. After the user disables the channel and initiates BIT, they must wait a minimum of 5 msec then check to see if the bit for the associated channel in the Test Enabled register or (for legacy application) Initiate BIT bit of the Tx-Rx-Configuration register reads a 0. When the SC3 clears the bit, it means that the test has completed, and its results can be checked. If the bit has not cleared after 10ms, the test has timed out and not run. In the event this should occur, the user should verify that the channel, and its pair, has been disabled. The results of the IBIT is stored in the BIT Dynamic Status and BIT Latched Status registers, a 0 indicates that the channel has passed and a 1 indicates that it failed.

Receiver Enable/Disable

A Receiver Enable/Disable function allows the user to turn selected receivers ON/OFF. When a receiver is disabled, no data will be placed in the buffer.

Serial Data Transmit Enhancement

An additional asynchronous mode to support “Immediate Transmit” operation has been incorporated. This mode immediately transmits serial data anytime the transmit buffer is not empty. There is no requirement to set the Tx Initiate bit before each transmission, which simplifies system traffic and overhead, since only the actual data byte being transmitted needs be sent to the transmit buffer. Each channel has its own configurable Transmit and Receive buffer. The upper byte of each received word provides status information for that word.

Multi-Drop Link Mode (RS485)

The transmitter and receivers of up to 32 channels can be tied together in either Half or Full-Duplex mode. While in Multi-Drop Link Mode, the transmit line for each channel will automatically tri-state. When data in the transmit buffer is initiated, the transmitter will be taken out of tri-state and send the data. Once transmission is completed, the transmit line is automatically changed back to tri-state mode.

To program the serial channel for Multi-Drop mode, the interface level must be set to RS485, and the Tristate Transmit Line bit in the Channel Control register must be set to a 1.

Communication Module Factory Defaults: Registers and Delays

Address Recognition: |

Off |

Baud Rate: |

9600 |

CTS/RTS: |

Disabled |

Protocol: |

0, Asynchronous |

Interface Levels: |

5 (Tri-state mode) |

Termination Character: |

0x0003h |

Interrupt Level: |

0 |

Interrupt Vector: |

0x00 |

Mode: |

Asynchronous |

Number of Data Bits: |

8 |

Parity: |

Disabled |

Receivers: |

Disabled |

Transmit Buffer Word Count: |

0 |

Receive Buffer Word Count: |

0 |

Receive Buffer, Almost Full: |

0xFFF9B |

Stop Bits: |

1 |

Transmit Buffer, Almost Empty: |

0x0064 |

Tx-Rx Configuration: |

0 |

Channel Control: |

0 |

Data Configuration: |

0x0108 |

Preamble: |

0 |

Receive Buffer High Watermark: |

0xFFF9B |

Receive Buffer Low Watermark: |

0x0800h |

XON: |

0x0011h |

XOFF: |

0x0013h |

XON/XOFF: |

Disabled |

Time Out Value: |

0x9C40 |

A write to the following registers takes place immediately:

-

Transmit Data

-

Channel Control

-

Channel Interrupt Enable

-

Channel Interrupt Edge/Level

-

Summary Interrupt Enable

-

Summary Edge/Level

-

Interrupt Vector

-

Interrupt Steering

For all other registers, channel configuration protocol must be followed.

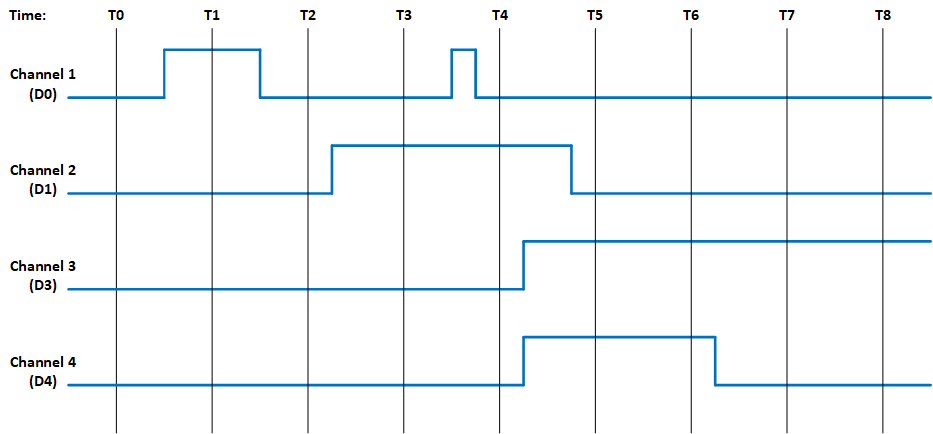

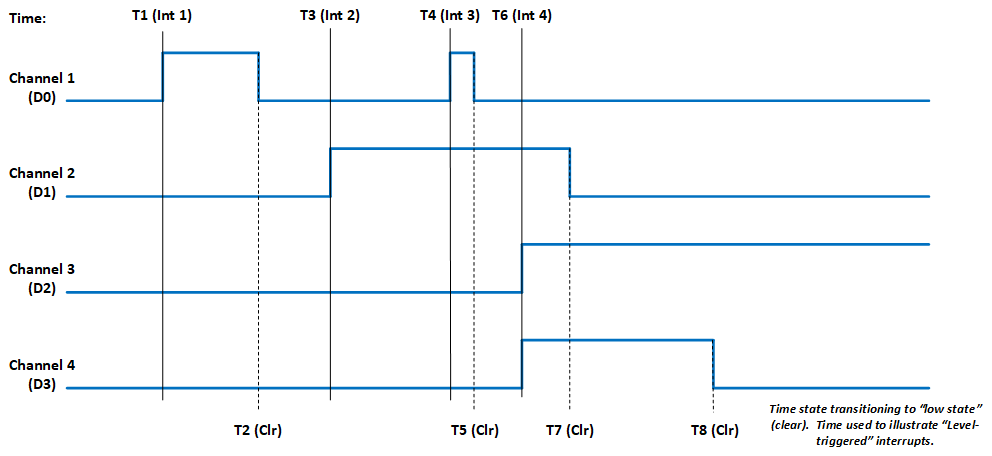

Status and Interrupts

The SC3 Serial Communications Function Module provide registers that indicate faults or events. Refer to “Status and Interrupts Module Manual” for the Principle of Operation description.

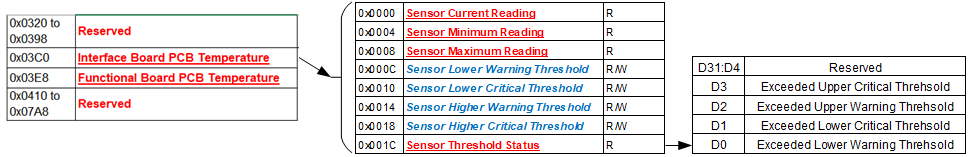

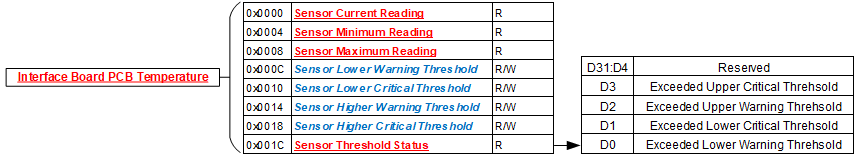

Module Common Registers

The SC3 Serial Communications Function Module includes module common registers that provide access to module-level bare metal/FPGA revisions & compile times, unique serial number information, and temperature/voltage/current monitoring. Refer to “Module Common Registers Module Manual” for the detailed information.

REGISTER DESCRIPTIONS

The register descriptions provide the register name, Type, Data Range, Read or Write information, Initialized Value, a description of the function and, in most cases, a data table.

Receive Registers

Serial data received are placed in the Receive FIFO Buffer register. The Receive FIFO Buffer Word Count provide the count of the number of elements in the Receive FIFO Buffer. The Receive FIFO Buffer Almost Full, Receive FIFO Buffer High Watermark and Receive FIFO Buffer Low Watermark registers provide the ability to specify the thresholds for the associated status in the Channel FIFO Status register.

Receive FIFO Buffer |

|

Function: |

Received data is placed in this buffer. |

Type: |

unsigned binary word (32-bit). |

Data Range: |

0x 0000 0000 to 0x 0000 FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Data is received is based on Protocol. |

|

Note

|

Receive FIFO Buffer is a self-clearing register. Performing a register read of the Receive FIFO marks the current location as 'read'. This moves the pointer to the next unread location and decrements the Receive FIFO Buffer Word Count register count by one. |

| Asynchronous/Asynchronous-GPI | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

PE |

FE |

0 |

0 |

0 |

EOF |

P |

D |

D |

D |

D |

D |

D |

D |

D |

D |

Bi-Synchronous/Mono-Synchronous |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

EOF |

0 |

D |

D |

D |

D |

D |

D |

D |

D |

HDLC |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

BOF |

0 |

ER1 |

ER1 |

ER0 |

EOF |

0 |

D |

D |

D |

D |

D |

D |

D |

D |

Asynchronous/Asynchronous-GPI |

||

PE |

= Parity Error |

A 1 indicates the calculated parity does not match the received parity bit. |

FE |

= Framing Error |

A 1 indicates a framing error was detected. |

EOF |

= End of Frame |

A 1 indicates an ETx character was received. Termination Character Detection must be turned on. |

P |

= Parity Bit |

This bit carries the parity bit of the last received character. |

Bi-Synchronous/Mono-Synchronous |

||

EOF |

= End of Frame |

A 1 indicates the End of Frame. Useful to identify multiple frames in large buffer. |

HDLC |

||

BOF |

= Beginning of Frame |

A 1 indicates first character of frame. Useful to identify multiple frames in large buffer. |

EOF |

= End of Frame |

A 1 indicates End of Frame. Useful to identify multiple frames in large buffer. |

ER2:ER0 |

= Last Frame Status |

000 = Good Frame, 111 = CRC Error |

Receive FIFO Buffer Word Count |

|

Function: |

Contains the number of words in the Receive FIFO Buffer waiting to be read back. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0 to 0x0010 0000 (Buffer Size) |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

Reads Integers. |

Receive FIFO Buffer Almost Full |

|

Function: |

Specifies the maximum size, in bytes, of the receive buffer before the Receive FIFO Almost Full Status bit D0 in the FIFO Status register is flagged (High True). |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0 to 0x0010 0000 (Buffer Size) |

Read/Write: |

R/W |

Initialized Value: |

1048475 (0x000F FF9B) |

Operational Settings: |

If the interrupt is enabled (see Interrupt Enable register), a System interrupt will be generated. |

Receive FIFO Buffer High Watermark |

|

Function: |

Defines the Receive Buffer High Watermark value. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

Low Watermark < High Watermark < 0xFFF9B |

Read/Write: |

R/W |

Initialized Value: |

1048475 (0xFFF9B) |

Operational Settings: |

When Receive FIFO Buffer size equals the High Watermark value, the High Watermark bit in both the FIFO Status and Channel Status registers is set to a 1 and: * If XON/XOFF is enabled, XOFF is sent, and/or * If RTS/CTS is enabled, RTS goes inactive. The Watermark registers are used for XON/XOFF and/or RTS/CTS flow control. The Receive Buffer High Watermark register value controls when the XOFF character is sent when using software flow control and controls when the RTS signal would be negated when using hardware flow control. For software flow control operation, the XOFF character would be sent once when the number of bytes in the Receive FIFO Buffer equals the value in the Receive Buffer High Watermark register. Once the XOFF has been sent, it cannot be sent again until the XON character has been sent. The valid state transitions to sending the XOFF character can be either no previous XON/XOFF character sent or a previous XON character sent. There is also a High Watermark Reached interrupt enable/disable bit in the Channel Interrupt Enable register and a High Watermark Reached bit in the Channel Interrupt Status Register. When the High Watermark is reached, an interrupt request will be generated, when the interrupt enable/disable bit is enabled. |

Receive FIFO Buffer Low Watermark |

|

Function: |

Defines the Receive Buffer Low Watermark value. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0 < Low Watermark < High Watermark < 0xFFF9B |

Read/Write: |

R/W |

Initialized Value: |

2048 (0x0800) |

Operational Settings: |

When Receive Buffer size equals the Low Watermark value, the Low Watermark bit in both the FIFO Status and Channel Status registers is set to a 1 and: * If XON/XOFF is enabled, XON is sent, and/or * If RTS/CTS is enabled, RTS goes active. The Watermark registers are used for XON/XOFF and/or RTS/CTS flow control. The Receive Buffer Low Watermark register value controls when the XON character is sent when using software flow control and controls when the RTS signal would be asserted when using hardware flow control. For software flow control operation, the XON character would be sent once when the number of bytes in the Receive FIFO Buffer equals the value in the Receive Buffer Low Watermark register AND an XOFF character has been sent prior to this XON character. The valid state transition to sending the XON character can only be from the state of a previous XOFF character that has been sent. There is a Low Watermark Reached interrupt enable/disable bit in the Channel Interrupt Enable register and a Low Watermark Reached bit in the Channel Interrupt Status Register. When the Low Watermark is reached, an interrupt request will be generated, when the interrupt enable/disable bit is enabled. |

Transmit Registers

Serial data to be transmitted are placed in the Transmit FIFO Buffer register. The Transmit FIFO Buffer Word Count provides the count of the number of elements in the Transmit FIFO Buffer. The Receive FIFO Buffer Almost Empty register provide the ability to specify the threshold for the associated status in the Channel FIFO Status register.

Transmit FIFO Buffer |

|

Function: |

Data to be transmitted is placed in this buffer prior to transmission. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x 0000 0000 to 0x 0000 01FF |

Read/Write: |

W |

Initialized Value: |

Not Applicable (NA) |

Operational Settings: |

Data words are 8-bit and occupy the register’s lowest significant bits (LSBs), or low byte. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D1 |

D |

D |

D |

D |

D |

D |

D |

D |

Note 1: Data only in Asynchronous mode when data bits are set to 9.

Transmit FIFO Buffer Word Count |

|

Function: |

Contains the number of words in the Transmit FIFO Buffer waiting to be transmitted. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0 to 0x0010 0000 (Buffer Size) |

Read/Write: |

R |

Initialized Value: |

0 |

Transmit FIFO Buffer Almost Empty |

|

Function: |

Specifies the minimum size, in bytes, of the transmit buffer before the Transmit Buffer Almost Empty Status bit D1 in the FIFO Status register is flagged (High True). |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0 to 0x0010 0000 (Buffer Size) |

Read/Write: |

R/W |

Initialized Value: |

100 (0x64) |

Operational Settings: |

If the interrupt is enabled (see Interrupt Enable register), a System interrupt will be generated. |

Configuration Registers

SC3 configurations includes setting the Interface Levels, Baud Rate, Protocol, Tx-Rx Configuration and if applicable, the Termination Character registers. Additional registers need to be configured specifically for Async or Sync modes.

Interface Levels |

|

Function: |

Configures the interface level (RS-232, RS-422, RS-485, Loopback, Tri-State, FPGA Loop-Back, GPIO) for the associated channel. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table |

Read/Write: |

R/W |

Initialized Value: |

5 (Tri-State) |

Operational Settings: |

Loopback selection connects the channel’s transmit and receive line internally. To implement, user must send data and look at Receive FIFO to verify that the sent data. Loopback is usually used for testing. Notes: Channels are programmed for loop back in pairs. For example, if channel 1 is programmed for loop back, then channel 2 will be also. This includes channels 3 and 4, 5 and 6 and 7 and 8. |

Bit(s) |

Interface |

Description |

D31:D15 |

Reserved |

Set Reserved bits to 0. |

D14 |

GPIO |

Needs to be ORed with either RS232 or RS422. |

D13:D8 |

Reserved |

Set Reserved bits to 0. |

D7 |

Disable termination resistor |

Disables termination resistor in-between the differential pairs of the transmitter and the receiver. Useful for RS485 Multi-Drop. |

D6:D3 |

Reserved |

Set Reserved bits to 0. |

D2:D0 |

Interface Level |

These bits set the interface level: (0:0:0) RS232 |

Baud Rate |

|

Function: |

Sets the baud rate for communications. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

300 bps to 10 Mbps Sync (1.5 Mbps Async) |

Read/Write: |

R/W |

Initialized Value: |

9600 bps |

Protocol |

|

Function: |

Configures the associated channel for either asynchronous, mono-synchronous, bi-synchronous, HDLC mode or mixed asynchronous and GPIO modes. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table |

Read/Write: |

R/W |

Initialized Value: |

0 (Asynchronous) |

Operational Settings: |

See table below. |

Bit(s) |

Protocol |

Description |

D31:D6 |

Reserved |

Set Reserved bits to 0. |

D5:D0 |

0x00 - Async |

Async-GPO: This mode can transmit general purpose signals on the channels transmitter while being able to receive async serial data on the receiver. Async-GPI: This mode can transmit async serial data on the channels transmitter while being able to receive general purpose signals on the receiver. |

Tx-Rx Configuration |

|

Function: |

Sets the transmit/receive configuration for the associated channel. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

BIT - Set Enable Channel bit, D24 low (0) to clear the selected channel. Set Initiate BIT bit D27 high (1) to initiate BIT. After 5 msec, a 0 should be read, which indicates that the BIT test is complete. The BIT Status register reports the channel status. |

Bit(s) |

Name |

Description |

D31:D28 |

Reserved |

Set Reserved bits to 0. |

D27 |

Initiate BIT |

Write a 1 to start built-in-test. The channel running BIT needs to be disabled, as well as it’s channel pair. For common module functionality see the Test Enabled register. |

D26 |

Invert RTS/GPO |

0 = Normal |

D25 |

Invert CTS/GPI |

0 = Normal |

D24 |

Enable Channel |

0 = Disable |

D23 |

Rx Suppression |

0 = Receiver Always On |

D22 |

Reserved |

Set Reserved bits to 0. |

D21 |

Idle Flag |

Idle Flag (0x7E) Transmission |

D20 |

Enable Gap Timeout |

0 = Ignore gap timeout |

D19 |

Append CRC |

0 = No CRC |

D18:D17 |

CRC |

(0:0) 16-Bit CRC (Mono/Bi-Sync only) |

D16 |

CRC Reset Value |

0 = Ones |

D15 |

Timeout Detection |

Turns on timeout detection |

D14 |

XON/XOFF Char as Data |

0 = Stripped |

D13 |

XON/XOFF Flow Control |

Turns on Software Flow Control |

D12 |

Termination Character Detection |

0 = Ignore termination character |

D11 |

Sync char as data |

0 = Stripped |

D10:D8 |

Reserved |

Set Reserved bits to 0. |

D7 |

Address Length |

0 = 8 bits |

D6:D4 |

Address Transmission/Recognition (HLDC only): 0x0 - Addressing Off |

Addressing Off: Don’t send address, receive data from any address. |

D3-D1 |

Reserved |

Set Reserved bits to 0. |

D0 |

RTS/CTS Flow Control |

Turns on Hardware Flow Control |

Termination Character |

|

Function: |

Contains the termination character used for termination detection. |

Type: |

unsigned character (usually a member of the ASCII data set) |

Data Range: |

0x00 to 0xFF |

Read/Write: |

R/W |

Initialized Value: |

0x03 |

Operational Settings: |

When using the Asynchronous or Mono/Bi-Synchronous modes, the receive data stream is monitored for the occurrence of the termination character. When this character is detected, the Rx COMPLETE / ETx RECEIVED bit is set in the Channel Status register, an interrupt is generated, if enabled. |

Async Only Configuration

In Async mode, additional configurations include setting the Data Configuration, Time Out Value, XOFF Character and XON Character registers.

Data Configuration |

|

Function: |

Channel data configuration. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table |

Read/Write: |

R/W |

Initialized Value: |

0x108 |

Operational Settings: |

Sets up the Serial channel configuration. |

Bit(s) |

Name |

Description |

D31:D15 |

Reserved |

Set Reserved bits to 0. |

D14:D12 |

Encoding |

The following sets the Data Encoding: (0:0:0) No Encoding (NRZ) |

D11:D10 |

Reserved |

Set Reserved bits to 0. |

D9:D8 |

Stop Bits |

The following sets the number of stop bits: (0:1) 1 Stop bit |

D7 |

Reserved |

Set Reserved bits to 0. |

D6:D4 |

Parity |

The following sets the Parity: (0:0:0) No Parity |

D3:D0 |

Number of Data Bits |

Actual number of data bits between 5 and 9. For Asynchronous Protocol only. |

Time Out Value |

|

Function: |

Determines the timeout period. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0 to 0xFFFF |

Read/Write: |

R/W |

Initialized Value: |

0x9C40 (1 second) |

Operational Settings: |

If there is no receive line activity for the configured period of time, a timeout is indicated in the Interrupt Status register, bit D10. LSB is 25µs. Modes Affected: Async. |

XON Character |

|

Function: |

Specifies the XON character for asynchronous flow control mode. |

Type: |

unsigned binary word 32-bits (usually a member of the ASCII data set) |

Data Range: |

0x00 to 0xFF |

Read/Write: |

R/W |

Initialized Value: |

0x11 |

Modes Affected: |

Async |

Operational Settings: |

When software flow control is enabled, this value is sent as the XON character. |

XOFF Character |

|

Function: |

Specifies the XOFF character for asynchronous software flow control mode. |

Type: |

unsigned binary word 32-bits (usually a member of the ASCII data set) |

Data Range: |

0x00 to 0xFF |

Read/Write: |

R/W |

Initialized Value: |

0x13 |

Modes Affected: |

Async |

Operational Settings: |

When software flow control is enabled, this value is sent as the XOFF character. |

Sync Only Configuration

In Sync mode, additional configurations include setting the Clock Mode, HDLC Rx Address/Sync Character and HDLC Tx Address/Sync Character registers.

Clock Mode |

|

Function: |

Configures clock for internal (driven) or external (received) transmit/receive clocks |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table. |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

Applicable only for Mono/bi-synchronous or HDLC as set by Protocol register. |

Default: |

0 |

Bit(s) |

Name |

Description |

D31:D8 |

Reserved |

Set Reserved bits to 0. |

D7 |

Invert Rx Clock |

Swap receive clock edge. |

D6 |

Invert Tx Clock |

Swap transmit clock edge. |

D5 |

Tristate Clock after Tx |

|

D4:D3 |

Reserved |

Set Reserved bits to 0. |

D2:D0 |

0x0: Internal |

Internal: Module always drives clock. |

HDLC Rx Address/Sync Character |

|

Function: |

Mode dependent for HDLC and Synchronous modes. See Operational Settings. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 to 0xFFFF |

Read/Write: |

R/W |

Initialized Value: |

0xA5 |

Operational Settings: |

HDLC Mode: This value is compared to the address of the received message and if it’s equal, the message is stored in the receive buffer. Mono/Bi-Synchronous Mode: this value is considered the “Sync Character” and is used for communication synchronization. The receiver searches incoming data for the Sync Character. Once found, communication is synchronized, and additional data is valid. When in Bi-Synchronous, low byte is sent before high byte. HDLC Rx Address/Sync Character Register |

HDLC |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

8-bit address when Address Length bit in Tx-Rx Configuration register is 0. |

|||||||

16-bit address when Address Length bit in Tx-Rx Configuration register is 1. |

|||||||||||||||

Mono-Synchronous |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

8-bit synchronization character |

|||||||

Bi-Synchronous |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Second 8-bit synchronization character |

First 8-bit synchronization character |

||||||||||||||

HDLC Tx Address/Sync Character |

|

Function: |

Mode dependent for HDLC and Synchronous modes. See Operational Settings. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 to 0xFFFF |

Read/Write: |

R/W |

Initialized Value: |

0xA5 |

Operational Settings: |

If using HDLC Mode: this value is compared to the address of the received message and if it’s equal, the message is stored in the receive buffer. Mono/Bi-Synchronous Mode: this value is considered the “Sync Character” and is used for communication synchronization. The receiver searches incoming data for the Sync Character. Once found, communication is synchronized, and additional data is valid. When in Bi-Synchronous, low byte is sent before high byte. |

Preamble |

|

Function: |

Determines the number of preambles and the preamble pattern sent during a preamble transmission. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 to 0xF0FF |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

In HDLC Mode: zero-bit insertion is disabled during preamble transmission. |

Bit(s) |

Name |

Description |

D31:D16 |

Reserved |

Set Reserved bits to 0. |

D15:D12 |

Number of Preambles |

The number of Preamble Patterns to be sent. |

D11:D8 |

Reserved |

Set Reserved bits to 0. |

D7:D0 |

Preamble Pattern |

Actual data byte to be sent. |

Control Register

The Channel Control register provides control of the serial channel.

Channel Control |

|

Function: |

Channel control configuration. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table. |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

Real time control of the Serial channel. |

Bit(s) |

Name |

Description |

D31:D19 |

Reserved |

Set Reserved bits to 0. |

D18 |

Enable Receiver |

|

D17 |

Tx Always (Async Only) |

Transmit data as soon as data is buffered. |

D16 |

Tx Initiate |

Transmit data in Tx buffer. (The data bit is cleared when all data from the Tx Buffer is transmitted) |

D15 |

Clear Tx FIFO |

Clear all data in the Tx FIFO. The data bit is self-clearing. |

D14 |

Clear Rx FIFO |

Clear all data in the Rx FIFO. The data bit is self-clearing. |

D13 |

Reset Channel FIFOs & UART |

Clear both FIFOs and reset channel. Bit is not self-clearing. |

D12:D11 |

Reserved |

Set Reserved bits to 0. |

D10 |

Set/Release Break |

0 = Break not set |

D9 |

Reserved |

Set Reserved bits to 0. |

D8 |

Tristate Transmit Line |

Tristate the transmit line after transmitting, for use with RS485 Multi-Drop mode. |

D7:D2 |

Reserved |

Set Reserved bits to 0. |

D1 |

GPO 2 |

General purpose output two control. |

D0 |

RTS/GPO* |

General purpose output one control. |

|

Note

|

*RTS/CTS as GPO when RTS/CTS Flow Control disabled. |

Serial Test Registers

The serial module provides the ability to run an initiated test (IBIT). Writing a 1 to the bit associated with the channel in the Test Enabled register.

|

Note

|

This register has the same effect as writing a 1 to the Initiate BIT bit of the Tx-Rx Configuration register for legacy applications. |

Test Enabled |

|

Function: |

Set the bit corresponding to the channel you want to run Initiated Built-In-Test. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0 to 0x0000 00FF |

Read/Write: |

R/W |

Initialized Value: |

0x0 |

Operational Settings: |

Set bit to 1 for channel to run an Initiated BIT test. Failures in the BIT test are reflected in the BIT Status registers for the corresponding channels that fail. In addition, an interrupt (if enabled in the BIT Interrupt Enable register) can be triggered when the BIT testing detects failures. Bit is self-clearing. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Background BIT Threshold Programming Registers

The Background BIT Threshold register provides the ability to specify the minimum time before the BIT fault is reported in the BIT Status registers. The Reset BIT register provides the ability to reset the BIT counter used in CBIT.

Background BIT Threshold |

|

Function: |

Sets background BIT Threshold value to use for all channels for BIT failure indication. This value is a scalar for the internal BIT counter, refer to Continuous Background Built-In Test. To filter out momentary or intermittent anomalies in background BIT errors, this value can be increased to allow the error to “come and go” before the BIT status is flagged. |

Data Range: |

0x1 to 0xFFFF |

Read/Write: |

R/W |

Initialized Value: |

5 |

Reset BIT |

|

Function: |

Resets the CBIT internal circuitry and count mechanism. Set the bit corresponding to the channel you want to clear. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0 to 0x0000 00FF |

Read/Write: |

W |

Initialized Value: |

0 |

Operational Settings: |

Set bit to 1 for channel to resets the CBIT mechanisms. Bit is self-clearing. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Module Common Registers

Refer to “Module Common Registers Module Manual” for the register descriptions.

Status and Interrupt Registers

The SC3 Module provides status registers for BIT, Channel, Summary and Channel FIFO.

BIT Status

There are four registers associated with the BIT Status: Dynamic Status, Latched Status, Interrupt Enable, and Set Edge/Level Interrupt.

BIT Status |

|

Function: |

Sets the corresponding bit associated with the channel’s BIT error. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt) |

Initialized Value: |

0 |

BIT Dynamic Status |

|||||||||||||||

BIT Latched Status |

|||||||||||||||

BIT Interrupt Enable |

|||||||||||||||

BIT Set Edge/Level Interrupt |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Power-on BIT (PBIT) Complete |

|

Function: |

Indication if Power-on BIT has completed. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 0000 to 0x0000 0001 |

Read/Write: |

R |

Initialized Value: |

0 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PBIT Complete |

Channel Status |

|

Function: |

Sets the corresponding bit associated with each event type. There are separate registers for each channel. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table. |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Set Edge/Level Interrupt) |

Initialized Value: |

0 |

Channel Dynamic Status |

|||

Channel Latched Status |

|||

Channel Interrupt Enable |

|||

Channel Set Edge/Level Interrupt |

|||

Bit(s) |

Name |

Configurable |

Description |

D31 |

Channel Configured |

No |

Module is configured and ready to operate. |

D30 |

Built-in-Self Test Passed |

No |

Indicates the status of the last ran IBIT test. |

D29:D18 |

Reserved |

No |

Set Reserved bits to 0. |

D17 |

Gap Timeout Occurred |

Yes |

Rx FIFO has data in it, but there hasn’t been activity on the bus in 3-byte times. |

D16 |

GPI 2 |

No |

Binary value of general-purpose input 2. |

D15 |

CTS/GPI1 |

No |

Binary value of general-purpose input 1 or CTS. |

D14 |

CTS Low Detect (fall) |

No |

CTS falling edge detected. |

D13 |

CTS High Detect (rise) |

No |

CTS rising edge detected. |

D12 |

Reserved |

No |

Set Reserved bits to 0. |

D11 |

Break/Abort |

No |

Break recognized. |

D10 |

Timeout Occurred |

Yes |

No receive line activity within timeout value. |

D9 |

Tx Complete |

No |

While transmitting, Tx FIFO count reaches zero. |

D8 |

Tx FIFO Almost Empty |

Yes |

Transmit FIFO Almost Empty Threshold reached. |

D7 |

Low Watermark Reached |

Yes |

Rx Buffer Low Watermark Threshold reached. |

D6 |

High Watermark Reached |

Yes |

Rx Buffer High Watermark Threshold reached. |

D5 |

Rx Overrun |

No |

Data was received while the Rx FIFO was full. |

D4 |

Rx Data Available |

No |

Receive FIFO count is greater than zero. |

D3 |

Rx Complete/ET x Received |

No |

Async: Termination character received (Only if termination detection is turned on.) |

D2 |

CRC Error (Sync & HDLC) |

No |

CRC calculation did not match. |

D1 |

Rx FIFO Almost Full |

Yes |

Receive FIFO Almost Full Threshold |

D0 |

Parity Error |

No |

Parity bit did not match. |

|

Note

|

For the Latched Channel Status register, the interrupts are cleared when a 1 is written to the specific bit. |

Channel FIFO Status |

|

Function: |

Describes current FIFO Status. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See Table |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

See Rx Almost Full, Tx Almost Empty, Rx High Watermark and Rx Low Watermark specific registers for function description and programming. |

Bit(s) |

Name |

Configurable? |

Description |

D5 |

Tx FIFO Full |

No |

Tx FIFO has reached maximum buffer size. |

D4 |

Rx FIFO Empty |

No |

Rx FIFO count is zero. |

D3 |

Low Watermark Reached |

Yes |

Rx Buffer Low Watermark Threshold reached. |

D2 |

High Watermark Reached |

Yes |

Rx Buffer High Watermark Threshold reached. |

D1 |

Tx FIFO Almost Empty |

Yes |

Tx FIFO Almost Empty Threshold reached. |

D0 |

Rx FIFO Almost Full |

Yes |

Rx FIFO Almost Full Threshold reached |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

D |

D |

D |

D |

D |

Summary Status |

|

Function: |

Sets the corresponding bit associated with the channel that has data available to receive in its Receive FIFO Buffer. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Set Edge/Level Interrupt) |

Initialized Value: |

0 |

Summary Dynamic Status |

|||||||||||||||

Summary Latched Status |

|||||||||||||||

Summary Interrupt Enable |

|||||||||||||||

Summary Set Edge/Level Interrupt |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Interrupt Vector and Steering

When interrupts are enabled, the interrupt vector associated with the specific interrupt can be programmed (typically with a unique number/identifier) such that it can be utilized in the Interrupt Service Routine (ISR) to identify the type of interrupt. When an interrupt occurs, the contents of the Interrupt Vector registers is reported as part of the interrupt mechanism.

In addition to specifying the interrupt vector, the interrupt can be directed (“steered”) to the native bus or to the application running on the onboard ARM processor.

|

Note

|

The Interrupt Vector and Interrupt Steering registers are mapped to the Motherboard Common Memory and these registers are associated with the Module Slot position (refer to Function Register Map). |

Interrupt Vector |

|

Function: |

Set an identifier for the interrupt. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, this value is reported as part of the interrupt mechanism. |

Interrupt Steering |

|

Function: |

Sets where to direct the interrupt. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

See table |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, the interrupt is sent as specified: |

Direct Interrupt to VME |

1 |

Direct Interrupt to ARM Processor (via SerDes) |

2 |

Direct Interrupt to PCIe Bus |

5 |

Direct Interrupt to cPCI Bus |

6 |

FUNCTION REGISTER MAP

KEY

Incoming Data |

Outgoing Data |

Configuration/Control |

Status |

| RECEIVE REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x1004 |

Receive FIFO Buffer Ch 1 |

R |

0x100C |

Receive FIFO Buffer Word Count Ch 1 |

R |

0x1084 |

Receive FIFO Buffer Ch 2 |

R |

0x108C |

Receive FIFO Buffer Word Count Ch 2 |

R |

0x1104 |

Receive FIFO Buffer Ch 3 |

R |

0x110C |

Receive FIFO Buffer Word Count Ch 3 |

R |

0x1184 |

Receive FIFO Buffer Ch 4 |

R |

0x118C |

Receive FIFO Buffer Word Count Ch 4 |

R |

0x1204 |

Receive FIFO Buffer Ch 5 |

R |

0x120C |

Receive FIFO Buffer Word Count Ch 5 |

R |

0x1284 |

Receive FIFO Buffer Ch 6 |

R |

0x128C |

Receive FIFO Buffer Word Count Ch 6 |

R |

0x1304 |

Receive FIFO Buffer Ch 7 |

R |

0x130C |

Receive FIFO Buffer Word Count Ch 7 |

R |

0x1384 |

Receive FIFO Buffer Ch 8 |

R |

0x138C |

Receive FIFO Buffer Word Count Ch 8 |

R |

0x1034 |

Receive FIFO Buffer Almost Full Ch 1 |

R/W |

0x1038 |

Receive FIFO Buffer High Watermark Ch 1 |

R/W |

0x10B4 |

Receive FIFO Buffer Almost Full Ch 2 |

R/W |

0x10B8 |

Receive FIFO Buffer High Watermark Ch 2 |

R/W |

0x1134 |

Receive FIFO Buffer Almost Full Ch 3 |

R/W |

0x1138 |

Receive FIFO Buffer High Watermark Ch 3 |

R/W |

0x11B4 |

Receive FIFO Buffer Almost Full Ch 4 |

R/W |

0x11B8 |

Receive FIFO Buffer High Watermark Ch 4 |

R/W |

0x1234 |

Receive FIFO Buffer Almost Full Ch 5 |

R/W |

0x1238 |

Receive FIFO Buffer High Watermark Ch 5 |

R/W |

0x12B4 |

Receive FIFO Buffer Almost Full Ch 6 |

R/W |

0x12B8 |

Receive FIFO Buffer High Watermark Ch 6 |

R/W |

0x1334 |

Receive FIFO Buffer Almost Full Ch 7 |

R/W |

0x1338 |

Receive FIFO Buffer High Watermark Ch 7 |

R/W |

0x13B4 |

Receive FIFO Buffer Almost Full Ch 8 |

R/W |

0x13B8 |

Receive FIFO Buffer High Watermark Ch 8 |

R/W |

0x103C |

Receive FIFO Buffer Low Watermark Ch 1 |

R/W |

|||

0x10BC |

Receive FIFO Buffer Low Watermark Ch 2 |

R/W |

|||

0x113C |

Receive FIFO Buffer Low Watermark Ch 3 |

R/W |

|||

0x11BC |

Receive FIFO Buffer Low Watermark Ch 4 |

R/W |

|||

0x123C |

Receive FIFO Buffer Low Watermark Ch 5 |

R/W |

|||

0x12BC |

Receive FIFO Buffer Low Watermark Ch 6 |

R/W |

|||

0x133C |

Receive FIFO Buffer Low Watermark Ch 7 |

R/W |

|||

0x13BC |

Receive FIFO Buffer Low Watermark Ch 8 |

R/W |

|||

| TRANSMIT REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x1000 |

Transmit FIFO Buffer Ch 1 |

W |

0x1008 |

Transmit FIFO Buffer Word Count Ch 1 |

R |

0x1080 |

Transmit FIFO Buffer Ch 2 |

W |

0x1088 |

Transmit FIFO Buffer Word Count Ch 2 |

R |

0x1100 |

Transmit FIFO Buffer Ch 3 |

W |

0x1108 |

Transmit FIFO Buffer Word Count Ch 3 |

R |

0x1180 |

Transmit FIFO Buffer Ch 4 |

W |

0x1188 |

Transmit FIFO Buffer Word Count Ch 4 |

R |

0x1200 |

Transmit FIFO Buffer Ch 5 |

W |

0x1208 |

Transmit FIFO Buffer Word Count Ch 5 |

R |

0x1280 |

Transmit FIFO Buffer Ch 6 |

W |

0x1288 |

Transmit FIFO Buffer Word Count Ch 6 |

R |

0x1300 |

Transmit FIFO Buffer Ch 7 |

W |

0x1308 |

Transmit FIFO Buffer Word Count Ch 7 |

R |

0x1380 |

Transmit FIFO Buffer Ch 8 |

W |

0x1388 |

Transmit FIFO Buffer Word Count Ch 8 |

R |

0x1030 |

Transmit FIFO Buffer Almost Empty Ch 1 |

R/W |

|||

0x10B0 |

Transmit FIFO Buffer Almost Empty Ch 2 |

R/W |

|||

0x1130 |

Transmit FIFO Buffer Almost Empty Ch 3 |

R/W |

|||

0x11B0 |

Transmit FIFO Buffer Almost Empty Ch 4 |

R/W |

|||

0x1230 |

Transmit FIFO Buffer Almost Empty Ch 5 |

R/W |

|||

0x12B0 |

Transmit FIFO Buffer Almost Empty Ch 6 |

R/W |

|||

0x1330 |

Transmit FIFO Buffer Almost Empty Ch 7 |

R/W |

|||

0x13B0 |

Transmit FIFO Buffer Almost Empty Ch 8 |

R/W |

|||

| CONFIGURATION REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x1018 |

Interface Levels Ch 1 |

R/W |

0x1028 |

Baud Rate Ch 1 |

R/W |

0x1098 |

Interface Levels Ch 2 |

R/W |

0x10A8 |

Baud Rate Ch 2 |

R/W |

0x1118 |

Interface Levels Ch 3 |

R/W |

0x1128 |

Baud Rate Ch 3 |

R/W |

0x1198 |

Interface Levels Ch 4 |

R/W |

0x11A8 |

Baud Rate Ch 4 |

R/W |

0x1218 |

Interface Levels Ch 5 |

R/W |

0x1228 |

Baud Rate Ch 5 |

R/W |

0x1298 |

Interface Levels Ch 6 |

R/W |

0x12A8 |

Baud Rate Ch 6 |

R/W |

0x1318 |

Interface Levels Ch 7 |

R/W |

0x1328 |

Baud Rate Ch 7 |

R/W |

0x1398 |

Interface Levels Ch 8 |

R/W |

0x13A8 |

Baud Rate Ch 8 |

R/W |

0x1010 |

Protocol Ch 1 |

R/W |

0x101C |

Tx-Rx Configuration Ch 1 |

R/W |

0x1090 |

Protocol Ch 2 |

R/W |

0x109C |

Tx-Rx Configuration Ch 2 |

R/W |

0x1110 |

Protocol Ch 3 |

R/W |

0x111C |

Tx-Rx Configuration Ch 3 |

R/W |

0x1190 |

Protocol Ch 4 |

R/W |

0x119C |

Tx-Rx Configuration Ch 4 |

R/W |

0x1210 |

Protocol Ch 5 |

R/W |

0x121C |

Tx-Rx Configuration Ch 5 |

R/W |

0x1290 |

Protocol Ch 6 |

R/W |

0x129C |

Tx-Rx Configuration Ch 6 |

R/W |

0x1310 |

Protocol Ch 7 |

R/W |

0x131C |

Tx-Rx Configuration Ch 7 |

R/W |

0x1390 |

Protocol Ch 8 |

R/W |

0x139C |

Tx-Rx Configuration Ch 8 |

R/W |

0x1050 |

Termination Character Ch 1 |

R/W |

|||

0x10D0 |

Termination Character Ch 2 |

R/W |

|||

0x1150 |

Termination Character Ch 3 |

R/W |

|||

0x11D0 |

Termination Character Ch 4 |

R/W |

|||

0x1250 |

Termination Character Ch 5 |

R/W |

|||

0x12D0 |

Termination Character Ch 6 |

R/W |

|||

0x1350 |

Termination Character Ch 7 |

R/W |

|||

0x13D0 |

Termination Character Ch 8 |

R/W |

|||

| ASYNC ONLY CONFIGURATION REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

0x1024 |

Data Configuration Ch 1 |

R/W |

0x1054 |

Time Out Value Ch 1 |

R/W |

0x10A4 |

Data Configuration Ch 2 |

R/W |

0x10D4 |

Time Out Value Ch 2 |

R/W |

0x1124 |

Data Configuration Ch 3 |

R/W |

0x1154 |

Time Out Value Ch 3 |

R/W |

0x11A4 |

Data Configuration Ch 4 |

R/W |

0x11D4 |

Time Out Value Ch 4 |

R/W |

0x1224 |

Data Configuration Ch 5 |

R/W |

0x1254 |

Time Out Value Ch 5 |

R/W |

0x12A4 |

Data Configuration Ch 6 |

R/W |

0x12D4 |

Time Out Value Ch 6 |

R/W |

0x1324 |

Data Configuration Ch 7 |

R/W |

0x1354 |

Time Out Value Ch 7 |

R/W |

0x13A4 |

Data Configuration Ch 8 |

R/W |

0x13D4 |

Time Out Value Ch 8 |

R/W |

0x1048 |

XON Character Ch 1 |

R/W |

0x104C |

XOFF Character Ch 1 |

R/W |

0x10C8 |

XON Character Ch 2 |

R/W |

0x10CC |

XOFF Character Ch 2 |

R/W |

0x1148 |

XON Character Ch 3 |

R/W |

0x114C |

XOFF Character Ch 3 |

R/W |

0x11C8 |

XON Character Ch 4 |

R/W |

0x11CC |

XOFF Character Ch 4 |

R/W |

0x1248 |

XON Character Ch 5 |

R/W |

0x124C |

XOFF Character Ch 5 |

R/W |

0x12C8 |

XON Character Ch 6 |

R/W |

0x12CC |

XOFF Character Ch 6 |

R/W |

0x1348 |

XON Character Ch 7 |

R/W |

0x134C |

XOFF Character Ch 7 |

R/W |

0x13C8 |

XON Character Ch 8 |

R/W |

0x13CC |

XOFF Character Ch 8 |

R/W |

| SYNC ONLY CONFIGURATION REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

0x1014 |

Clock Mode Ch 1 |

R/W |

0x1040 |

HDLC Rx Address/Sync Character Ch 1 |

R/W |

0x1094 |

Clock Mode Ch 2 |

R/W |

0x10C0 |

HDLC Rx Address/Sync Character Ch 2 |

R/W |

0x1114 |

Clock Mode Ch 3 |

R/W |

0x1140 |

HDLC Rx Address/Sync Character Ch 3 |

R/W |

0x1194 |

Clock Mode Ch 4 |

R/W |

0x11C0 |

HDLC Rx Address/Sync Character Ch 4 |

R/W |

0x1044 |

HDLC Tx Address/Sync Character Ch 1 |

R/W |

0x102C |

Preamble Ch 1 |

R/W |

0x10C4 |

HDLC Tx Address/Sync Character Ch 2 |

R/W |

0x10AC |

Preamble Ch 2 |

R/W |

0x1144 |

HDLC Tx Address/Sync Character Ch 3 |

R/W |

0x112C |

Preamble Ch 3 |

R/W |

0x11C4 |

HDLC Tx Address/Sync Character Ch 4 |

R/W |

0x11AC |

Preamble Ch 4 |

R/W |

| CONTROL REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x1020 |

Channel Control Ch 1 |

R/W |

|||

0x10A0 |

Channel Control Ch 2 |

R/W |

|||

0x1120 |

Channel Control Ch 3 |

R/W |

|||

0x11A0 |

Channel Control Ch 4 |

R/W |

|||

0x1220 |

Channel Control Ch 5 |

R/W |

|||

0x12A0 |

Channel Control Ch 6 |

R/W |

|||

0x1320 |

Channel Control Ch 7 |

R/W |

|||

0x13A0 |

Channel Control Ch 8 |

R/W |

|||

| MODULE COMMON REGISTERS | |||||

|---|---|---|---|---|---|

Refer to “Module Common Registers Module Manual” for the Module Common Registers Function Register Map. |

| STATUS REGISTERS* | |||||

|---|---|---|---|---|---|

*When an event is detected, the bit associated with the event is set in this register and will remain set until the user clears the event bit. Clearing the bit requires writing a 1 back to the specific bit that was set when read (i.e., write-1-to-clear, writing a “1” to a bit set to “1” will set the bit to “0). |

|||||

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x02B0 |

Channel Status Enabled |

R/W |

|||

0x0800 |

BIT Dynamic Status |

R |

|||

0x0804 |

BIT Latched Status* |

R/W |

|||

0x0808 |

BIT Interrupt Enable |

R/W |

|||

0x080C |

BIT Set Edge/Level Interrupt |

R/W |

|||

0x02A8 |

Test Enabled |

R/W |

0x02AC |

Power-on BIT Complete++ |

R/W |

NOTE: ++After power-on, Power-on BIT Complete should be checked before reading the BIT Latched Status. |

|||||

0x02B8 |

Background BIT Threshold |

R/W |

0x02BC |

Reset BIT |

W |

Channel 1 Status |

Channel 2 Status |

||||

0x0810 |

Dynamic Status |

R |

0x0820 |

Dynamic Status |

R |

0x0814 |

Latched Status* |

R/W |

0x0824 |

Latched Status* |

R/W |

0x0818 |

Interrupt Enable |

R/W |

0x0828 |

Interrupt Enable |

R/W |

0x081C |

Set Edge/Level Interrupt |

R/W |

0x082C |

Set Edge/Level Interrupt |

R/W |

Channel 3 Status |

Channel 4 Status |

||||

0x0830 |

Dynamic Status |

R |

0x0840 |

Dynamic Status |

R |

0x0834 |

Latched Status* |

R/W |

0x0844 |

Latched Status* |

R/W |

0x0838 |

Interrupt Enable |

R/W |

0x0848 |

Interrupt Enable |

R/W |

0x083C |

Set Edge/Level Interrupt |

R/W |

0x084C |

Set Edge/Level Interrupt |

R/W |

Channel 5 Status |

Channel 6 Status |

||||

0x0850 |

Dynamic Status |

R |

0x0860 |

Dynamic Status |

R |

0x0854 |

Latched Status* |

R/W |

0x0864 |

Latched Status* |

R/W |

0x0858 |

Interrupt Enable |

R/W |

0x0868 |

Interrupt Enable |

R/W |

0x085C |

Set Edge/Level Interrupt |

R/W |

0x086C |

Set Edge/Level Interrupt |

R/W |

Channel 7 Status |

Channel 8 Status |

||||

0x0870 |

Dynamic Status |

R |

0x0880 |

Dynamic Status |

R |

0x0874 |

Latched Status* |

R/W |

0x0884 |

Latched Status* |

R/W |

0x0878 |

Interrupt Enable |

R/W |

0x0888 |

Interrupt Enable |

R/W |

0x087C |

Set Edge/Level Interrupt |

R/W |

0x088C |

Set Edge/Level Interrupt |

R/W |

FIFO Status |

Summary Status |

||||

0x1058 |

Channel 1 FIFO Status |

R |

0x09A0 |

Dynamic Status |

R |

0x10D8 |

Channel 2 FIFO Status |

R/W |

0x09A4 |

Latched Status* |

R/W |

0x1158 |

Channel 3 FIFO Status |

R/W |

0x09A8 |

Interrupt Enable |

R/W |

0x11D8 |

Channel 4 FIFO Status |

R/W |

0x09AC |

Set Edge/Level Interrupt |

R/W |

0x1258 |

Channel 5 FIFO Status |

R/W |

|||

0x12D8 |

Channel 6 FIFO Status |

R/W |

|||

0x1358 |

Channel 7 FIFO Status |

R/W |

|||

0x13D8 |

Channel 8 FIFO Status |

R/W |

|||

| INTERRUPT REGISTERS | |||||

|---|---|---|---|---|---|

The Interrupt Vector and Interrupt Steering registers are located on the Motherboard Memory Space and do not require any Module Address Offsets. These registers are accessed using the absolute addresses listed in the table below. |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x0500 |

Module 1 Interrupt Vector 1 - BIT |

R/W |

0x0600 |

Module 1 Interrupt Steering 1 - BIT |

R/W |

0x0504 |

Module 1 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0604 |

Module 1 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0508 |

Module 1 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0608 |

Module 1 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x050C |

Module 1 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x060C |

Module 1 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0510 |

Module 1 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0610 |

Module 1 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0514 |

Module 1 Interrupt Vector 6 - Channel Status Ch 5 |

R/W |

0x0614 |

Module 1 Interrupt Steering 6 - Channel Status Ch 5 |

R/W |

0x0518 |

Module 1 Interrupt Vector 7 - Channel Status Ch 6 |

R/W |

0x0618 |

Module 1 Interrupt Steering 7 - Channel Status Ch 6 |

R/W |

0x051C |

Module 1 Interrupt Vector 8 - Channel Status Ch 7 |

R/W |

0x061C |

Module 1 Interrupt Steering 8 - Channel Status Ch 7 |

R/W |

0x0520 |

Module 1 Interrupt Vector 9 - Channel Status Ch 8 |

R/W |

0x0620 |

Module 1 Interrupt Steering 9 - Channel Status Ch 8 |

R/W |

0x0524 to 0x0564 |

Module 1 Interrupt Vector 10 to 26 - Reserved |

R/W |

0x0624 to 0x0664 |

Module 1 Interrupt Steering 10 to 26 - Reserved |

R/W |

0x0568 |

Module 1 Interrupt Vector 27 - Summary Status |

R/W |

0x0668 |

Module 1 Interrupt Steering 27 - Summary Status |

R/W |

0x056C to 0x057C |

Module 1 Interrupt Vector 28 to 32 - Reserved |

R/W |

0x066C to 0x067C |

Module 1 Interrupt Steering 28 to 32 - Reserved |

R/W |

0x0700 |

Module 2 Interrupt Vector 1 - BIT |

R/W |

0x0800 |

Module 2 Interrupt Steering 1 - BIT |

R/W |

0x0704 |

Module 2 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0804 |

Module 2 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0708 |

Module 2 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0808 |

Module 2 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x070C |

Module 2 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x080C |

Module 2 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0710 |

Module 2 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0810 |

Module 2 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0714 |

Module 2 Interrupt Vector 6 - Channel Status Ch 5 |

R/W |

0x0814 |

Module 2 Interrupt Steering 6 - Channel Status Ch 5 |

R/W |

0x0718 |

Module 2 Interrupt Vector 7 - Channel Status Ch 6 |

R/W |

0x0818 |

Module 2 Interrupt Steering 7 - Channel Status Ch 6 |

R/W |

0x071C |

Module 2 Interrupt Vector 8 - Channel Status Ch 7 |

R/W |

0x081C |

Module 2 Interrupt Steering 8 - Channel Status Ch 7 |

R/W |

0x0720 |

Module 2 Interrupt Vector 9 - Channel Status Ch 8 |

R/W |

0x0820 |

Module 2 Interrupt Steering 9 - Channel Status Ch 8 |

R/W |

0x0724 to 0x0764 |

Module 2 Interrupt Vector 10 to 26 - Reserved |

R/W |

0x0824 to 0x0864 |

Module 2 Interrupt Steering 10 to 26 - Reserved |

R/W |

0x0768 |

Module 2 Interrupt Vector 27 - Summary Status |

R/W |

0x0868 |

Module 2 Interrupt Steering 27 - Summary Status |

R/W |

0x076C to 0x077C |

Module 2 Interrupt Vector 28 to 32 - Reserved |

R/W |

0x086C to 0x087C |

Module 2 Interrupt Steering 28 to 32 - Reserved |

R/W |

0x0900 |

Module 3 Interrupt Vector 1 - BIT |

R/W |

0x0A00 |

Module 3 Interrupt Steering 1 - BIT |

R/W |

0x0904 |

Module 3 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0A04 |

Module 3 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0908 |

Module 3 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0A08 |

Module 3 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x090C |

Module 3 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x0A0C |

Module 3 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0910 |

Module 3 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0A10 |

Module 3 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0914 |

Module 3 Interrupt Vector 6 - Channel Status Ch 5 |

R/W |

0x0A14 |

Module 3 Interrupt Steering 6 - Channel Status Ch 5 |

R/W |

0x0918 |

Module 3 Interrupt Vector 7 - Channel Status Ch 6 |

R/W |

0x0A18 |

Module 3 Interrupt Steering 7 - Channel Status Ch 6 |

R/W |

0x091C |

Module 3 Interrupt Vector 8 - Channel Status Ch 7 |

R/W |

0x0A1C |

Module 3 Interrupt Steering 8 - Channel Status Ch 7 |

R/W |

0x0920 |

Module 3 Interrupt Vector 9 - Channel Status Ch 8 |

R/W |