NIU3E Manual

Edit this on GitLab

INTRODUCTION

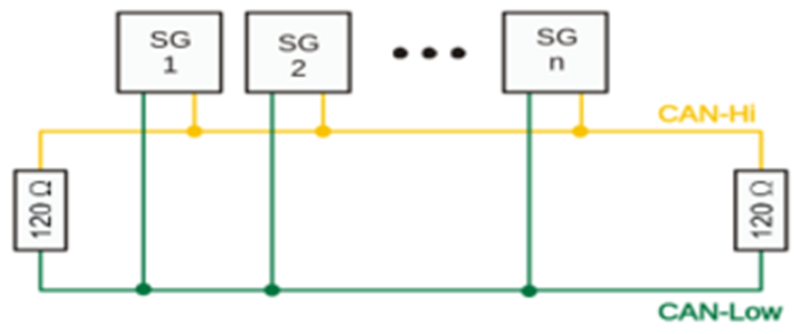

This manual provides information about the North Atlantic Industries, Inc. (NAI) NIU3E System. The NIU3E is a “Nano Interface Unit” self contained multi-port Ethernet Switch and Multifunction I/O System preconfigured with a choice of Ethernet Switch Module(s) (e.g. ES2; Managed Ethernet Switch Module w/ 16x 10/100/1000Base-T and 4x 10Gb 850 nm Fiber Optic ports), 24-CH programmable Discrete I/O, 8-CH ARINC 429/575, 4-CH CAN bus and 2-CH MIL-STD-1553 functions. The NIU3E can also be configured with up to one additional smart Configurable Open Systems Architecture™ (COSA®) function modules. The NIU3E boasts a dual ARM ®Cortex®-A53 processor for customer application and I/O and communications management.

SOFTWARE SUPPORT

Edit this on GitLab

The ENAIBL Software Support Kit (SSK) is supplied with all system platform based board level products. This platform’s SSK contents include html format help documentation which defines board specific library functions and their respective parameter requirements. A board specific library and its source code is provided (module level ‘C’ and header files) to facilitate function implementation independent of user operating system (O/S). Portability files are provided to identify Board Support Package (BSP) dependent functions and help port code to other common system BSPs. With the use of the provided help documentation, these libraries are easily ported to any 32-bit O/S such as RTOS or Linux.

The latest version of a board specific SSK can be downloaded from our website www.naii.com in the software downloads section. A Quick-Start Software Manual is also available for download where the SSK contents are detailed, Quick-Start Instructions provided and GUI applications are described therein. For other operating system support, contact factory.

CONVENTIONS USED IN THIS MANUAL

|

Note

|

An operating procedure, practice, or condition, etc., that is essential to emphasize. |

All numbers are expressed in decimal format unless otherwise noted.

Website: http://www.naii.com/

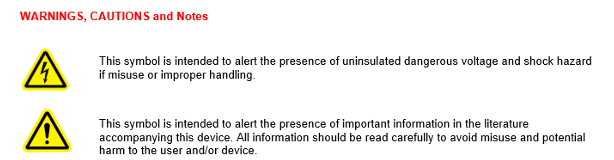

GENERAL SAFETY NOTICES

The following general safety notices supplement the specific warnings and cautions appearing elsewhere in the manual. They are recommended precautions that must be understood and applied during operation and maintenance of the instrument covered herein.

Death or serious injury may result if personnel fail to observe safety precautions. Dependent on configuration, some modules (e.g. Synchro / Resolver or AC signal sources) can generate output signals with high voltages. Be careful not to contact high-voltage connections when installing, operating, or maintaining this instrument.

The NIU3E is delivered as a standalone system with no accessible or serviceable parts.

Repair

DO NOT ATTEMPT REPAIR. Under no circumstances should repair of this instrument be attempted. All repairs to the chassis must be accomplished at the factory.

Input Power Always On

|

Note

|

The design of the model NIU3E is such that DC input power is continuously supplied to internal circuits when connected to a main power source. To disconnect the NIU3E from external power, the external power source should first be de-energized. The power input cable can then be disconnected. |

SYSTEM SPECIFICATIONS AND DETAILS

Introduction

The Nano Interface Unit (NIU3E) is a second-generation, integrated, compact, “nano-sized” subsystem with unprecedented I/O capability configurations and fitted with a managed multiport Ethernet switch. The NIU3E connects to existing platform Ethernet networks, making data available to any system on the network. Additionally, the NIU3E is delivered with ARM® Cortex®-A53 access support for standalone or other processor related capability.

The NIU3E easily adds sensor data acquisition and distribution and communication interfaces to mission computers without expensive chassis and backplane redesign. It has been designed with rugged embedded industrial, military and aerospace applications in mind.

Leveraging NAI’s field-proven, unique modular architecture, the NIU3E supports a wide selection of different Intelligent I/O, motion simulation/measurement and communications functions such as:

A/D Converter |

D/A Converter |

I/O TTL/CMOS |

RTD |

I/O Discrete |

I/O Differential Transceiver |

Synchro/Resolver LVDT/RVDT Measurement |

Synchro/Resolver LVDT/RVDT Simulation |

Strain Gage |

Encoder |

Dual-Channel Dual Redundant BC/RT/MT MIL-STD-1553 |

High-Speed Sync/Async RS232/422/423/485 |

ARINC 429/575 |

CANBus |

I/O Relay |

AC Reference |

Ethernet Switch |

SSD/Flash |

This approach provides unprecedented flexibility for supporting existing or new applications where there are specific interfacing requirements.

Significant application benefits include:

-

Independent (pre-processed) I/O functionality targeted to specific data acquisition/control areas

-

Additional capabilities, technology insertion and sensor interfacing to existing fielded applications

-

Minimal integration risk based on current field-proven, deployed technologies

-

Only ~ 7.2” x 7.1” x 3.2” @ ~7.7 lbs. (3.49 kg) conduction/convection cooled

-

16x Ethernet Switch Ports

-

10/100/1000Base-T (GbE) (default)

-

-

4x 10 Gb Fiber Optic 850 nm (optional)

Objectives

This manual provides the user with basic hardware implementation and information regarding the operation and interface of the NIU3E. Each NIU3E is fitted with one Ethernet Switch module, one function module, four embedded module functions, dual-core processor and an integrated motherboard, power supply unit (PSU) and interface connectors.

ON BOARD RESOURCES

Memory

DDR4 SDRAM

The NIU3E provides a total of 8 GB of ECC DDR4 memory. This memory is organized as 4 1Gb x 16 MT40A1G16RC devices (parts may vary), with a fifth device providing storage for ECC data. The Ultrascale+™ has an on chip 64-bit DDR4 memory controller. The controller has full ECC error-correction support, with the ability to detect multi-bit errors and correct single-bit errors within a nibble. Please consult the Micron data sheet for DDR4 device specific details.

NOR Flash

Connected through the local bus, the NIU3E supports 2 x 2 gigabytes of flash. The Flash consists of a stacked (four 512Mb die) Micron® Flash MT25QL02GCBB8E12-0SIT device. Flash features a high-speed SPI-compatible bus interface that utilizes dual QSPI via a two-input logic gate to increase I/O throughput rates four times for each device. The NOR Flash has an erase capacity of 100,000 cycles per sector and typical data retention of 20 years.

FRAM

The FM24CL64B is a 64-kilobit nonvolatile memory employing an advanced ferroelectric process. The ferroelectric random-access memory or FRAM is nonvolatile and performs reads and writes like a RAM. It provides reliable data retention for 38 years. The NIU3E FRAM 64K bits are organized as 8,192 x 8 bits random access memory, connected to the Ultrascale+™ CPU through the I2C controller.

SATA

The Ultrascale+™ CPU is directly connected to an onboard Solid-State Drive (SSD). The SSD contains a single level cell NAND Flash together with a controller in a single Multi-Chip package. The Multi-Chip packaged device is soldered directly to the printed circuit board for reliable electrical and mechanical connection.

The SSD has an internal write protect signal SATA_WP. The SATA_WP signal must be connected or switched to ground to enable any write to the SSD. The SATA_WP signal is pulled up on card by a 4.7 KΩ resistor to the internal 3.3 V supply.

The onboard SATA drive conforms to the follow specifications:

-

Complies with Serial ATA 2.5 Specification

-

Supports speeds: 1.5 Gbps (first-generation SATA), 3 Gbps (second-generation SATA and eSATA)

-

Supports advanced technology attachment packet interface (ATAPI) devices

-

Contains high-speed descriptor-based DMA controller

-

Supports native command queuing (NCQ) commands

-

The standard ordering code for the NIU3E includes a 32GB SSD drive. Larger devices are available; please consult the factory for availability

Peripheral I/O

Ethernet

The NIU3E supports two 10/100/1000Base-TX Ethernet or two 1000Base-KX Ethernet connections using two Marvell Alaska 88E1512 Ethernet PHY devices and the Xilinx Gigabit Ethernet MACs. The PHY-to-MAC interface employs a Reduced Gigabit Media Independent Interface (RGIII) connection using four data lines at 250 Mbps each for a connection speed of 1 Gbps. The NIU3E contains internal magnetics and can directly drive copper CAT5e or CAT6 twisted pairs.

The NIU3E Ethernet ports support:

-

Detection and correction of pair swaps (MDI crossover), and pair polarity

-

MAC-side and line-side loopback

-

Auto–negotiation

Ethernet Port 1 can be routed as 10/100/1000Base-TX as a build option.

Ethernet Port 2 can be routed as 10/100/1000Base-TX as a build option.

I/O pin outs can be found in the Pinout Details section of this document.

USB

The NIU3E supports one USB 2.0 port. Contact factory for availability.

USB0 is available on the NIU3E, on connector J5. The USB port can operate as a standalone host.

-

Compatible with USB specification, Rev. 2.0

-

Supports high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations

-

Supports operation as a standalone USB host controller

-

Supports USB root hub with one downstream-facing port

-

Enhanced host controller interface (EHCI)-compatible

-

One controller supports operation as a standalone USB device

-

Supports one upstream-facing port

-

Supports six programmable USB endpoints

I2C

I2C is a two-wire, bidirectional single ended serial bus that provides an efficient method of exchanging data between a master and slave device. The NIU3E has one I2C device for communicating with onboard devices, as shown in the table below.

Assignment |

I2C addresses |

Device |

Onboard Devices |

0x50 |

Security Manager |

Onboard Devices |

0x56 |

EEPROM |

Onboard Devices |

0x53 |

FRAM |

Tamper Detect Interface and Action Circuit

NAI is developing an optional Tamper Detect Interface and Action Circuit for improved Security/Cybersecurity requirements. This circuit will offer FIPS 140-3 Level 3 Design Support, Crypto-Key Storage (with Battery-Backed RAM), Secure Boot and Anti-Tamper/Tamper Detect & Sanitize functions. For further information, please contact NAI.

Software Libraries/Associated Documents

NIU3E BSP Processor Module Library

The NIU3E Processor library package provides function interfaces to the on-module functionality. This package contains Help documentation (in html format) that explains all the functions available in the library. The package also contains the source code (*.h, *.c) files as well as the files needed to build the library using any of the supported operating systems. Example programs are also provided to demonstrate the usage of the libraries in typical applications of the module.

SPECIFICATIONS

The NIU3E is designed to meet the following general specifications.

General

Ethernet Data Transfer: |

Data transfers within 1 ms (typical) |

Input Voltage: |

18 to 36 VDC (28 VDC nominal) |

Power (Base unit): |

0.675 A (~19 W) @ 28 V VDC nominal plus module(s) power (see specific module(s) specifications) I/O Signal GND reference is isolated from main power source return and chassis. |

Power/Heat Dissipation: |

~25 watts (maximum) when properly mounted, with the thermal transfer mounting surface maintained at a temperature not to exceed 71°C. Note: The total NIU3E power dissipation is dependent on the configuration of the modules fitted in the NIU3E. |

Temperature, Operating: |

-40°C to 71°C (conduction cooled - measured at primary thermal interface) |

Temperature, Storage: |

-55°C to 105°C |

Size: |

Depth: ~7.1” (180.3 mm) Height: ~3.2” (81.3 mm) Width: ~7.2” (182.9 mm) |

Weight: |

The weight of an NIU3E system is dependent on the configuration. The approximate weight of the NIU3E is based on the selection of the functional module(s). The approximate weight of a typical fully configured NIU3E (model #) is ~7.7 lbs. (3.49 kg). |

Environmental

No. |

Description |

Procedure (for ref.) |

Cycles (for ref.) |

Table (for ref.) |

Fig. (for ref.) |

Comments |

514 |

Random Vibe |

Method 514.6, 0.1g2/Hz from 100 to 1K Hz., -3dB octave 5-100 Hz and -6dB 1K-2K Hz,(Operational) |

||||

514 |

Sinusoidal Vibe |

TBD |

||||

501 |

Temp (High) |

3 |

3 periods (@ 4 hrs. ea.) within 24 hrs. cycle at 71 ºC baseplate |

|||

502 |

Temp (Low) |

1 |

3 periods (@ 4 hrs. ea.) within 24 hrs. cycle at -40 ºC baseplate |

|||

503 |

Temp (Shock) |

3 |

3 x 1 hr. each hot & cold cycles (non-operational) |

|||

507 |

Humidity |

II |

10 |

507.5-7 |

507.5-IX |

Cyclic high humidity (Cycle B2) |

500 |

Altitude (50K) |

II |

1 |

n/a |

n/a |

10m/s to 50,000ft for 1 hr. |

500 |

Altitude (70K) |

II |

1 |

n/a |

n/a |

10m/s to 70,000ft for 1 hr. |

513 |

Acceleration |

II |

1 |

513.6-II |

n/a |

Carrier-based Aircraft (18g’s max) |

516 |

Shock - Operating |

I |

3 |

516.6-I |

n/a |

40g’s, 3 pulses each ± X, Y, Z axis (total of 18 shock pulses) |

516 |

Shock - Crash |

V |

3 |

516.6-I |

n/a |

75g’s, 3 pulses each ± X, Y, Z axis (total of 18 shock pulses) |

Ingress Protection IEC 60529 (*1) |

||||||

No. |

Description |

Procedure |

Cycles |

Table |

Figure |

Comments |

IP54 |

Dust Protection |

|||||

IP54 |

Water Splashing |

|||||

IP65 |

Dust Tight |

|||||

IP65 |

Water Jets |

|||||

MIL-STD-461(G) |

Method/Curve/Procedure |

Comments |

CE102 |

Conducted emissions, power leads, 30 Hz to 10 kHz. |

|

CS101 |

Conducted emissions, power leads, 10 kHz to 10 MHz |

|

CS106 |

Conducted susceptibility, power leads, 30 Hz to 150 kHz. |

|

CS114 |

Conducted susceptibility, transients, power leads |

|

CS115 |

Conducted susceptibility, bulk cable injection, 10 kHz to 200 MHz |

|

CS116 |

Conducted susceptibility, bulk cable injection, impulse excitation |

|

RE101 |

Conducted susceptibility, damped sinusoidal transients, cables and power leads, 10 kHz to 100 MHz |

|

RE102 |

Radiated emissions, magnetic field, 30 Hz to 100 kHz. |

|

RS101 |

Radiated emissions, electric field, 10 kHz to 18 GHz. |

|

RS103 |

Radiated, susceptibility, magnetic field, 30 Hz – 100 kHz |

Notes:

1) Designed to meet / Generic Test Reports (contact factory for availability).

2) Utilizing proper shielded cables and system practices.

|

Note

|

Specifications are subject to change without notice. |

UNPACKING AND INSPECTION

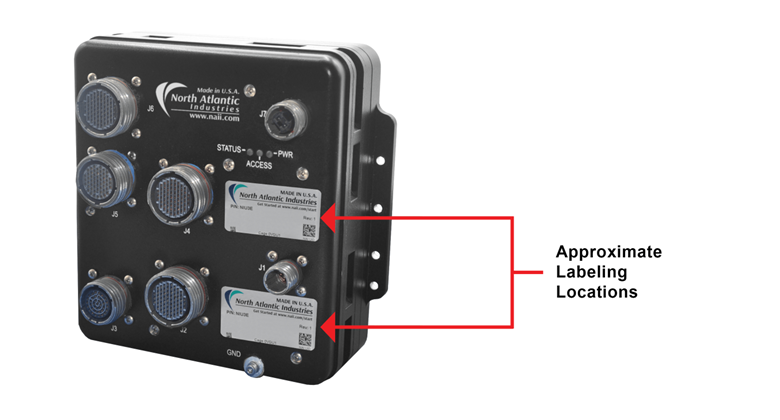

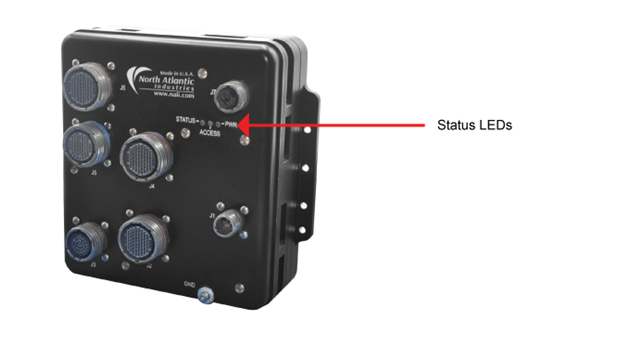

Figure 1. NIU3E

Unpacking

The NIU3E packing materials were designed specifically for transport protection of the NIU3E. When receiving the shipment container, inspect packaging for any evidence of physical damage. If damage is evident, it is recommended that the carrier agent is present when opening the shipping container. It is further recommended that all packing material is retained in the event the NIU3E needs to be shipped elsewhere.

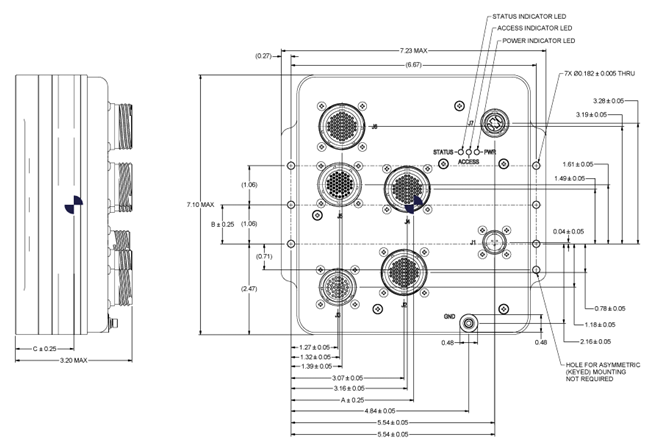

MECHANICAL

Mechanical Description

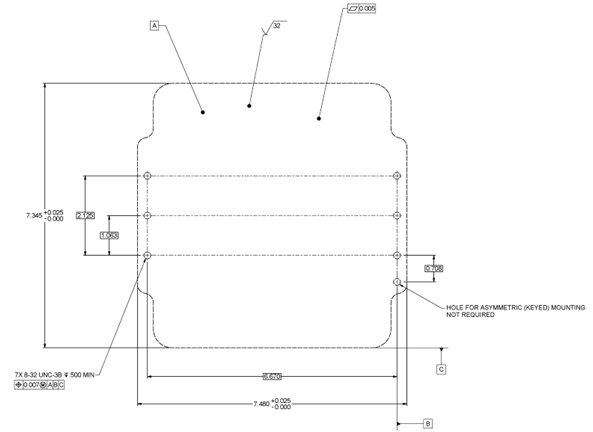

The NIU3E is a rugged, aluminum, conduction-cooled system. It must be mounted to a cold plate. The system thermal management design considerations should ensure that the chassis thermal interface (NIU3E bottom surface) does not exceed 71°C. Mounting holes are provided on the chassis bottom housing flanges (as depicted). See the outline drawing below.

Mounting Requirements

The NIU3E is conduction cooled and must be mounted in accordance with the drawing. The OID provides recommended hardware, torque, cold plate flatness and surface finish specifications, and thermal conductivity requirements.

Figure 3. NIU3E Outline Dimensions/Cold Plate Mounting Pattern (Reference Only)

Notes:

-

J7 Fiber Optic Connector is optional.

-

Unless otherwise specified, dimensions are in inches (mm); tolerances are:

-

2 PL DEC ±0.01; 3 PL DEC ±0.005

-

FRACT ±1/64 (0.4); ANGLES ±1/2 (12.7)

-

Chassis (Earth) GND

Chassis ground point threaded insert location is on the connector side of the NIU3E as shown

Figure 4. NIU3E Outline Dimensions/Chassis GND location

|

Note

|

Chassis GND braid or equivalent to be secured by #6-32 screw/studs (with a depth of 0.3 inches) as end application requires. The NIU3E chassis is provided with #6-32 threaded insert only. The recommended torque for the NIU3E Chassis GND screw is 11 in-lbs. (125 N·cm) |

CONNECTOR DESIGNATION AND DESCRIPTION

The Power, I/O Interface and Ethernet connectors are located on the NIU3E front panel housing.

Figure 5. NIU3E (Front Panel Connector Placement)

Connector Designation |

Description |

J1 |

Primary Power Connector, VDC |

J2 |

I/O Connector 1, Smart Module I/O Slot & Onboard Discrete I/O |

J3 |

I/O Connector 2, Onboard ARINC-429, MIL-STD-1553 & CANBus |

J4 |

GbE Connector 1, Switch Ports 1-8 |

j5 |

1x GbE ES2 Module Maintenance Port, RS-232 Management & Debug Port, System Reset |

J6 |

GbE Connector 2, Switch Ports 9-16 |

J7 |

4x Fiber Optic (optional configuration) |

J8* |

I/O Connector 3, Smart Module I/O Slot (* - as of 07/01/2024) |

Connector Details and Pinout

Generic pinout. See module I/O section or contact factory regarding any special module I/O configuration.

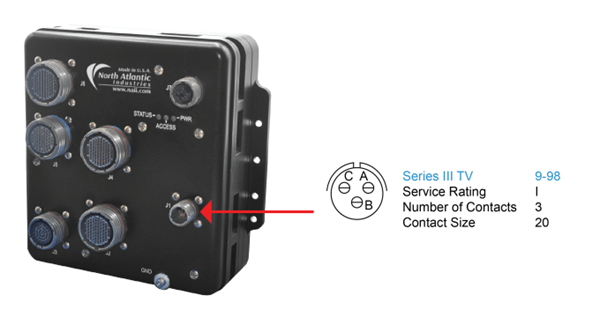

J1, Primary Power Connector

Primary input power is supported on the NIU3E via the J1 connector. Connectors used are as follows:

Figure 6. J1 Primary Power Connector Detail

Parts Identification

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J1 |

D38999/20WA98PA (10,000 pF, incl. ‘c-filter') |

9 / 98 |

3 |

D38999/26WA98SA |

05-0297-COM |

J2, I/O, Module-1 & Onboard Discrete I/O (DT) Function

The J2 I/O connector supports Module-1 and Onboard Discrete (DT) function I/O.

|

Note

|

This configuration of the J2 connector will be deprecated as of 07/01/2024. After that date, the J2 I/O connector will be configured to support Module-3 and Onboard Discrete (DT) function I/O. |

Figure 7. J2 I/O Module-1/Onboard Discrete Connector Detail

Parts Identification (Depricated as of 07/01/2024)

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J2 |

D38999/20WF35SA |

19 / 35 |

66 |

D38999/26WF35PA |

05-0285-COM |

Pinout (Depricated as of 07/01/2024)

Generic pinout. See module I/O section or contact factory regarding any special module I/O configuration.

J2 Connector Pin |

Signal |

Notes |

20 |

DT-IO-CH01 |

|

44 |

DT-IO-CH02 |

|

4 |

DT-IO-CH03 |

|

51 |

DT-IO-CH04 |

|

27 |

DT-IO-CH05 |

|

58 |

DT-IO-CH06 |

|

45 |

DT-IO-CH07 |

|

28 |

DT-IO-CH08 |

|

43 |

DT-IO-CH09 |

|

17 |

DT-IO-CH10 |

|

59 |

DT-IO-CH11 |

|

29 |

DT-IO-CH12 |

|

26 |

DT-IO-CH13 |

|

5 |

DT-IO-CH14 |

|

34 |

DT-IO-CH15 |

|

52 |

DT-IO-CH16 |

|

36 |

DT-IO-CH17 |

|

54 |

DT-IO-CH18 |

|

60 |

DT-IO-CH19 |

|

25 |

DT-IO-CH20 |

|

10 |

DT-IO-CH21 |

|

37 |

DT-IO-CH22 |

|

53 |

DT-IO-CH23 |

|

35 |

DT-IO-CH24 |

|

11 |

DT-ISO-GND |

Signal/System Ground |

19 |

DT-ISO-GND |

Signal/System Ground |

46 |

DT-ISO-GND |

Signal/System Ground |

47 |

DT-ISO-GND |

Signal/System Ground |

12 |

DT-VCC1 |

|

18 |

DT-VCC2 |

|

38 |

DT-VCC3 |

|

55 |

DT-VCC4 |

|

65 |

MOD1-DATIO01 |

|

64 |

MOD1-DATIO02 |

|

16 |

MOD1-DATIO03 |

|

9 |

MOD1-DATIO04 |

|

22 |

MOD1-DATIO05 |

|

14 |

MOD1-DATIO06 |

|

3 |

MOD1-DATIO07 |

|

8 |

MOD1-DATIO08 |

|

21 |

MOD1-DATIO09 |

|

7 |

MOD1-DATIO10 |

|

30 |

MOD1-DATIO11 |

|

6 |

MOD1-DATIO12 |

|

56 |

MOD1-DATIO13 |

|

62 |

MOD1-DATIO14 |

|

66 |

MOD1-DATIO15 |

|

40 |

MOD1-DATIO16 |

|

41 |

MOD1-DATIO17 |

|

50 |

MOD1-DATIO18 |

|

42 |

MOD1-DATIO19 |

|

32 |

MOD1-DATIO20 |

|

24 |

MOD1-DATIO21 |

|

48 |

MOD1-DATIO22 |

|

23 |

MOD1-DATIO23 |

|

39 |

MOD1-DATIO24 |

|

15 |

MOD1-DATIO25 |

|

31 |

MOD1-DATIO26 |

|

2 |

MOD1-DATIO27 |

|

13 |

MOD1-DATIO28 |

|

57 |

MOD1-DATIO29 |

|

49 |

MOD1-DATIO30 |

|

33 |

MOD1-DATIO31 |

|

63 |

MOD1-DATIO32 |

|

1 |

SYS-GND |

Signal/System Ground |

61 |

SYS-GND |

Signal/System Ground |

Parts Identification (Starting as of 07/01/2024)

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J2 |

D38999/20WF35SA |

19 / 35 |

66 |

D38999/26WF35PA |

05-0285-COM |

Pinout (Starting as of 07/01/2024)

Generic pinout. See module I/O section or contact factory regarding any special module I/O configuration.

J2 Connector Pin |

Signal |

Notes |

20 |

DT-IO-CH01 |

|

44 |

DT-IO-CH02 |

|

4 |

DT-IO-CH03 |

|

51 |

DT-IO-CH04 |

|

27 |

DT-IO-CH05 |

|

58 |

DT-IO-CH06 |

|

45 |

DT-IO-CH07 |

|

28 |

DT-IO-CH08 |

|

43 |

DT-IO-CH09 |

|

17 |

DT-IO-CH10 |

|

59 |

DT-IO-CH11 |

|

29 |

DT-IO-CH12 |

|

26 |

DT-IO-CH13 |

|

5 |

DT-IO-CH14 |

|

34 |

DT-IO-CH15 |

|

52 |

DT-IO-CH16 |

|

36 |

DT-IO-CH17 |

|

54 |

DT-IO-CH18 |

|

60 |

DT-IO-CH19 |

|

25 |

DT-IO-CH20 |

|

10 |

DT-IO-CH21 |

|

37 |

DT-IO-CH22 |

|

53 |

DT-IO-CH23 |

|

35 |

DT-IO-CH24 |

|

11 |

DT-ISO-GND |

Signal/System Ground |

19 |

DT-ISO-GND |

Signal/System Ground |

46 |

DT-ISO-GND |

Signal/System Ground |

47 |

DT-ISO-GND |

Signal/System Ground |

12 |

DT-VCC1 |

|

18 |

DT-VCC2 |

|

38 |

DT-VCC3 |

|

55 |

DT-VCC4 |

|

65 |

MOD3-DATIO01 |

|

64 |

MOD3-DATIO02 |

|

16 |

MOD3-DATIO03 |

|

9 |

MOD3-DATIO04 |

|

22 |

MOD3-DATIO05 |

|

14 |

MOD3-DATIO06 |

|

3 |

MOD3-DATIO07 |

|

8 |

MOD3-DATIO08 |

|

21 |

MOD3-DATIO09 |

|

7 |

MOD3-DATIO10 |

|

30 |

MOD3-DATIO11 |

|

6 |

MOD3-DATIO12 |

|

56 |

MOD3-DATIO13 |

|

62 |

MOD3-DATIO14 |

|

66 |

MOD3-DATIO15 |

|

40 |

MOD3-DATIO16 |

|

41 |

MOD3-DATIO17 |

|

50 |

MOD3-DATIO18 |

|

42 |

MOD3-DATIO19 |

|

32 |

MOD3-DATIO20 |

|

24 |

MOD3-DATIO21 |

|

48 |

MOD3-DATIO22 |

|

23 |

MOD3-DATIO23 |

|

39 |

MOD3-DATIO24 |

|

15 |

MOD3-DATIO25 |

|

31 |

MOD3-DATIO26 |

|

2 |

MOD3-DATIO27 |

|

13 |

MOD3-DATIO28 |

|

57 |

MOD3-DATIO29 |

|

49 |

MOD3-DATIO30 |

|

33 |

MOD3-DATIO31 |

|

63 |

MOD3-DATIO32 |

|

1 |

SYS-GND |

Signal/System Ground |

61 |

SYS-GND |

Signal/System Ground |

J3, I/O, Onboard ARINC-429/MIL-STD-1553/CANBus Functions

The J3 IO connector supports Onboard ARINC/MIL-STD/1553/CANBus function I/O

Figure 8. J3 I/O Onboard Functions Connector Detail

Parts Identification

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J3 |

D38999/20WD35SA |

15/35 |

37 |

D38999/26WD35PA |

05-0532-COM |

Pinout

Generic pinout. See module I/O section or contact factory regarding any special module I/O configuration

J3 Connector Pin |

Signal |

Notes |

7 |

1553-BUSA-CH1- |

|

6 |

1553-BUSA-CH1+ |

|

23 |

1553-BUSA-CH2- |

|

33 |

1553-BUSA-CH2+ |

|

25 |

1553-BUSB-CH1- |

|

24 |

1553-BUSB-CH1+ |

|

9 |

1553-BUSB-CH2- |

|

8 |

1553-BUB-CH2+ |

|

21 |

AR429-CH1-A |

|

22 |

AR429-CH1-B |

|

20 |

AR429-CH2-A |

|

31 |

AR429-CH2-B |

|

18 |

AR429-CH3-A |

|

30 |

AR429-CH3-B |

|

36 |

AR429-CH4-A |

|

37 |

AR429-CH4-B |

|

17 |

AR429-CH5-A |

|

29 |

AR429-CH5-A |

|

1 |

AR429-CH6-A |

|

19 |

AR429-CH6-B |

|

2 |

AR429-CH7-A |

|

3 |

AR429-CH7-B |

|

4 |

AR429-CH8-A |

|

5 |

AR429-CH8-B |

|

28 |

CAN-CH1-H |

|

27 |

CAN-CH1-L |

|

16 |

CAN-CH2-H |

|

15 |

CAN-CH2-L |

|

35 |

CAN-CH3-H |

|

34 |

CAN-CH3-L |

|

14 |

CAN-CH4-H |

|

13 |

CAN-CH4-L |

|

11 |

GND-CAN1 |

Signal/System Ground |

26 |

GND-CAN2 |

Signal/System Ground |

10 |

GND-CAN3 |

Signal/System Ground |

12 |

GND-CAN4 |

Signal/System Ground |

32 |

N/C |

J4, I/O, Ethernet Switch Module (Ports 1-8)

The J4 I/O connector supports eight of the sixteen Ethernet Switch Ports (Ports 1 through 8).

Figure 9. J4 I/O ES2 (Ports 1-8) Connector Detail

Parts Identification

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J4 |

D38999/20WF35SB |

19/35 |

66 |

D38999/26WF35PB |

05-0541-COM |

Pinout

Generic pinout. See module I/O section or contact factory regarding any special module I/O configuration

J4 Connector Pin |

Signal |

Notes |

40 |

ETH01_T0N |

*1 |

31 |

ETH01_T0P |

*1 |

57 |

ETH01_T1N |

*1 |

50 |

ETH01_T1P |

*1 |

37 |

ETH01_T2N |

*1 |

28 |

ETH01_T2P |

*1 |

48 |

ETH01_T3N |

*1 |

39 |

ETH01_T3P |

*1 |

56 |

ETH02_T0N |

*1 |

49 |

ETH02_T0P |

*1 |

62 |

ETH02_T1N |

*1 |

63 |

ETH02_T1P |

*1 |

47 |

ETH02_T2N |

*1 |

38 |

ETH02_T2P |

*1 |

61 |

ETH02_T3N |

*1 |

55 |

ETH02_T3P |

*1 |

46 |

ETH03_T0N |

*1 |

53 |

ETH03_T0P |

*1 |

65 |

ETH03_T1N |

*1 |

66 |

ETH03_T1P |

*1 |

36 |

ETH03_T2N |

*1 |

45 |

ETH03_T2P |

*1 |

58 |

ETH03_T3N |

*1 |

52 |

ETH03_T3P |

*1 |

60 |

ETH04_T0N |

*1 |

54 |

ETH04_T0P |

*1 |

59 |

ETH04_T1N |

*1 |

64 |

ETH04_T1P |

*1 |

51 |

ETH04_T2N |

*1 |

44 |

ETH04_T2P |

*1 |

43 |

ETH04_T3N |

*1 |

35 |

ETH04_T3P |

*1 |

6 |

ETH05_T0N |

*1 |

12 |

ETH05_T0P |

*1 |

2 |

ETH05_T1N |

*1 |

1 |

ETH05_T1P |

*1 |

17 |

ETH05_T2N |

*1 |

25 |

ETH05_T2P |

*1 |

18 |

ETH05_T3N |

*1 |

26 |

ETH05_T3P |

*1 |

3 |

ETH06_T0N |

*1 |

7 |

ETH06_T0P |

*1 |

8 |

ETH06_T1N |

*1 |

14 |

ETH06_T1P |

*1 |

4 |

ETH06_T2N |

*1 |

10 |

ETH06_T2P |

*1 |

5 |

ETH06_T3N |

*1 |

11 |

ETH06_T3P |

*1 |

9 |

ETH07_T0N * |

1 |

15 |

ETH07_T0P |

*1 |

16 |

ETH07_T1N |

*1 |

23 |

ETH07_T1P |

*1 |

19 |

ETH07_T2N |

*1 |

27 |

ETH07_T2P |

*1 |

13 |

ETH07_T3N |

*1 |

20 |

ETH07_T3P |

*1 |

24 |

ETH08_T0N |

*1 |

32 |

ETH08_T0P |

*1 |

42 |

ETH08_T1N |

*1 |

41 |

ETH08_T1P |

*1 |

21 |

ETH08_T2N |

*1 |

29 |

ETH08_T2P |

*1 |

22 |

ETH08_T3N |

*1 |

30 |

ETH08_T3P |

*1 |

33 |

SYS_GND |

Signal/System Ground |

34 |

SYS_GND |

Signal/System Ground |

Notes:

-

10/100/1000Base-T signal definitions:

* ETHnn_Tx(y) where:

* nn = Ethernet Switch Port number

* x = Twisted pair/differential signal number (0, 1, 2 or 3)

* y = Differential signal polarity (p = positive(+) and n = negative(-))

J5, Ethernet Communications & Debug

The NIU3E supports up to two 10/100/1000Base-T ports (when appropriately configured) and debug/maintenance signals. The debug/maintenance signals provided are an RS-232 console port and System Reset (for a soft reset/reload). Additionally, typically for ARM/processor optioned configurations, a USB 2.0 port, Hardware Write Protect (for SATA accessibility) and a Real Time Clock Standby (i.e. auxiliary 3.3V/battery backup for the real time clock) are also provided.

Figure 10. J5 Ethernet Communications & Debug Connector Detail

Parts Identification

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J5 |

D38999/20WE35SN |

17/35 |

55 |

D38999/26WE35PN |

05-0534-COM |

Pinout

J5 Connector Pin |

Signal |

Notes |

1 |

SYS-GND |

*7 |

2 |

SW-ETH1-TP0+ |

*8 |

3 |

SW-ETH1-TP0- |

*8 |

4 |

SER0-TXD |

*2 |

5 |

N/C |

*10 |

6 |

USB0-D- |

*5 |

7 |

SYS-GND |

*7 |

8 |

SW-ETH1-TP2+ |

*8 |

9 |

SW-ETH1-TP2- |

*8 |

10 |

SER0-RXD |

*2 |

11 |

N/C |

*10 |

12 |

USB0-D+ |

*5 |

13 |

N/C |

*10 |

14 |

SW-ETH1-TP1+ |

*8 |

15 |

SYS-GND |

*7 |

16 |

SW-ETH1-TP3+ |

*8 |

17 |

N/C |

*10 |

18 |

N/C |

*10 |

19 |

USB-GND |

*5 |

20 |

USB0-5V0 |

*5 |

21 |

MOD2-UART-RX |

*9 |

22 |

SW-ETH1-TP1- |

*8 |

23 |

I2C1-SCL |

*6 |

24 |

SW-ETH1-TP3- |

*8 |

25 |

MB-ETH1-TP3- |

*8 |

26 |

N/C |

*10 |

27 |

N/C |

*10 |

28 |

N/C |

*10 |

29 |

MOD2-UART-TX |

*9 |

30 |

SYS-GND |

*7 |

31 |

I2C1-SDA |

*6 |

32 |

MB-ETH1-TP3+ |

*8 |

33 |

SYS-GND |

*7 |

34 |

MB-ETH1-TP2 |

*8 |

35 |

SYS-GND |

*7 |

36 |

SYS-GND |

*7 |

37 |

MB-ETH0-TP1+ |

*8 |

38 |

SYSRSTn |

*1 |

39 |

ENABLE |

*4 |

40 |

MB-ETH1-TP1 |

*8 |

41 |

SYS-GND |

*7 |

42 |

MB-ETH1-TP2+ |

*8 |

43 |

MB-ETH0-TP0+ |

*8 |

44 |

SYS-GND |

*7 |

45 |

MB-ETH0-TP1 |

*8 |

46 |

NVMRO |

*3 |

47 |

MB-ETH1-TP1+ |

*8 |

48 |

MB-ETH1-TP0 |

*8 |

49 |

SYS-GND |

*7 |

50 |

MB-ETH0-TP0 |

*8 |

51 |

MB-ETH0-TP3+ |

*8 |

52 |

MB-ETH0-TP3 |

*8 |

53 |

MB-ETH1-TP0+ |

*8 |

54 |

MB-ETH0-TP2+ |

*8 |

55 |

MB-ETH0-TP2 |

*8 |

Notes:

-

SYSRSTn: An active “low” or GND logic level (as referenced to System GND of the NIU3E) assertion of the SYSRST# signal (internally pulled ‘high') on the NIU3E processor and module cards will initiate an NIU3E system reset.

-

Debug: RS-232 Serial Communications Console port

-

NVMRO: Used for SATA Flash write enable/disable on the processor of the NIU3E. OPEN for Write Protect, GND for Write Enable.

-

ENABLE: Used to power the PSU. OPEN for PSU Power-On, GND for PSU Power-Off.

-

USB: USB 2.0 compatibility - accessible with processor accessible version of the NIU3E. (ARM option only).

-

I2C1-Sxy: The two lines used for I2C communications. SCL (Serial Clock) synchronizes all data transfers over the I2C bus, SDA (Serial Data) carries the data.

-

GND: All the identified GNDs are referenced to the same internal signal GND (System GND).

-

ETHx-TPyz: Standard NIU3E configuration provides 2x 10/100/1000Base-T Ethernet ports. If the Gigabit Fiber Optic (Gb FO) connection is specified, the Ethernet functionality will not be available These signals are considered no-connects (N/C).

-

UART: The two lines that are used to transmit and receive serial data.

-

N/C: Signals are undefined in the standard NIU3E configurations. These signals are considered no-connects (N/C)

J6, I/O, Ethernet Switch Module (Ports 9-16)

The J6 I/O connector supports eight of the sixteen Ethernet Switch Ports (Ports 9 through 16)

Figure 11. J6 I/O ES2 (Ports 9-16) Connector Detail

Parts Identification

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J6 |

D38999/20WE35SN |

19/35 |

66 |

D38999/26WE35PN |

05-0584-COM |

Pinout

Generic pinout. See module I/O section or contact factory regarding any special module I/O configuration.

J6 Connector Pin |

Signal |

Notes |

6 |

ETH09_T0N |

*1 |

12 |

ETH09_T0P |

*1 |

2 |

ETH09_T1N |

*1 |

1 |

ETH09_T1P |

*1 |

17 |

ETH09_T2N |

*1 |

25 |

ETH09_T2P |

*1 |

18 |

ETH09_T3N |

*1 |

26 |

ETH09_T3P |

*1 |

3 |

ETH10_T0N |

*1 |

7 |

ETH10_T0P |

*1 |

8 |

ETH10_T1N |

*1 |

14 |

ETH10_T1P |

*1 |

4 |

ETH10_T2N |

*1 |

10 |

ETH10_T2P |

*1 |

5 |

ETH10_T3N |

*1 |

11 |

ETH10_T3P |

*1 |

9 |

ETH11_T0N |

*1 |

15 |

ETH11_T0P |

*1 |

16 |

ETH11_T1N |

*1 |

23 |

ETH11_T1P |

*1 |

19 |

ETH11_T2N |

*1 |

27 |

ETH11_T2P |

*1 |

13 |

ETH11_T3N |

*1 |

20 |

ETH11_T3P |

*1 |

24 |

ETH12_T0N |

*1 |

32 |

ETH12_T0P |

*1 |

42 |

ETH12_T1N |

*1 |

41 |

ETH12_T1P |

*1 |

21 |

ETH12_T2N |

*1 |

29 |

ETH12_T2P |

*1 |

22 |

ETH12_T3N |

*1 |

30 |

ETH12_T3P |

*1 |

40 |

ETH13_T0N |

*1 |

31 |

ETH13_T0P |

*1 |

57 |

ETH13_T1N |

*1 |

50 |

ETH13_T1P |

*1 |

37 |

ETH13_T2N |

*1 |

28 |

ETH13_T2P |

*1 |

48 |

ETH13_T3N |

*1 |

39 |

ETH13_T3P |

*1 |

56 |

ETH14_T0N |

*1 |

49 |

ETH14_T0P |

*1 |

62 |

ETH14_T1N |

*1 |

63 |

ETH14_T1P |

*1 |

47 |

ETH14_T2N |

*1 |

38 |

ETH14_T2P |

*1 |

61 |

ETH14_T3N |

*1 |

55 |

ETH14_T3P |

*1 |

46 |

ETH15_T0N |

*1 |

53 |

ETH15_T0P |

*1 |

65 |

ETH15_T1N |

*1 |

66 |

ETH15_T1P |

*1 |

36 |

ETH15_T2N |

*1 |

45 |

ETH15_T2P |

*1 |

58 |

ETH15_T3N |

*1 |

52 |

ETH15_T3P |

*1 |

60 |

ETH16_T0N |

*1 |

54 |

ETH16_T0P |

*1 |

59 |

ETH16_T1N |

*1 |

64 |

ETH16_T1P |

*1 |

51 |

ETH16_T2N |

*1 |

44 |

ETH16_T2P |

*1 |

43 |

ETH16_T3N |

*1 |

35 |

ETH16_T3P |

*1 |

33 |

SYS_GND |

Signal/System Ground |

34 |

SYS_GND |

Signal/System Ground |

Notes:

-

10/100/1000Base-T signal definitions:

* ETHnn_Tx(y) where:

* nn = Ethernet Switch Port number

* x = Twisted pair/differential signal number

* y = Differential signal polarity (p=positive(+) and n=negative(-))

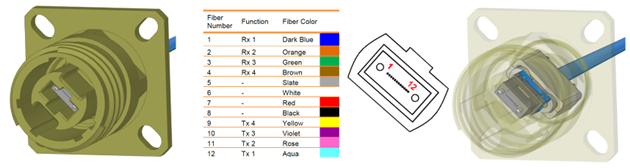

J7, Fiber Optic, Option

The NIU3E supports up to four Tx and Rx Fiber Optic (Gb) Connections when appropriately configured.

Figure 12. J7 Gb Fiber Optic Connector Detail (option)

Parts Identification

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J7 |

MT38999 FO MIL-circular Amphenol: CF-599011-01S (Modified, NAI) Olive drab, Cd Includes: MT 12 fiber ferrule |

11/01 FO, single cavity |

N/A (FO ferrule) |

Amphenol: CF-599611-01P (olive drab, Cd) Includes: MT 12 fiber ferrule with female MT to 38999 adapter kit (MT female Assy Kit (flat ribbon) / Amphenol CF-198137-000) |

05-529 |

Figure 13. FO MT38999 Connector Fiber Ferrule Assembly Detail (for reference only)

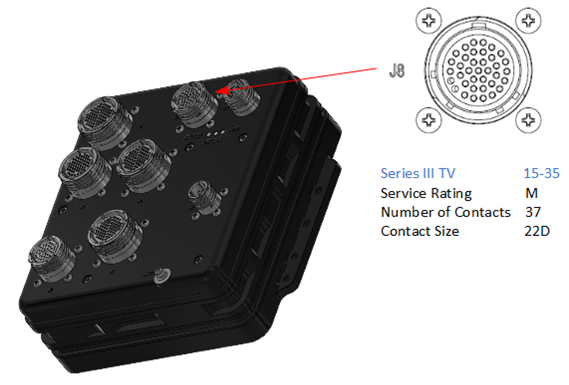

J8, I/O, Module-1 (Starting as of 07/01/2024)

The J8 I/O connector supports Module-1 function I/O.

|

Note

|

The J8 connector will be applicable to the NIU3E as of 07/01/2024. It is not available with legacy NIU3E units built prior to 07/01/2024. |

Figure 14. J8 I/O Module-1 Connector Detail

Parts Identification (Starting as of 07/01/2024)

Chassis (Box-level) |

Mating Cable Connector |

||||

Designation |

MIL-DTL Equivalent Reference |

Shell/Insert |

Pin-count |

MIL-DTL Equivalent Reference |

NAI P/N (for reference) |

J8 |

D38999/20WD35SN |

15 / 35 |

37 |

D38999/26WD35PN |

05-0302-COM |

Pinout (Starting as of 07/01/2024

Generic pinout. See module I/O section or contact factory regarding any special module I/O configuration.

J8 Connector Pin |

Signal |

Notes |

3 |

MB-ETH1-TP0N |

|

2 |

MB-ETH1-TP0P |

|

31 |

MB-ETH1-TP1N |

|

20 |

MB-ETH1-TP1P |

|

5 |

MB-ETH1-TP2N |

|

4 |

MB-ETH1-TP2P |

|

7 |

MB-ETH1-TP3N |

|

6 |

MB-EHT1-TP3P |

|

9 |

MB-ETH2-TP0N |

|

8 |

MB-ETH2-TP0P |

|

33 |

MB-ETH2-TP1N |

|

23 |

MB-ETH2-TP1P |

|

25 |

MB-ETH2-TP2N |

|

24 |

MB-ETH2-TP2P |

|

28 |

MB-ETH2-TP3N |

|

27 |

MB-ETH2-TP3P |

|

29 |

MB-ETH3-TP0N |

|

17 |

MB-ETH3-TP0P |

|

35 |

MB-ETH3-TP1N |

|

34 |

MB-ETH3-TP1P |

|

30 |

MB-ETH3-TP2N |

|

18 |

MB-ETH3-TP2P |

|

14 |

MB-ETH3-TP3N |

|

13 |

MB-ETH3-TP3P |

|

16 |

MB-ETH4-TP0N |

|

15 |

MB-ETH4-TP0P |

|

37 |

MB-ETH4-TP1N |

|

36 |

MB-ETH4-TP1P |

|

19 |

MB-ETH4-TP2N |

|

1 |

MB-ETH4-TP2P |

|

22 |

MB-ETH4-TP3N |

|

21 |

MB-ETH4-TP3P |

|

10 |

||

11 |

||

12 |

||

26 |

||

32 |

POWER-UP AND OPERATIONAL DESCRIPTION

Panel LEDs & Functions

Front Panel LEDs indications

Figure 14. NIU3E Status LEDs Location

LED |

STATUS / FUNCTION |

|

ILLUMINATED |

EXTINGUISHED |

|

POWER GRN: |

Blinking: Initializing Steady On: Power-On/Ready |

Power-off |

ACCESS YEL: |

Blinking: Unit Access (GbE activity) |

No Unit Access or Activity |

STATUS RED: |

Module BIT (Attention required) |

No Module BIT Attention Required |

REGISTER MEMORY MAP ADDRESSING

The register map address consists of the following:

-

cPCI/PCIe BAR or Base Address for the Board

-

Module Slot Base Address

-

Function Offset Address

Board Base Address

The table below lists the BAR used for access to the motherboard and module registers. The second BAR is used internally for motherboard and module firmware updates. The other cPCI/PCIe BARs not listed are not used.

NAI Boards |

Device ID |

Bus |

Motherboard and Module Register Access |

Motherboard and Module Firmware Updates |

Slave Boards |

||||

NIU3E |

N/A |

N/A |

Direct Memory Access |

Internal Direct Memory Access |

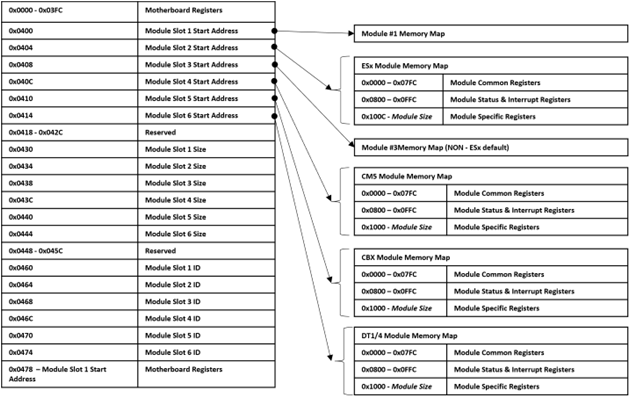

Module Slot and Function Addresses

The NIU3E includes (4) basic preconfigured IO functions embedded within the motherboard (onboard functions). These functions are like the standard NAI COSA® smart functions identified as:

-

CM5 = Support function ID; for 2 channels MIL-STD-1553 & 8 Channels ARINC 429/575 (combination functions)

-

CBX = Support function ID; for 2 channels CAN Bus

-

DT1/4 = Support function ID for 24-CH programmable Discrete I/O (standard/enhanced capability option)

Additionally, the NIU3E incorporates a double-wide Ethernet Switch Module (ES2) and can be fitted with one additional function module.

The following depicts the memory structure allocated for the (3) onboard function IDs and (2) configured functions

NIU3E function/module structure/order" |

|

Function #1: |

Expansion Module 1 |

Function #2: |

Ethernet Switch Module (ES2) |

Function #3: |

Onboard Function CM5-type (MIL-STD-1553, ARINC 429) |

Function #4: |

Onboard Function CBX-type (CAN Bus) |

Function #5: |

Onboard Function DT1/4-tpe (Discrete I/O) |

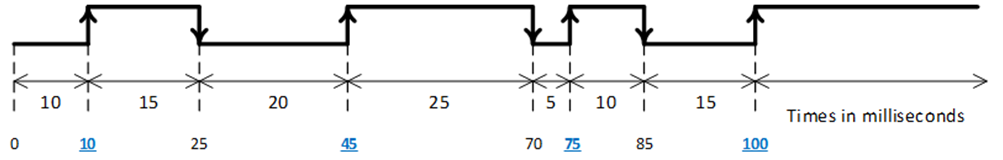

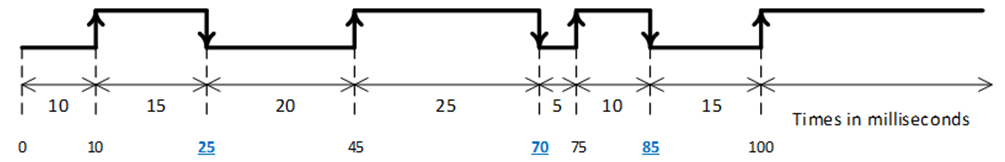

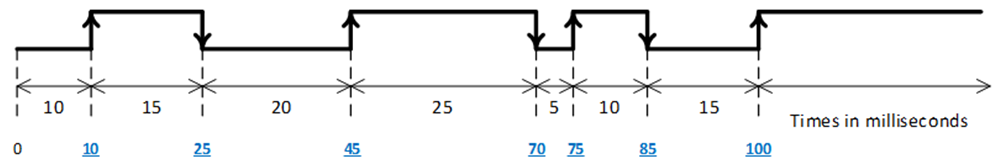

The “start” address of the function on the NIU3E are factory pre-defined (and read from) the Module Address register. Refer to Figure 15.

Figure 15. Register Memory Map Addressing Example for NIU3E

Address Calculation

Motherboard Registers

Read/Write access to the motherboard registers starts with the base address for the board and then the motherboard base offset address.

For example, to address Module Slot 1 Start Address register (i.e. register address = 0x0400):

-

Start with the base address for the board.

-

Add the motherboard base register address offset.

Motherboard Address = |

Base Address + Motherboard Address Offset |

= 0x0000 0400 |

0x0000 0000 + 0x0400 |

Module Registers:

Read/Write access to the Function module’s registers start with the base address of the board. Add the “content” for the Module Start Address and then, add the specific module function register offset.

For example, to address an appropriate/specific function module with a register offset:

-

Start with the base address for the board.

-

Add the value (contents) from the module base address offset register (contents/value of Motherboard Memory register for Module 1 (i.e., @ 0x0400) = 0x4000.

-

Then add the specific module function Register Offset of interest (i.e., A/D Reading Ch 1 @ 0x1000)

(Function Specific) Address = |

Base Address |

Module Base Address Offset |

Function Register Offset |

= 0x0000 5000 |

0x0000 0000 |

0x4000 |

0x1000 |

REGISTER DESCRIPTIONS

Module Information Registers

The Module Slot Address, Module Slot Size and Module Slot ID provide information about the modules detected on the board.

Module Slot Address |

|

Function: |

Specifies the Base Address for the module in the specific slot position. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Based on board’s module configuration. |

Operational Settings: |

0x0000 0000 indicates no Module found. |

Module Slot Size |

|

Function: |

Specifies the Memory Size (in bytes) allocated for the module in the specific slot position. |

Type: |

unsigned binary word (32-bit) |

Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Assigned by factory for the module. |

Operational Settings: |

0x0000 0000 indicates no Module found. |

Module Slot ID |

|

Function: |

Specifies the Model ID for the module in the specified slot position. |

Type: |

4-character ASCII string |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Assigned by factory for the module. |

Operational Settings: |

The Module ID is formatted as four ASCII bytes: three characters followed by a space. Module IDs are in little-endian order with a single space following the first three characters. For example, 'TL1' is '1LT', 'SC1' is '1CS' and so forth. Example below is for “TL1” (MSB justified). All value of 0000 0000 indicates no Module found. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

ASCII Character (ex: 'T' - 0x54) |

ASCII Character (ex: 'L' - 0x4C) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ASCII Character (ex: '1' - 0x31) |

ASCII Space (' ' - 0x20) |

||||||||||||||

Hardware Information Registers

The registers identified in this section provide information about the board’s hardware.

Product Serial Number |

|

Function: |

Specifies the Board Serial Number. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Serial number assigned by factory for the board. |

Operational Settings: |

N/A |

Platform

Function: Specifies the Board Platform Identifier. Values are for the ASCII characters for the NAI valid platforms (Identifiers).

Type: 4-character ASCII string

Data Range: See table below.

Read/Write: R

Initialized Value: ASCII code is for the Platform Identifier of the board

Operational Settings: NAI platform for this board is shown below:

NAI Platform |

Platform Identifier |

4-character ASCII string |

NIU |

00 |

0x0000 3030 |

Model

Function: Specifies the Board Model Identifier. Values are for the ASCII characters for the NAI valid models.

Type: 4-character ASCII string

Data Range: See table below.

Read/Write: R

Initialized Value: ASCII code is for the Model Identifier of the board

Operational Settings: NAI model for this board is shown below:

NAI Model |

4-character ASCII string |

NIU |

0x0055 494E |

Generation

Function: Specifies the Board Generation. Identifier values are for the ASCII characters for the NAI valid generation identifiers.

Type: 4-character ASCII string

Data Range: See table below.

Read/Write: R

Initialized Value: ASCII code is for the Generation Identifier of the board

Operational Settings: NAI generation for this board is shown below:

NAI Generation |

4-character ASCII string |

3E |

0x0000 4533 |

Processor Count/Ethernet Interface Count

Function: Specifies the Processor Count and Ethernet Interface Count.

Type: unsigned binary word (32-bit)

Data Range: See table below.

Read/Write: R

Operational Settings:

Processor Count - Indicates the number of unique processor types on the motherboard = 1

Ethernet Interface Count - Indicates the number of Ethernet interfaces on the product motherboard. For NIU3A, the Ethernet Interface Count is set for Dual Ethernet = 2.

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Processor Count (0x0001) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Ethernet Interface Count (0x0002) |

|||||||||||||||

Maximum Module Slot Count?ARM Platform Type

Function: Maximum Module Slot Count and Specifies the ARM Platform Type.

Type: unsigned binary word (32-bit)

Data Range: See table below.

Read/Write: R

Operational Settings:

Maximum Module Slot Count = 6.

ARM Platform Type - Xilinx UltraScale+ = 3

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Maximum Module Slot = 0x0006 |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ARM Platform Type = 0x0003 (UltraScale) |

|||||||||||||||

Processor Operating System Registers

The registers in this section provide information about the Operating System that is running on the host processor on the motherboard. For boards that have more than one processor (ex. 75PPC1, 75INT2, 68PPC2, etc), the host processor would be the Power-PC or Intel processor.

ARM Processor Platform

Edit this on GitLab

Function: |

Specifies the ARM Processor on the motherboard. Values are for the ASCII characters for the NAI host processor platforms specified by the Operating System. |

Type: |

8-character ASCII string - Two (2) unsigned binary word (32-bit) |

Data Range: |

N/A |

Read/Write: |

R |

Initialized Value: |

ASCII code is for the Host Platform Identifier of the board. |

Operational Settings: |

Valid NAI platforms based on Operating System loaded to host processor. |

Processor Platform (Note: 8-character ASCII string) (“aarch64”) |

|||||||||||||||

Word 1 (0x6372 6161 = “craa”) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

'c' (0x63) |

'r' (0x72) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

'a' (0x61) |

'a' (0x61) |

||||||||||||||

Word 2 (0x0034 3668 = “ 46h”) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

null (0x00) |

'4' (0x34) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

'6' (0x36) |

'h' (0x68) |

||||||||||||||

Processor Operating System

Edit this on GitLab

Function: |

Specifies the Operating System installed for the host processor. Values are for the ASCII characters for the NAI supported operating systems. |

Type: |

12-character ASCII string - Three (3) unsigned binary word (32-bit) |

Data Range: |

N/A |

Read/Write: |

R |

Operational Settings: |

ASCII, 12 characters; ('Linux', 'VxWorks', 'RTOS', …) |

Processor Platform (Note: 12-character ASCII string) (“Linux”) |

|||||||||||||||

Word 1 (0x756E 694C = “uniL”) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

'u' (0x75) |

'n' (0x6E) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

'i' (0x69) |

'L' (0x4C) |

||||||||||||||

Word 2 (0x0000 0078 = “ x”) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

null (0x00) |

null (0x00) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

null (0x00) |

null (0x00) |

||||||||||||||

Word 3 (0x0000 0000 = “ ”) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

null (0x00) |

null (0x00) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

null (0x00) |

null (0x00) |

||||||||||||||

Motherboard Firmware Information Registers

The registers in this section provide information on the revision of the firmware installed on the motherboard.

Motherboard Core (MBCore) Firmware Version |

|

Function: |

Specifies the Version of the NAI factory provided Motherboard Core Application installed on the board. |

Type: |

Two (2) unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Operational Settings: |

The motherboard firmware version consists of four components: Major, Minor, Minor 2 and Minor 3. |

Motherboard Core Firmware Version (Note: little-endian order in register) (ex. 4.7.0.0) |

|||||||||||||||

Word 1 (Ex. 0007 0004 = 4.7 (Major.Minor) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Minor (ex: 0x0007 = 7) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Major (ex: 0x0004 = 4) |

|||||||||||||||

Word 2 (Ex. 0x0000 0000 = 0000 = 0.0 (Minor2.Minor3)) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Minor 3 (ex: 0x000 = 0) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Minor 2 (ex: 0x000 = 0) |

|||||||||||||||

Motherboard Firmware Build Time/Date |

|

Function: |

Specifies the Build Date/Time of the NAI factory provided Motherboard Core Application installed on the board. |

Type: |

Two (2) unsigned binary word (32-bit) |

Data Range: |

N/A |

Read/Write: |

R |

Operational Settings: |

The motherboard firmware time consists of the Build Date and Build Time. NOTE: On some builds the the Date/Time fields are fixed to 0000 0000 to maintain binary consistency across builds. |

Motherboard Firmware Build Time (Note: little-endian order in register) |

|||||||||||||||

Word 1 - Build Date (ex. 0x030C 07E2 = 2018-12-03) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Day (ex: 0x03 = 3) |

Month (ex: 0x0C = 12) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Year (ex: 0x07E2 = 2018) |

|||||||||||||||

Word 2 - Build Time (ex. 0x001B 3B0A = 10:59:27) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

null (0x00) |

Seconds (ex: 0x1B = 27) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Minutes (ex: 0x3B = 59) |

Hours (ex: 0x0A = 10) |

||||||||||||||

Motherboard FPGA Firmware Version

Edit this on GitLab

Function: |

Specifies the Version of the NAI factory provided Motherboard FPGA installed on the board. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Operational Settings: |

The motherboard FPGA firmware version consists of two components: Major, Minor. |

Motherboard FPGA Firmware Version (ex. 0x0005 0008 = 5.8) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Major (ex: 0x0005 = 5) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Minor (ex: 0x0008 = 8) |

|||||||||||||||

Motherboard FPGA Compile Date/Time

Edit this on GitLab

Function: |

Specifies the Compile Date/Time of the NAI factory provided Motherboard FPGA installed on the board. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

N/A |

Read/Write: |

R |

Operational Settings: |

The motherboard firmware time consists of the Build Date and Time in the following format: |

Motherboard FPGA Compile Time (ex. 0xD12A 01B8 = 02/26/21 00:06:56) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Day (D31:D27) |

Month (D26:D23) |

Year (D22:D17) |

|||||||||||||

ex. 0xD |

ex. 0x1 |

0x2 |

0xA |

||||||||||||

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

Day = 0x1A = 26 |

Month = 0x2 = 2 |

Year = 0x15 = 21 |

|||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Hour (D16:D12) |

Minutes (D11:D6) |

Seconds (D5:D0) |

|||||||||||||

ex. 0x0 |

ex. 0x1 |

ex. 0xB |

ex. 0x8 |

||||||||||||

Hour = 0x00 = 0 |

Minutes = 0x06 = 06 |

Seconds = 0x38 = 56 |

|||||||||||||

Motherboard Monitoring Registers

The registers in this provide motherboard voltage and temperature measurement information.

Temperature Readings Register

Edit this on GitLab

The temperature registers provide the current, maximum (from power-up) and minimum (from power-up) for the processor and PCB for UltraScale processor.

These registers are only available on Xilinx Generation 5 platforms, and are periodically populated by the motherboard core application, which only runs in Petalinux and BareMetal. For other operating systems, refer to the naibrd Software Support Kit (SSK) naibsp_system_Monitor_Temperature_Get() routine to manually retrieve the temperature (NOTE: this feature is typically utilized for development/factory use only; contact the factory for additional details on potential use, if required).

Function: |

Specifies the Measured Temperatures on Motherboard. |

Type: |

signed byte (8-bits) for each temperature reading - Six (6) 32-bit words |

Data Range: |

0x0000 0000 to 0xFFFF 0000 |

Read/Write: |

R |

Initialized Value: |

Value corresponding to the measured temperatures based on the table below. |

Operational Settings: |

The 8-bit temperature readings are signed bytes. For example, if the following register contains the value 0x2B2B 0000: |

Example:

Word 1 (UltraScale Temperatures) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

UltraScale Core Temperature |

UltraScale PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

The values would represent the following temperatures:

Temperature Measurements |

Data Bits |

Value |

Temperature (Celsius) |

UltraScale Core Temperature |

D31:D24 |

0x2B |

+43° |

UltraScale PCB Temperature |

D23:D16 |

0x2B |

+43° |

Temperature Readings |

|||||||||||||||

Word 1 (UltraScale Temperatures) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

UltraScale Core Temperature |

UltraScale PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

Word 2 (Reserved) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0x00 |

0x00 |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

Word 3 (Max UltraScale Temperatures) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Max UltraScale Core Temperature |

Max UltraScale PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

Word 4 (Reserved) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0x00 |

0x00 |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Word 5 (Min UltraScale Temperatures) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Min UltraScale Core Temperature |

Min UltraScale PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Word 6 (Reserved) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0x00 |

0x00 |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

00 |

Higher Precision Temperature Readings Registers

These registers provide higher precision readings of the current UltraScale Core and PCB temperatures.

Higher Precision UltraScale Core Temperature |

|

Function: |

Specifies the Higher Precision Measured UltraScale Core temperature on Motherboard Board. |

Type: |

signed word (16-bits) for integer part and unsigned word (16-bits) for fractional part |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Measured UltraScale Core temperature on Motherboard Board |

Operational Settings: |

The upper 16-bits represent the signed integer part of the temperature, and the lower 16-bits represent the fractional part of the temperature with the resolution of 1/1000 of degree Celsius. For example, if the register contains the value 0x002B 0271, this represents UltraScale Core Temperature = 43.625° Celsius, and value 0xFFF6 0177 represents -10.375° Celsius. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Signed Integer Part of Temperature |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Fractional Part of Temperature |

|||||||||||||||

Higher Precision Motherboard PCB Temperature |

|

Function: |

Specifies the Higher Precision Measured Motherboard PCB temperature. |

Type: |

signed word (16-bits) for integer part and unsigned word (16-bits) for fractional part |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Measured Motherboard PCB temperature |

Operational Settings: |

The upper 16-bits represent the signed integer part of the temperature and the lower 16-bits represent the fractional part of the temperature with the resolution of 1/1000 of degree Celsius. For example, if the register contains the value 0x0020 007D, this represents Interface PCB Temperature = 32.125° Celsius, and value 0xFFE8 036B represents -24.875° Celsius. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Signed Integer Part of Temperature |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Fractional Part of Temperature |

|||||||||||||||

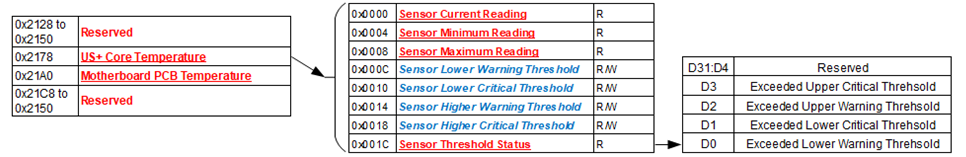

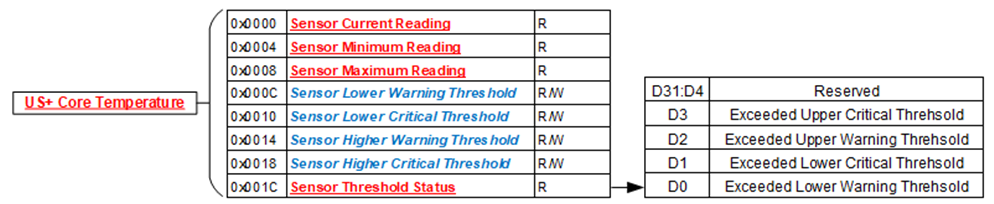

Motherboard Health Monitoring Registers

The registers in this section provide a summary of motherboard temperature sensors and their corresponding bits. Additionally, this section provides an overview of the registers allocated to those sensors, which are used to monitor current/minimum/maximum temperature readings, upper & lower critical/warning temperature thresholds, and whether or not a programmed temperature threshold has been exceeded.

These registers are only available on Xilinx Generation 5 platforms, and are periodically populated by the motherboard core application, which only runs in Petalinux and BareMetal. For other operating systems, refer to the naibrd Software Support Kit (SSK) naibsp_system_Monitor_Temperature_Get() routine to manually retrieve the temperature (NOTE: this feature is typically utilized for development/factory use only; contact the factory for additional details on potential use, if required).

Motherboard Sensor Summary Status |

|

Function: |

The corresponding sensor bit is set if the sensor has crossed any of its thresholds. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table below |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

This register provides a summary for motherboard sensors. When the corresponding sensor bit is set, the Sensor Threshold Status register for that sensor will indicate the threshold condition that triggered the event. |

Bit(s) |

Sensor |

D31:D5 |

Reserved |

D4 |

Motherboard PCB Temperature |

D3 |

US+ Core Temperature |

D2:D0 |

Reserved |

Motherboard Sensor Registers

Edit this on GitLab

The registers listed in this section apply to each module sensor listed for the Motherboard Sensor Summary Status register. Each individual sensor register provides a group of registers for monitoring motherboard temperatures readings. From these registers, a user can read the current temperature of the sensor in addition to the minimum and maximum temperature readings since power-up. Upper and lower critical/warning temperature thresholds can be set and monitored from these registers. When a programmed temperature threshold is crossed, the Sensor Threshold Status register will set the corresponding bit for that threshold. The figure below shows the functionality of this group of registers when accessing the Zynq Core Temperature sensor as an example.

Sensor Threshold Status |

|

Function: |

Reflects which threshold has been crossed |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table below |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

The associated bit is set when the sensor reading exceed the corresponding threshold settings. |

Bit(s) |

Description |

D31:D4 |

Reserved |

D3 |

Exceeded Upper Critical Threshold |

D2 |

Exceeded Upper Warning Threshold |

D1 |

Exceeded Lower Critical Threshold |

D0 |

Exceeded Lower Warning Threshold |

Sensor Current Reading |

|

Function: |

Reflects current reading of temperature sensor |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

The register represents current sensor reading as a single precision floating point value. For example, for a temperature sensor, register value 0x41C6 0000 represents temperature = 24.75° Celsius. |

Sensor Minimum Reading |

|

Function: |

Reflects minimum value of temperature sensor since power up |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R |

Initialized Value: |

N/A |

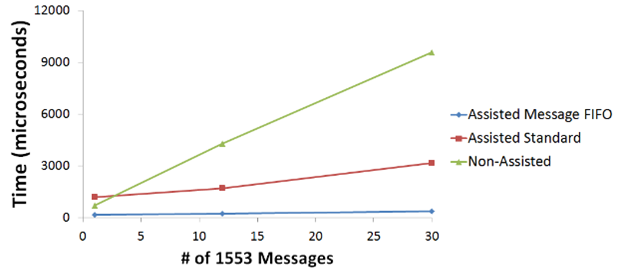

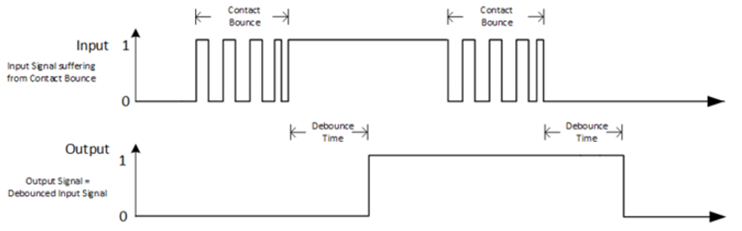

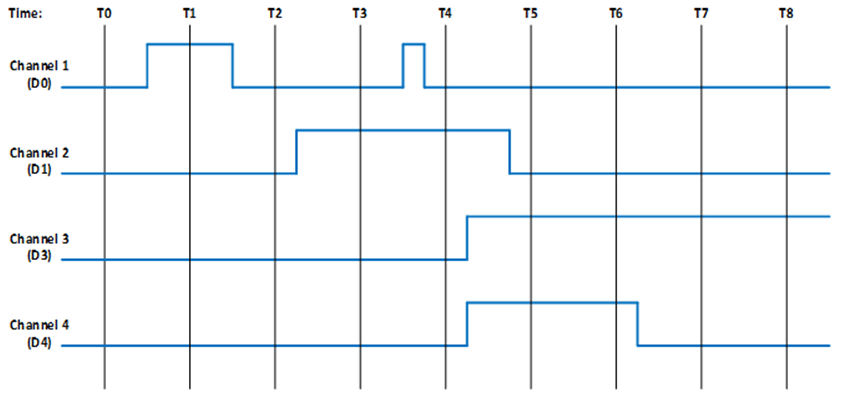

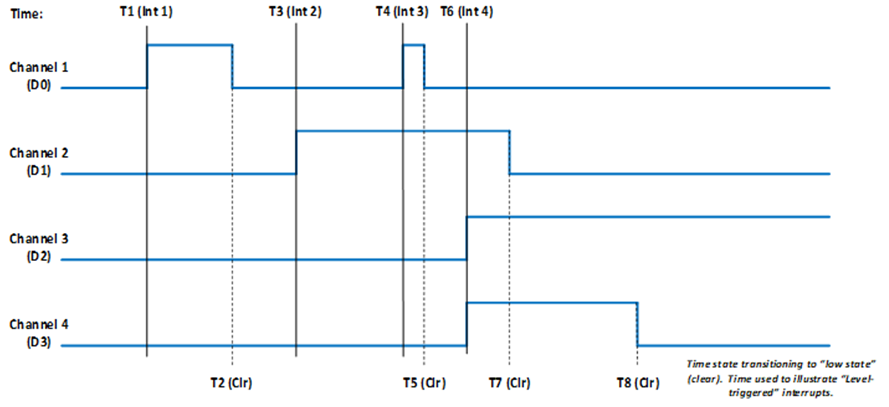

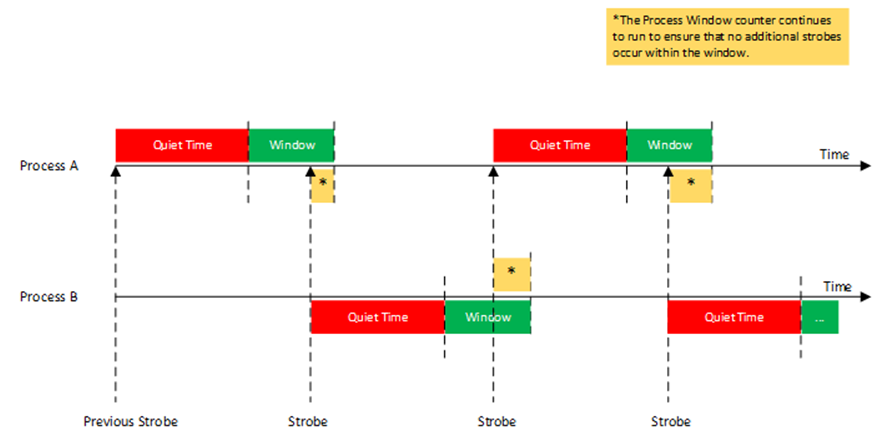

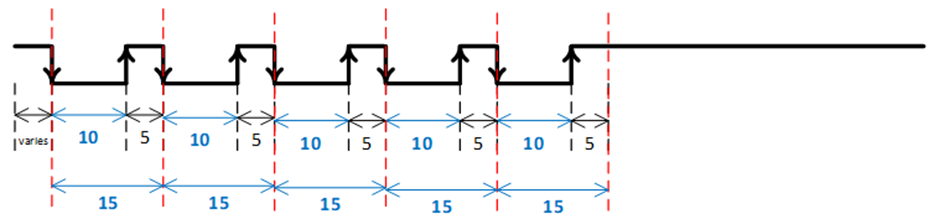

Operational Settings: |