LD1-LD5 Manual

Edit this on GitLab

INTRODUCTION

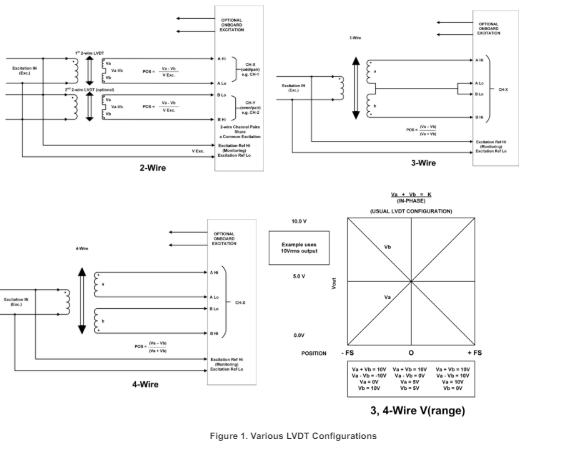

This module manual provides information about the North Atlantic Industries, Inc. (NAI) LVDT or RVDT Function Modules: LD1-LD5. These modules are compatible with all NAI Generation 5 motherboards.

Modules LD1, LD2, LD3, LD4, and LD5 provide Linear Variable Differential Transformer (LVDT) or Rotary Variable Differential Transformer (RVDT) measurement. An LVDT is a type of electrical transformer/transducer used for measuring linear displacement (position). The RVDT is like an LVDT in that it measures a positional displacement, however, the displacement, which is still a linear proportional function, is based on rotary instead of linear positional movement. Both types provide output signals (voltages) as a proportional linear function based upon an AC Reference source. The AC Reference source applied at the transformer primary winding causes a magnetic flux generated on the transformer secondary windings by a moveable core, which causes output signal(s) proportional to the linear displacement position being gauged.

Both deliver signals proportional to the linear displacement of the moveable core. LD1-LD5 convert these signals to a digital output corresponding to position. See the following table for each model’s operating parameters.

For the remainder of this document, LVDT and RVDT acronyms may be used interchangeably as the fundamental operation and interface for both are essentially the same.

Module ID |

No. of Ch. |

Description |

LD1 |

4 |

2-28 Vrms Input, 47 Hz -1 KHz |

LD2 |

4 |

2-28 Vrms Input, 1 KHz - 5 KHz |

LD3 |

4 |

2-28 Vrms Input, 5 KHz - 10 KHz |

LD4 |

4 |

2-28 Vrms Input, 10 KHz - 20 KHz |

LD5 |

4 |

28-90 Vrms Input, 47 Hz - 1 KHz |

FEATURES

-

With isolated excitation and signal input covering 2, 3, or 4-wire transducer interfaces and a normalized digital position word based on a percentage of full-scale travel, the LVDT/RVDT modules are able to interface to virtually any type LVDT or RVDT transformer.

-

The channels include many other useful application features such as signal, reference, and frequency measurements as well as signal under- and over-voltage detection, and reference under- and over-voltage detections.

-

All channels have continuous background Built-In-Test (BIT).

-

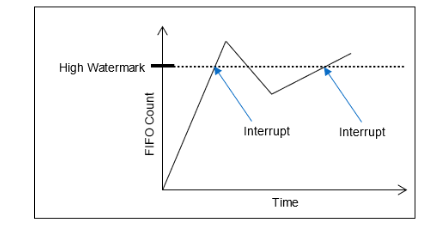

The modules also include extended LVDT FIFO buffering capabilities for greater storage/management of the incoming signal samples (data) for post processing applications. Programmable FIFO buffer thresholds maximize data flow control (in and out of the FIFO).

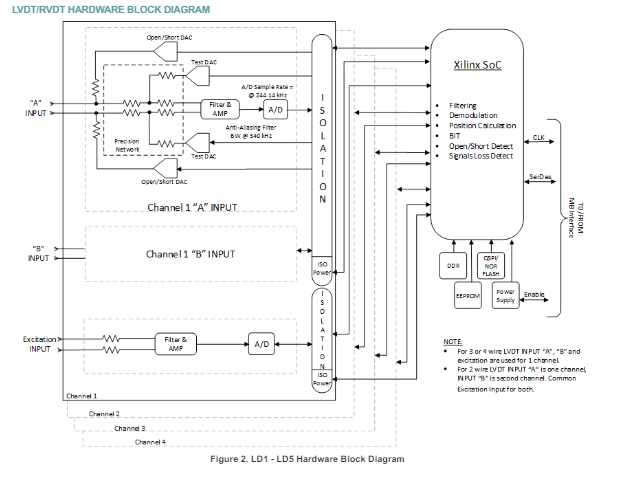

PRINCIPLE OF OPERATION

The modules cover a wide range of reference voltages/frequencies, so they can interface to almost any transducer. With isolated reference and signal input covering 2-, 3-, or 4-wire transducer interfaces and a normalized digital position word based on a percentage of full-scale travel, these modules can interface to virtually any type LVDT or RVDT transformer.

The conversion of input signals to position is performed as a tracking, ratio-metric calculation. This conversion uses phase sensitive demodulation, and band limiting techniques. This enhances the accuracy and performance by reducing the sensitivity to the noise and quadrature, in the input signals (caused by stray capacitive coupling, in the wiring.).

Two common connection methods are:

-

Primary as reference (2-wire system)

-

Derived reference (3- or 4-wire system)

Figure 1. Various LVDT Configurations

2-Wire System

In a 2-Wire LVDT system, when the primary coil is excited with an excitation voltage (Excitation IN), this voltage produces a current in the windings (function of the input impedance). The variable current generates a variable magnetic flux which induces voltages in the secondary windings, Va and Vb, as a function of the core position The secondary windings are connected in series to produce the differential voltage Va - Vb. The amplitude of the differential output voltage (Va-Vb) is proportional to the core position. The phase of (Va-Vb) with respect to the excitation, is typically 5 to 10 deg, and is usually specified by the manufacture.

The 2-Wire LVDT system allows the minimum numbers of electrical connections to the LVDT, as only 4 are required (2 for the excitation and 2 for the differential output). In this configuration (refer to Figure 1), connect “a-b” LVDT output to Signal A (A HI and A LO) and the Excitation-toExcitation Ref Hi and Excitation Ref Lo.

This Excitation signal will be scaled by the value in the Transformation Ratio (TR) Value register, to adjust the full-scale value of the output position to +/- 100%. The Excitation signal will also be phase compensated with the phase shift in the phase shift register. This will reduce the sensitivity to Quadrature signals caused by the system wiring and null voltage of the LVDT. The Position of the LVDT will be calculated as the ratio of the Signal A to this adjusted Excitation signal. This excitation signal is monitored for signal level and the converter will report if signal level is not within levels specified in reference level registers.

Some of the drawbacks of the 2 Wire LVDT system are the variation in TR and Phase Shift from LVDT to LVDT and over temperature can produce degraded positional accuracies.

In a 2-Wire LVDT system the position is measured as (Va-Vb) / (TR * VEXCITATION )

Where TR is the transformation ratio of the LVDT, specified by manufacturer.

This position ratio is determined using a tracking algorithm that is Phase sensitive, which rejects the null error signal, as well as errors from quadrature signals caused by coupling, in the system wiring. The phase information is derived from the Excitation Ref inputs. Programmable fixed phase shift compensation is provided.

This algorithm is also bandwidth limited to reduce errors due to noise in input signals. The bandwidth is programmable to allow users to increase filtering in noisy environments.

Operational Note:

Programming a channel for 2-wire mode essentially doubles the channel count by 'splitting' independent channels into two separate, ACReference (Excitation) dependent channel pairs.

Example: Independent channel CHx is “split” into dependent channel pairs: CHxA & CHxB. 2-wire mode channel pairs require and expect to use the single CHx REF Hi/Lo inputs. Since these channel pairs are dependent, any LVDT operating characteristic parameters must be consistent with the common AC Reference (Excitation) source which is applied to each of the channel pairs.

Each channel of a channel pair can interface to independent LVDTs and provide two independent position (and signal) related measurements. However, because the same AC Reference (Excitation) source is applied and is being utilized by both channels of the pair, it is also implied that the programmable characteristics of the channel pairs must be the same. In other words, LVDT characteristics (e.g., transformation ratio (TR)) must be the same for the CHxA and CHxB). Therefore, there is no “B-side” TR register; as the channel B-side of the pair will use the same programmed TR as the “A-side”.

For operational consistency, it is recommended that the independent LVDTs interfaced to the 2-wire mode channel pairs are of the same model/type with similar operating characteristics.

3-Wire or 4-Wire System

In 3-Wire and 4-Wire LVDT systems, the LVDT is designed to maintain a constant sum of the secondary voltages (Va+Vb) over the measuring stroke length. This allows the system to be insensitive to temperature effects, phase shifts and oscillator instability.

In the 3-Wire configuration (refer to Figure 1), connect the “a” and “b” (Hi) LVDT outputs to the A HI and B HI inputs respectively and the common center tap (“a” and “b” (Lo)) to A LO and B LO inputs.

In the 4-Wire configuration (refer to Figure 1), connect the “a” (Hi, Lo) outputs to A HI and A LO and “b” (Hi, Lo) outputs to B HI and B LO.

Note that the Reference is not used in calculating the position but should be connected to enable the channel to initially phase lock to the excitation voltage, and to monitor and report if the Reference level is not within levels specified in reference level registers.

In a 3-Wire and 4-Wire LVDT system the position is measured as (Va-Vb) / (Va+Vb).

This position ratio is determined using a tracking algorithm that is Phase sensitive, which rejects the null error signal, as well as errors from quadrature signals caused by coupling, in the system wiring. The phase information is derived from the ( Va + Vb ) signal

This algorithm is also bandwidth limited to reduce errors due to noise in input signals. The bandwidth is programmable to allow users to increase filtering in noisy environments.

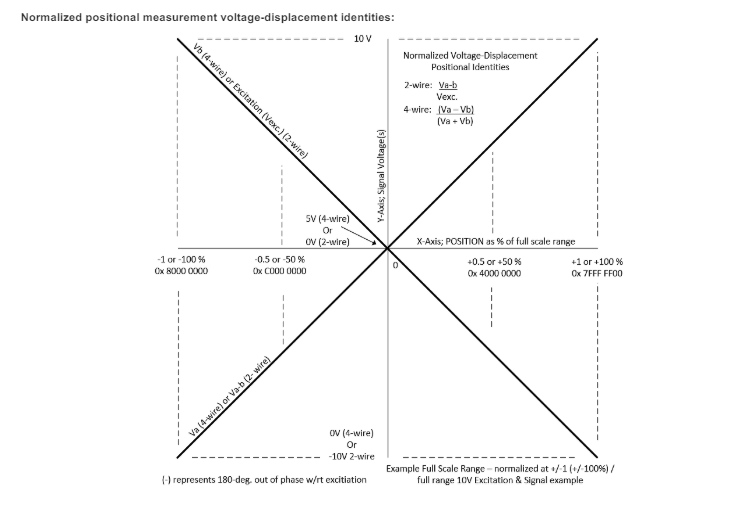

Position Measurement

The LVDT/RVDT channels measure the LVDT position as a percentage of full-scale coupling (+/- FS) If the coupling is limited by the linear range of the LVDT, the output can be scaled to indicate full scale travel at a limited coupling position, with the use of the LVDT/RVDT scaling register. i.e., 85 % coupling can be scaled to indicate 100 % travel position.

3 or 4-wire configured channels provide a single LVDT position. 2-wire configured channels can provide two independent LVDT positions, as long as they share the same excitation signal. it reads the position of the signal on the “Va” input as Position A and “Vb” input as Position B

Velocity Measurement

The conversion of input signals to position is performed using a tracking algorithm. This algorithm produces a value that is proportional to the rate of change of the Output position. This value is supplied as the velocity of the output and is updated at every sample time.

Bandwidth Setting

The conversion of input signals to position is performed using a bandlimited tracking algorithm. The Bandwidth of this algorithm can be set manually or set automatically by the internal processor. Settings are from 2 Hz up to 1280 Hz. Auto Bandwidth mode will set the bandwidth to 1/10 of the excitation frequency up to 1280 Hz.

Signal/Reference Measurements

The Signal and Excitation RMS values (10 mV resolution) are available as well as the Excitation Frequency (1 Hz resolution).

Built-In Test (BIT)/Diagnostic Capability

The board supports three types of built-in tests: Power-On, Continuous Background and Initiated. The results of these tests are stored in the BIT Dynamic Status and BIT Latched Status registers.

Power-On Self-Test (POST)/Power-on BIT (PBIT)/Start-up BIT (SBIT)

This board features a power-on self-test that will do an accuracy check of each channel and report the results in the BIT Status register when complete. After power-on, the Power-on BIT Complete register should be checked to ensure that POST/PBIT/SBIT test is complete before reading the BIT Latched Status.

Continuous Background Built-In Test

All LVDT/RVDT measurement modules feature a background self-test capability or Continuous BIT (CBIT) (“D2”) test. The modules incorporate major diagnostics that ensure that the user is alerted to channel malfunction. This approach reduces bus traffic because the Status Registers need not be constantly polled. In addition to specialized design algorithms, the modules include many other useful applications features such signal voltage, reference voltage and frequency measurements, reference low/high (under-/over-voltage) fault detection, and signal low/high (under-/over-voltage) fault detection.

The CBIT test enables reporting of automatic background BIT (accuracy) testing. Seamlessly and transparently, each channel is in the “background” while operating normally to a default accuracy tolerance of 0.1% full-scale range. Any channel exceeding the tolerance is flagged in the BIT Status registers. The testing is totally transparent to the user, requires no external programming, and has no effect on the standard operation of the module. This test checks 72 unique positions for each channel sequentially and can take approximately 2 minutes to complete. Each position cycles through all 4 channels within 1.65 seconds. The user can verify that the background BIT testing is executing by writing a value other than 0x0055 to the Test CBIT Verify register and then reading the Test CBIT Verify register after 10ms. The value reported back will be 0x0055 while the background bit testing is active.

In addition to the above accuracy tests, Signal Fault Low Status, Reference Fault Low Status, Signal Fault High Status, Reference Fault High Status, and Delta Position are always being monitored.

Initiate Built-In Test

The LVDT/RVDT module support two off-line Initiated Built-in Test, User Initiated BIT (UBIT) (“D0”) and Initiated BIT (IBIT) (“D3”).

UBIT is used to check the channel functionality without the need for external sources. All channels use an internal source to simulate LVDT positions that the user can set and then to read the data from the interface. All channels acquire data from this internal source. External reference is not required.

IBIT test starts an initiated BIT test that utilizes an internal stimulus to generate and test the full-scale positional range to a default test accuracy of 0.1% full scale range. IBIT test cycle is completed within 30 seconds and the result can be read from the BIT status registers when IBIT bit changes from 1 to 0.

|

Note

|

UBIT and IBIT tests only check the accuracy of the LVDT/RVDT channels and are individual tests and will not operate concurrently. For example, if the UBIT mode is set, and the user would like to perform the IBIT test, the UBIT mode must be stopped (inactive) before the IBIT test will run. The same holds true when the IBIT test is active. For the UBIT test to be activated, the user must disable the IBIT test. The CBIT test, however, can be set and the board can still perform with either the UBIT or IBIT tests. The CBIT test will momentarily stop while either of these tests are active and will return when the tests have completed. |

|

Note

|

the default error limit that the BIT tests check to is 0.1%. The user has the option to program their own limits, per channel, by writing to the BIT Error Limit registers. There is on BIT Error Limit register per channel and is expressed as an IEEE-754 floating point number. |

LVDT/RVDT Threshold Programming

In addition to Built-in Tests, the LVDT/RVDT modules provide the ability to monitor Signal faults (under and over-voltage conditions), Reference faults (under and over-voltage conditions), and Open detects.

LVDT/RVDT FIFO Buffering

The LVDT/RVDT modules include LVDT/RVDT FIFO Buffering for greater control of the incoming signal (data) for analysis and display. When initialized and triggered, the LVDT/RVDT buffer will accept/store the data at the same rate specified in the FIFO Sample Rate register. Programmable buffer sample thresholds can be utilized for data flow control.

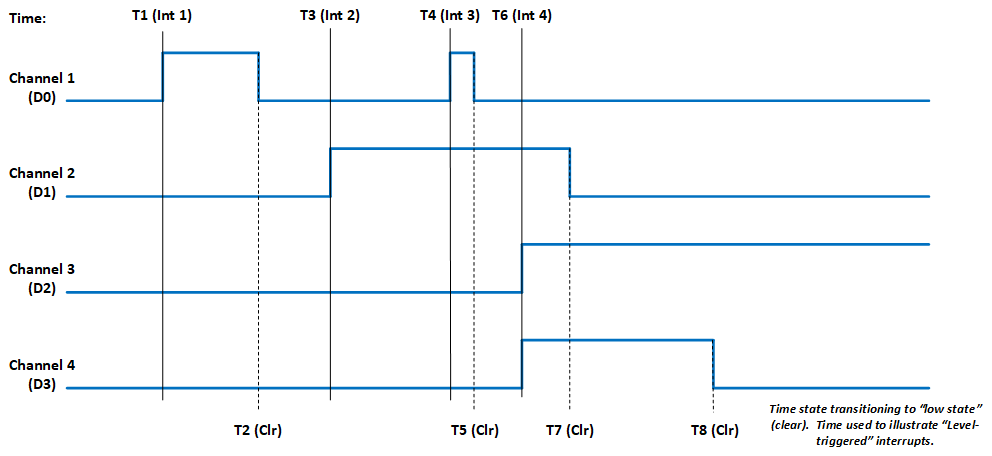

Status and Interrupts

The LVDT/RVDT Modules provide registers that indicate faults or events. Refer to “Status and Interrupts Module Manual” for the Principle of Operation description.

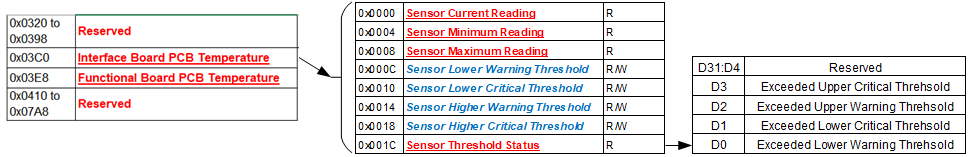

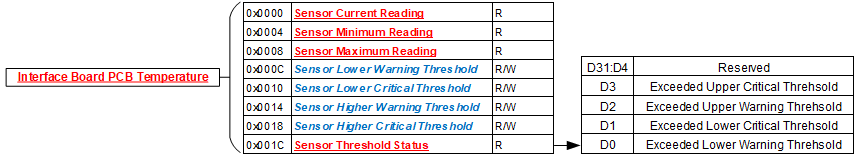

Module Common Registers

The LVDT/RVDT Modules include module common registers that provide access to module-level bare metal/FPGA revisions & compile times, unique serial number information, and temperature/voltage/current monitoring. Refer to “Module Common Registers Module Manual” for the detailed information.

Engineering Scaling Conversions

The LVDT/RVDT Threshold and Measurement registers can be programmed to be utilized as Single Precision Floating Point Value (IEEE-754) values or as 32-bit integer values. There are separate floating-point scale and offset registers for position, velocity, 2-wire position “B-side”, and 2- wire velocity “B-side” for each channel.

It is very often necessary to convert LVDT reading into a more useful value such as inches, etc. For example, when measuring distance, it would be more beneficial to read the data as inches instead of percentage of full scale. When the Enable Floating Point Mode register is set to 1, the values entered for the Floating Point Scale register and Floating Point Offset register will be used to convert the data (i.e., LVDT Position and Velocity Data and FIFO Buffer Data registers) to the associated engineering unit as follows:

LVDT Data in Engineering Units (Floating Point) =

(LVDT Value (Volts/Current) * Floating Point Scale) + Floating Point OffsetLVDT Data in Engineering Units (Floating Point) =

(LVDT Value (Percentage of Full-Scale) * Floating Point Scale) + Floating Point Offset

The purpose for providing this feature is to offload the processing that is normally performed by the mission processor to convert the integer values to engineering unit values. When the Enable Floating Point Mode register is set to 1 (Floating Point Mode) the following registers are formatted as Single Precision Floating Point Value (IEEE-754):

-

Position Data

-

Velocity Data

-

Measured Reference RMS Voltage

-

Measured Signal RMS Voltage

-

Measured Frequency

-

FIFO Buffer Data

-

Threshold Detect Level* (Signal Faults, Reference Faults)

-

UBIT Test Position*

-

Delta Position*

*When the Enable Floating Point Mode register is set to 1, it is important that these registers are updated with the Single Precision Floating Point (IEEE-754) representation of the value for proper operation of the channel. Conversely, when the Enable Floating Point Mode register is set to 0, these registers must be updated with the Integer 32-bit representation of the value.

|

Note

|

When changing the Enable Floating Point Mode from Integer Mode to Floating Point Mode or vice versa, the following step should be followed to avoid faults from falsely being generated because data registers (such as Thresholds) or internal registers may have the incorrect binary representation of the values: |

-

Set the Enable Floating Point Mode register to the desired mode (Integer = 0 or Floating Point = 1).

-

Wait for the Floating Point State register to match the value for the requested Floating Point Mode (Integer = 0, Floating Point = 1); this indicates that the module’s conversion of the register values and internal values is complete. Data registers will be converted to the units specified and can be read in that specified format.

-

Initialize configuration and control registers with the values in the units specified (Integer or Floating Point).

The following registers are formatted as Single Precision Floating Point Value (IEEE-754) regardless of the value in the Enable Floating Point Mode register:

-

Va, Vb, Va+Vb RMS Voltages

-

Va, Vb Detect Values

-

Open and Short Detect Thresholds

-

BIT Error Limit

-

Position and Velocity Floating Point Scales and Offsets

REGISTER DESCRIPTIONS

The register descriptions provide the register name, Type, Data Range, Read or Write information, Initialized Value, a description of the function and, in most cases, a data table.

LVDT/RVDT Measurement Registers

When the Enable Floating Point Mode is enabled, the register values are formatted as Single Precision Floating Point Value (IEEE-754) values. In addition, the Floating-Point Scale and register Floating Point Offset will be applied to convert the position value to engineering units.

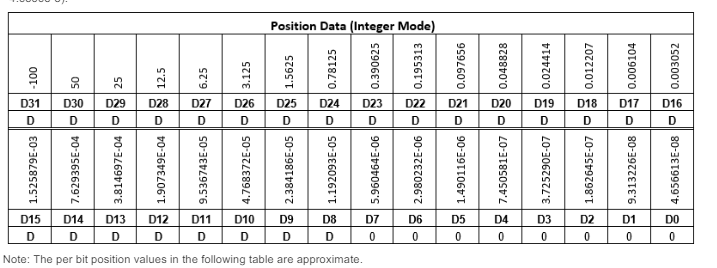

Position Data

Function: The value represents the position as a percentage of full scale (FS) in each channel for 3-Wire or 4-Wire applications. In 2-wire mode, the value is the position of the signal on the “Va” input with respect to the reference. The value for the position of the signal on “Vb” input with respect to the reference is stored in the Position B_2W register.

Type: signed binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: -100% to +100%

Integer Mode (Enable Floating Point Mode register = 0)

32-bit two’s complement (Lower 8 bits fixed at “0”)

-Full Scale (0x8000 0000) to +Full Scale (0x7FFF FF00)

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: N/A

Operational Settings:

Integer Mode:

Data Format (2-Wire): The value is computed as Va / REF and represents a % of ± Full Scale (FS). This value is formatted as a two’s complement value. The maximum positive excursion is 0x7FFF FF00, 0 = 0x0000 0000, and the maximum negative excursion is 0x8000 0000.

Data Format (3-Wire/4-Wire): The value is computed as (Va-Vb) / (Va+Vb) and represents a % of ±FS. This value is formatted as a two’s complement value. The maximum positive excursion is 0x7FFF FF00, 0 = 0x0000 0000, and the maximum negative excursion is 0x8000 0000.

-100 |

50 |

25 |

12.5 |

6.25 |

3.125 |

1.5625 |

0.78125 |

0.390625 |

0.195313 |

0.097656 |

0.048828 |

0.024414 |

0.012207 |

0.006104 |

0.003052 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

1.525879E-03 |

7.629395E-04 |

3.814697E-04 |

1.907349E-04 |

9.536743E-05 |

4.768372E-05 |

2.384186E-05 |

1.192093E-05 |

5.960464E-06 |

2.980232E-06 |

1.490116E-06 |

7.450581E-07 |

3.725290E-07 |

1.862645E-07 |

9.313226E-08 |

4.656613E-08 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

D |

D |

D |

D |

D |

D |

D |

D |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Note

|

The per bit position values in the following table are approximate. |

Floating Point Mode:

Read as Single Precision Floating Point Value (IEEE-754).

Velocity Data

Function: The value represents the constant velocity for each channel in for 3-Wire or 4-Wire. In 2-Wire mode, the value is the velocity of the “Va” input signal. The value for the velocity of the “Vb” input signal is stored in the Velocity B_2W register.

Type: signed binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: +/-100.0% / sec

Integer Mode (Enable Floating Point Mode register = 0)

-32-bit two’s complement

-Full Scale (0x8000 0000) to +Full Scale (0x7FFF FFFF)

Floating Point Mode (Enable Floating Point Mode register = 1)

-Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: N/A

Operational Settings:

Integer Mode:

Velocity registers of each channel are read as a two’s complement word when in “integer” mode, with 0x7FFF FFFF being maximum in positive velocity, and 0x8000 0000 being maximum negative velocity. Units are in decimal-percent/second

Va RMS

Function: The value represents the RMS value of the “Va” input.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: 0.0 to 30.0

Read/Write: R

Initialized Value: N/A

Operational Settings: N/A

Vb RMS

Function: The value represents the RMS value of the “Vb” input.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: 0.0 to 30.0

Read/Write: R

Initialized Value: N/A

Operational Settings: N/A

Position B_2W

Function: The value represents the position of the signal on the “Vb” input with respect to the reference when in 2-Wire mode only.

Type: signed binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: -100% to +100%

Integer Mode (Enable Floating Point Mode register = 0)

32-bit two’s complement (Lower 8 bits fixed at “0”)

-Full Scale (0x8000 0000) to +Full Scale (0x7FFF FF00)

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: N/A

Operational Settings:

Integer Mode:

The value is computed as Vb / REF and represents a % of ± Full Scale (FS). This value is formatted as a two’s complement value. The maximum positive excursion is 0x7FFF FF00, 0 = 0x0000 0000, and the maximum negative excursion is 0x8000 0000.

-100 |

50 |

25 |

12.5 |

6.25 |

3.125 |

1.5625 |

0.78125 |

0.390625 |

0.195313 |

0.097656 |

0.048828 |

0.024414 |

0.012207 |

0.006104 |

0.003052 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

1.525879E-03 |

7.629395E-04 |

3.814697E-04 |

1.907349E-04 |

9.536743E-05 |

4.768372E-05 |

2.384186E-05 |

1.192093E-05 |

5.960464E-06 |

2.980232E-06 |

1.490116E-06 |

7.450581E-07 |

3.725290E-07 |

1.862645E-07 |

9.313226E-08 |

4.656613E-08 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

D |

D |

D |

D |

D |

D |

D |

D |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Note

|

The per bit position values in the following table are approximate. |

Floating Point Mode:

Read as Single Precision Floating Point Value (IEEE-754).

Velocity B_2W

Function: The value represents the velocity of the signal on the “Vb” input with respect to the reference when in 2-Wire mode only.

Type: signed binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range:

Integer Mode (Enable Floating Point Mode register = 0)

32-bit two’s complement

-Full Scale (0x8000 0000) to +Full Scale (0x7FFF FFFF)

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: N/A

Operational Settings:

Integer Mode:

Velocity registers of each channel are read as a two’s complement word when in “integer” mode, with 0x7FFF FFFF being maximum in positive velocity, and 0x8000 0000 being maximum negative velocity. Units are in decimal-percent/second.

Floating Point Mode:

Read as Single Precision Floating Point Value (IEEE-754).

Measured Reference (RMS)

Function: Measures individual channel input reference voltage.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0-140

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: N/A

Operational Settings:

Integer Mode:

Read integer value and multiply value by LSB (10 mV) to compute the reference voltage.

Floating Point Mode:

Read as Single Precision Floating Point Value (IEEE-754).

Measured Frequency (Hz)

Function: Measures individual channel input reference frequency.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0-20 kHz

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 1 Hz.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: N/A

Operational Settings: Each individual channel input reference frequency is measured, and the value is reported to a corresponding register.

Integer Mode:

The integer value represents the reference frequency in Hz.

Floating Point Mode:

Read as Single Precision Floating Point Value (IEEE-754).

Va Detect Value

Function: Reports a numeric value based on the connection status of the Va input from the LVDT/RVDT.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: 0 to 200,000

Read/Write: R

Initialized Value: N/A

Operational Settings: This register will display a value typically in the hundreds when the LVDT/RVDT is connected normally and is functional. If one of the inputs, Va(hi) or Vb(lo) is disconnected from the LVDT, this value will increase into the thousands. If the Va and Vb winding is shorted, the value will be close to “0”. This value is used in comparison with the Open and Short Detect threshold values to alert the user of a faulty connection.

Vb Detect Value

Function: Reports a numeric value based on the connection status of the Vb input from the LVDT/RVDT.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: 0 to 200,000

Read/Write: R

Initialized Value: N/A

Operational Settings: Refer to Va Detect Value register description.

3- or 4-Wire Specific Register

The following registers apply when the LVDT is configured for 3- or 4-Wire mode.

Measured Signal (RMS)

Function: The value represents the total sum RMS value of the “Va” and “Vb” signals added together regardless of phase.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0-60

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: N/A

Operational Settings: Note: In 3- or 4-Wire mode, this should be a constant output corresponding to the LVDT/RVDT output windings. In 2-Wire mode, the value is not applicable since it includes both the “A” & “B” sides.

Integer Mode:

Read integer value and multiply value by LSB (10 mV) to compute the signal voltage.

Floating Point Mode:

Read as Single Precision Floating Point Value (IEEE-754).

Va+Vb RMS

Function: The value represents the total sum RMS value of the “Va” and “Vb” signals added together regardless of phase.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: 0.0 to 60.0

Read/Write: R

Initialized Value: N/A

Operational Settings: Applicable when in 3-Wire or 4-Wire Mode. In 3- or 4-Wire mode, this should be a constant output corresponding to the LVDT/RVDT output windings. In 2-Wire mode, the value is not applicable since it includes both the “A” & “B” sides.

LVDT/RVDT Control Registers

The LVDT/RVDT control registers provide the ability to specify the mode, LVDT/RVDT scaling and bandwidth. In addition, there are control registers that provide the ability to normalize the reference input voltage to the signal voltage, the ability to invert the Va, Vb, or excitation voltage, as well as the ability to specify the position measurement algorithm.

Mode Select

Function: Configures for 3-Wire/4-Wire or 2-Wire LVDT/RVDT signal format measurement.

Type: unsigned binary word (32-bit)

Data Range: See table.

Read/Write: R/W

Initialized Value: 0x0000 0001

Operational Settings: Set the Mode as specified in the table.

Mode Select Value |

Description |

1 |

3-Wire/4-Wire |

2 |

2-Wire |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Mode |

Mode |

LVDT/RVDT Scale

Function: This register will allow the user to scale the LVDT/RVDT output to represent full scale.

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0xFFFF FFFF

Read/Write: R/W

Initialized Value: 0xFFFF FFFF

Operational Settings: Used only for Integer mode. When set to 0xFFFF FFFF, it represents a scale of '1'. If the user wants to set the channel to represent +/- 100% with less than full excursion of the LVDT, this register needs to be adjusted.

TR Value (Transformation Ratio Value)

Function: This register will allow the user to normalize the Reference input to the Signal output (“A” side and “B” side). This is only applicable in 2-wire mode and should not be modified from the default value while in 3/4 wire mode.

Type: unsigned binary word (32-bit)

Read/Write: R/W

Initialized Value: 0xFFFFFFFF

Operational Settings:

Example: If the Reference voltage is 10V and the LVDT/RVDT outputs 10V at full excursion (full scale), then the ratio between the reference and the signal is 1:1 and this value would be at 0xFFFFFFFF. If, however, the LVDT/RVDT under test has a reference voltage of 6V applied and it produces a full-scale voltage of 4V, then the TR value should be set to 0xAAAAAAAA (4V / 6V). This will allow the module to normalize the output of the LVDT/RVDT to the reference so that the position will be reported correctly.

Bandwidth Select

Function: Sets the bandwidth control to use. Bandwidth settings can be set manually or automatically by the module’s internal processor.

Type: unsigned binary word (32-bit)

Data Range: 0 to 1

Read/Write: R/W

Initialized Value: 0

Operational Settings: Set to Manual (0) to use the value in the Bandwidth register. Set to Automatic (1) to have the module automatically set the bandwidth will be set to 1/10 of the excitation frequency up to 1280 Hz. The Bandwidth register will contain the calculated bandwidth when in Bandwidth Select is set to automatic. The bandwidth setting will only update when there is a 12.5% change in frequency. For example, if the frequency is at 1Khz and the bandwidth is set to 100hz, a change in frequency less than 125Hz will result in no change to the bandwidth setting.

Bandwidth Select Value |

Description |

0 |

Manual |

1 |

Automatic |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

Bandwidth (Hz)

Function: Sets the bandwidth when the Bandwidth Select register is set for “Manual” or contains the bandwidth set by the module’s internal processor when the Bandwidth Select register is set for “Automatic”.

Type: unsigned binary word (32-bit)

Data Range: 2 to 1280 Hz

Read/Write: R/W

Initialized Value: 40 Hz

Operational Settings: When the Bandwidth Select register is set for “Manual” mode, the bandwidth is programmable, between 2 and 1280 Hz. The LSB is 1 Hz. The resolution is 2Hz. All values greater than 1280 will be processed as 1280Hz. All values less than 2 will be processed as 2 Hz.

|

Note

|

The bandwidth should not be set to more than ¼ of the reference frequency. A higher BW setting will result in a quicker response to a change in position but will be at the expense of greater noise in the reading. A lower BW value will result in a much quieter reading but will take longer to settle. |

When the Bandwidth Select register is set for “Automatic” mode, the bandwidth will be internally calculated and written to this register. The bandwidth value will be set to 1/10 the carrier frequency with a minimum BW of 2 Hz, and a maximum BW of 1280 Hz. The change will occur only when a frequency change of 12.5% or greater is detected as illustrated in the table.

Example: Bandwidth Select = Automatic

Reference Frequency |

Bandwidth Value |

Description |

Current Reference frequency at 400 Hz |

Bandwidth sets to 40Hz |

a 12.5% change would be 50 Hz |

Reference Frequency changes to 12Khz |

Bandwidth sets to 1200Hz |

3000% change from 400Hz |

Reference Frequency changes to 13Khz |

Bandwidth sets to 1200Hz |

8.333% change from 12Khz (not enough to trigger a change) |

Reference Frequency changes to 14Khz |

Bandwidth sets to 1280Hz |

16.666% change from 12Khz |

Delta Position

Function: Sets the value of position change that is required to alert the user that a change has occurred.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0x002D E00D to 0x4000 0000 (Integer mode) or 0.14% to 50% (Floating Point Mode)

Read/Write: R/W

Initialized Value: 0

Operational Settings: Set the minimum differential position to trigger a position change alert.

Integer Mode:

Set the Delta Position based on the bit weighs shown in the table.

-100 |

50 |

25 |

12.5 |

6.25 |

3.125 |

1.5625 |

0.78125 |

0.390625 |

0.195313 |

0.097656 |

0.048828 |

0.024414 |

0.012207 |

0.006104 |

0.003052 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

1.525879E-03 |

7.629395E-04 |

3.814697E-04 |

1.907349E-04 |

9.536743E-05 |

4.768372E-05 |

2.384186E-05 |

1.192093E-05 |

5.960464E-06 |

2.980232E-06 |

1.490116E-06 |

7.450581E-07 |

3.725290E-07 |

1.862645E-07 |

9.313226E-08 |

4.656613E-08 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

D |

D |

D |

D |

D |

D |

D |

D |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Note

|

The per bit position values in the following table are approximate. |

Floating Point Mode:

Set as Single Precision Floating Point Value (IEEE-754).

Initiate Delta Position

Function: Initiates the monitored for position change alert.

Type: unsigned binary word (32-bit)

Data Range: 0 to 1

Read/Write: W

Initialized Value: 0

Operational Settings: Used in conjunction with the Delta Position register. Writing a “1” to the Initiate Delta Position register will capture the current position and use this value to detect a change of +/- the value written in the Delta Position register. If the position exceeds this limit, the corresponding bit in the Delta Position Status registers (Dynamic and Latched) will be set.

|

Note

|

Since the dynamic registers in general give you the current state of the channel, the bit will be set and then cleared within 4.096 µs and might not be observed in the dynamic register. The bit in the Delta Position Latched Status register, however, will remain set until cleared. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

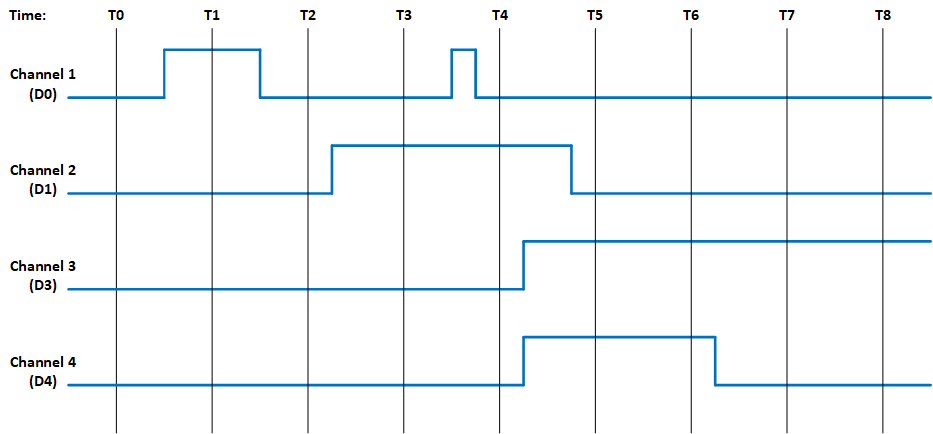

Track/Hold

Function: Latches channels.

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0x0000 000F

Read/Write: R/W

Initialized Value: 0

Operational Settings: Setting the bit for the associated channel to a “1” will latch the data for the corresponding channel. Internally, the channel will continue to track the input, but the data in the Position Data register for the corresponding channel will be latched at the LVDT/RVDT position when the latch was initiated. Once the Position Data register is read, the hardware will disengage the latch for that channel and will continue to update the current LVDT/RVDT position. It will automatically clear the bit associated with the channel. Once set, you can always return to updating the position by clearing the corresponding channel bit.

|

Note

|

This feature can be used to acquire a snapshot of all channels simultaneously. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch.4 |

Ch.3 |

Ch.2 |

Ch1 |

Inverse Signal Control

Function: Enables the inversion of the phase of the Va, Vb and Reference signals. Also enables the changing of the algorithm used for position measurement.

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 - 0x0000 000F

Read/Write: R/W

Initialized Value: 0

Operational Settings: The feature provides the ability to invert the phase of the Va, Vb and Reference signals and change the algorithm used for position measurements.

Bit |

Description |

D3 |

0: Uses (Va - Vb) / (Va + Vb) algorithm; 1: Uses (Vb - Va) / (Va + Vb) |

D2 |

0: Non-Inverted; 1: Inverts Reference |

D1 |

0: Non-Inverted; 1: Inverts Vb |

D0 |

0: Non-Inverted; 1: Inverts Va |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

D |

D |

D |

Threshold Programming Registers

The Signal Fault Low Threshold, Signal Fault High Threshold, Reference Fault Low Threshold, Reference Fault High Threshold, Open Detect Threshold and Short Detect Threshold registers set the threshold limits to the Signal Fault Low Status, Signal Fault High Status, Reference Fault Low Status, Reference Fault High Status, Open Detect Status, and Short Detect Status registers respectively.

Reference Fault Low Threshold

Function: Sets the “under-voltage” threshold at which a fault will be reported in the Reference Fault Low Status register.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0-135 Vrms

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R/W

Initialized Value: 1820 decimal (18.2V)

Operational Settings: The reference fault detection circuitry will report a fault in the Reference Fault Low Status register when the measured reference signal is below the value set in Reference Fault Low Threshold register.

Reference Fault High Threshold

Function: Sets the “over-voltage” threshold at which a fault will be reported in the Reference Fault High Status register.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0-135 Vrms

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R/W

Initialized Value: 2800 decimal (28.00V)

Operational Settings: The reference fault detection circuitry will report a fault in the Reference Fault High Status register when the measured reference signal is above the value set in Reference Fault High Threshold register.

Open Detect Threshold

Function: Sets the threshold at which “open” signal will be reported in the Open Detect Status register.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: 0.0 - 100,000.0

Read/Write: R/W

Initialized Value: 10,000.0

Operational Settings: This register value is used as a comparison for the Va Detect Value and Vb Detect Value register values. Since LVDT/RVDTs vary, this value will need to be “tuned” and will be described in the Va Detect Value and Vb Detect Value registers section. Note, setting this register to 100,000 will disable this feature.

Short Detect Threshold

Function: Sets the threshold at which a “shorted” signal will be reported in the Short Detect Status register.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: 0.0 - 100,000.0

Read/Write: R/W

Initialized Value: 0.0

Operational Settings: This register value is used as a comparison for the Va Detect Value and Vb Detect Value register values. Since LVDT/RVDTs vary, this value will need to be “tuned” and will be described in the Va Detect Value and Vb Detect Value registers section.

|

Note

|

Setting this register to 0.0 will disable this feature. |

3-Wire/4-Wire Signal Fault Register

The following registers apply when the LVDT is configured for 3-Wire or 4-Wire mode.

Signal Fault Low Threshold

Function: Sets the “under-voltage” threshold at which a fault will be reported in the Signal Fault Low Status register.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0 - 30Vrms (LD1-LD4), 0 - 95Vrms (LD5)

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R/W

Initialized Value: LD1 - LD4 modules (826 decimal) (8.26V), LD5 module (6300 decimal) (63.00V)

Operational Settings: The signal fault detection circuitry will report a fault in the Signal Fault Low Status register when the measured signal is below the value set in Signal Fault Low Threshold register.

Signal Fault High Threshold

Function: Sets the “over-voltage” threshold at which a fault will be reported in the Signal Fault High Status register.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0 - 30Vrms (LD1-LD4), 0 - 9Vrms (LD5)

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R/W

Initialized Value: LD1 - LD4 modules (1685 decimal) (16.85V), LD5 module (9500 decimal) (95.00V)

Operational Settings: The signal fault detection circuitry will report a fault in the Signal Fault High Status register when the measured signal is above the value set in Signal Fault High Threshold register.

2-Wire Signal Fault Register

The following registers apply when the LVDT is configured for 2-Wire mode (Contact factory for availability).

Va Fault High Threshold

Function: Sets the “over-voltage” threshold at which a fault will be reported in the Va Fault High Status register.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0 - 30Vrms (LD1-LD4), 0 - 95Vrms (LD5)

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R/W

Initialized Value: LD1 - LD4 modules (1685 decimal) (16.85V), LD5 module (11700 decimal) (117.00V)

Operational Settings: The signal fault detection circuitry will report a fault in the Signal Fault Low Status register when the measured signal is below the value set in Signal Fault High Threshold register.

Vb Fault High Threshold

Function: Sets the “over-voltage” threshold at which a fault will be reported in the Vb Fault High Status register.

Type: unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: 0 - 30Vrms (LD1-LD4), 0 - 9Vrms (LD5)

Integer Mode (Enable Floating Point Mode register = 0)

LSB = 10 mV rms.

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R/W

Initialized Value: LD1 - LD4 modules (1685 decimal) (16.85V), LD5 module (11700 decimal) (117.00V)

Operational Settings: The signal fault detection circuitry will report a fault in the Signal Fault High Status register when the measured signal is above the value set in Signal Fault High Threshold register.

LVDT/RVDT Test Registers

Three different tests, one on-line (CBIT) and two off-line (UBIT, IBIT), can be selected. External reference voltage is not required for any of these tests.

Test Enabled

Function: Set bit in this register to enable associated Built-In Self-Test IBIT, CBIT and UBIT.

Type: unsigned binary word (32-bit)

Data Range: 0x0000 to 0x000D

Read/Write: R/W

Initialized Value: 0x4 (CBIT Test Enabled)

Operational Settings: BIT tests include an on-line (CBIT) test and two off-line (UBIT, IBIT) tests. Failures in the BIT tests are reflected in the BIT Status registers for the corresponding channels that fail. In addition, an interrupt (if enabled in the BIT Interrupt Enable register) can be triggered when the BIT testing detects a failure. UBIT and IBIT will not operate concurrently. When UBIT is enabled, the IBIT should not be enabled, and vice versa. CBIT can be set with either UBIT or IBIT enabled. Note: IBIT, when enabled, will run until the test completes (within 5 seconds).

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

IBIT Test D |

CBITTest 1 |

0 |

UBIT Test D |

Test CBIT Verify

Function: Allows user to verify if the CBIT test is running.

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0xFFFF FFFF

Read/Write: R/W

Initialized Value: 0

Operational Settings: User can write any value to this register. If CBIT test is running, after a minimum of 10ms the value read back will be 0x0000 0055, otherwise the value read back will be the value written.

UBIT Test Position

Function: Specifies position to be applied by LVDT/RVDT UBIT test.

Type: signed binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Data Range: -100% to +100%

Integer Mode (Enable Floating Point Mode register = 0)

32-bit two’s complement

-Full Scale (0x8000 0000) to +Full Scale (0x7FFF FFFF)

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R/W

Initialized Value: 0x1555 5555 (16.66%)

Operational Settings:

Integer Mode:

Set the UBIT Test Position based on the bit weighs shown in the table.

-100 |

50 |

25 |

12.5 |

6.25 |

3.125 |

1.5625 |

0.78125 |

0.390625 |

0.195313 |

0.097656 |

0.048828 |

0.024414 |

0.012207 |

0.006104 |

0.003052 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

1.525879E-03 |

7.629395E-04 |

3.814697E-04 |

1.907349E-04 |

9.536743E-05 |

4.768372E-05 |

2.384186E-05 |

1.192093E-05 |

5.960464E-06 |

2.980232E-06 |

1.490116E-06 |

7.450581E-07 |

3.725290E-07 |

1.862645E-07 |

9.313226E-08 |

4.656613E-08 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

D |

D |

D |

D |

D |

D |

D |

D |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Note

|

The per bit position values in the following table are approximate. |

Floating Point Mode:

Set as Single Precision Floating Point Value (IEEE-754).

BIT Error Limit

Function: Allows the user to set the error limit for the CBIT, UBIT and IBIT tests.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: Positive value - setting this value to zero will most likely result in a BIT Status failure.

Read/Write: R/W

Initialized Value: 0.1

Operational Settings: The default error limit that the BIT tests check to is 0.1. In some systems the noise characteristics may result in larger errors than the default error limit. Setting BIT Error Limit registers with a value that better suited for these systems may help lower the possibility of reporting “false-positives” for the channel in the BIT Status registers during BIT testing.

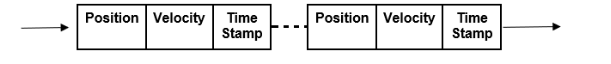

FIFO Registers

The FIFO registers are configurable for each channel.

FIFO Buffer Data

Function: Available data in the FIFO buffer can be retrieved, one word at a time (32-bits).

Type:

Position and Velocity: signed binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode)

Timestamp: unsigned binary word (32-bit)

Data Range: Varies based on Data type. Reading Position & Velocity can be either integer or float format. Time stamp will always be in integer format.

Integer Mode (Enable Floating Point Mode register = 0)

32-bit two’s complement

-Full Scale (0x8000 0000) to +Full Scale (0x7FFF FFFF)

Floating Point Mode (Enable Floating Point Mode register = 1)

Single Precision Floating Point Value (IEEE-754)

Read/Write: R

Initialized Value: 0

Operational Settings: Data for the Position & Velocity will be stored in either the integer format or IEEE floating point standard based on the state of the Enable Floating Point Mode register.

FIFO Word Count

Function: This is a counter that reports the number of 32-bit words currently in the FIFO Buffer Data register.

Type: unsigned binary word (32-bit)

Data Range: 0 to 0x0040 0000

Read/Write: R

Initialized Value: 0

Operational Settings: Each time the module writes to the FIFO, the word count will be incremented by 1. Any read operations made from the FIFO Buffer Data memory address, its corresponding Words in FIFO counter will be decremented by one. The maximum number of words that can be stored in the FIFO is 4,194,304 (4 Meg) (0x0040 0000).

FIFO Thresholds

The FIFO Almost Empty Threshold, FIFO Low Watermark Threshold, FIFO High Watermark Threshold, FIFO Almost Full Threshold and FIFO Buffer Size registers set the threshold limits that are used to set the bits in the FIFO Status registers.

|

Note

|

It is important that the almost empty threshold/low watermark threshold be set less than the almost full threshold/high watermark threshold, respectively, for valid operation. |

FIFO Almost Empty

Function: The FIFO Almost Empty threshold level is used as a comparison value to determine when to set the “almost empty” bit in the FIFO Status register.

Type: unsigned binary word (32-bit)

Data Range: 0 to 0x0040 0000

Read/Write: R/W

Initialized Value: 0x0000 0032

Operational Settings: When the number of words in the FIFO Word Count register is less than or equal to the value stored in this register, the “almost empty” bit (D1) of the FIFO Status register will be set. When the number of words in FIFO Word Count is greater than the value stored in this register, the “almost empty” bit (D1) of the FIFO Status register will be reset.

FIFO Low Watermark

Function: The FIFO Low Watermark threshold level is used as a comparison value to determine when to set the “low watermark” bit in the FIFO Status register.

Type: unsigned binary word (32-bit)

Data Range: 0 to 0x0040 0000

Read/Write: R/W

Initialized Value: 0x0000 0064

Operational Settings: When the number of words in FIFO Word Count register is less than or equal to the value stored in this register, the “low watermark” bit (D2) of the FIFO Status register will be set. When the number of words in FIFO Word Count is greater than the value stored in this register, the “low watermark” bit (D2) of the FIFO Status register will be reset.

FIFO High Watermark

Function: The FIFO High Watermark threshold level is used as a comparison value to determine when to set the “high watermark” bit in the FIFO Status register.

Type: unsigned binary word (32-bit)

Data Range: 0 to 0x0040 0000

Read/Write: R/W

Initialized Value: 0x003F 0000

Operational Settings: When the number of words in FIFO Word Count register is greater than or equal than the value stored in this register, the “high watermark” bit (D3) of the FIFO Status register will be set. When the number of words in FIFO Word Count is less than the value stored in the register, the “high watermark” bit (D3) of the FIFO Status register will be reset.

FIFO Almost Full

Function: The FIFO Almost Full threshold level is used as a comparison value to determine when to set the “almost full” bit in the FIFO Status register.

Type: unsigned binary word (32-bit)

Data Range: 0 to 0x0040 0000

Read/Write: R/W

Initialized Value: 0x003F FF00

Operational Settings: When the number of words in the FIFO Word Count register is greater than or equal to the value stored in this register, the “almost full” bit (D4) of the FIFO Status register will be set. When the number of words in FIFO Word Count is less than the value stored in this register, the “almost full” bit (D4) of the FIFO Status register will be reset.

FIFO Buffer Size

Function: The FIFO Buffer Size sets the number of samples to be taken and placed into the FIFO when a trigger occurs.

Type: unsigned binary word (32-bit)

Data Range: 0 to 0x0040 0000

Read/Write: R/W

Initialized Value: 0x0000 2000

Operational Settings: When the number of samples set in this register are sent to the FIFO, the “sample done” bit (D6) in the FIFO Status register is set. If another trigger is sent the “sample done” bit is cleared and set again once all data has been transferred. The largest number of samples that may be collected is 4,194,304 (0x0040 0000). If the buffer size is greater than the number of words available in the FIFO, only the number of words that are available will be stored and the remaining words lost.

FIFO Buffer Control

Function: The FIFO Buffer Control register defines the type of data that is stored in the FIFO Buffer Data register for each channel.

Type: unsigned binary word (32-bit)

Data Range: See table

Read/Write: R/W

Initialized Value: 0

Operational Settings: The following data types are available:

FIFO Buffer Control Description

Bit |

Description |

D31-D6 |

Reserved - Set to 0. |

D5 |

Store Velocity “B” Data (contact factory) |

D4 |

Store Position “B” Data (contact factory) |

D3 |

Reserved - Set to 0. |

D2 |

Store Timestamp. An integer counter that counts from 0 to 4,194,304 and wraps around when it overflows |

D1 |

Store Velocity Data |

D0 |

Store Position Data |

|

Note

|

Each data format (D0-D5) requires one word of storage from the FIFO buffer. For example: If D0, D1 and D2 are set (0x07) and the FIFO Buffer Size register is set to 1, a FIFO write will only put the Position data to the FIFO memory. |

If the FIFO Buffer Size is set to 10, it will store 4 Position values, 3 Velocity values & 3 timestamp values. Data will be stored in the order of Position, Velocity then timestamp. Since the maximum physical size of FIFO is 4,194,304 for each channel, the value in the FIFO Buffer Size register could cause an overflow to the FIFO Word Count register. When an overflow occurs, any data not placed in the FIFO will be lost.

FIFO Sample Rate

Function: The FIFO Sample Rate register sets the sampling rate for FIFO data collection for each channel.

Type: unsigned binary word (32-bit)

Data Range: 1 to 0xFFFF FFFF

Read/Write: R/W

Initialized Value: 1

Operational Settings: Sample rate is based on the product of 4.096 µsec x the integer set in the register. For example: if the rate is set to 2, the FIFO buffer sample rate will be, 4.096 µsec x 2 = 8.192 µsec

FIFO Sample Delay

Function: The FIFO Sample Delay register sets the number of delay samples before the actual FIFO data collection begins.

Type: unsigned binary word (32-bit)

Data Range: 0 to 0xFFFF FFFF

Read/Write: R/W

Initialized Value: 0

Operational Settings: The data collected during the delay period will be discarded.

|

Note

|

If timestamp is included as part of the FIFO data, it will begin as soon as the trigger is initiated. For example, if the FIFO Buffer Size register is set to 10, FIFO Sample Delay is set to 7, FIFO Sample Rate is at 1, and the Position is also selected to be stored, the data written into the FIFO would be <position>,8,<position>,9,<position>,10,<position>,11,<position>,12. |

FIFO Clear

Function: The FIFO Clear register clears FIFO data and sets the FIFO Word Count register to zero.

Type: unsigned binary word (32-bit)

Data Range: 0 to 1

Read/Write: W

Initialized Value: N/A

Operational Settings: Write a '1' to this register to reset the FIFO Word Count register to zero and clear the FIFO of any data in the buffer. After writing a '1' to the FIFO Clear register, the FIFO Buffer will only stay empty if all data has been sent (DONE bit set in the FIFO Status register). If data is still in the process of being written to the FIFO, any current data will be cleared, but the FIFO will continue to fill with new data until the number of samples sent equals the number of samples that was set in the FIFO Buffer Size register.

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

FIFO Trigger Control

Function: Sets the FIFO Buffer Triggering options. FIFO can be started/triggered by different sources.

Type: unsigned binary word (32-bit)

Data Range: See tables

Read/Write: R/W

Initialized Value: 2 (Software Trigger, Trigger Disabled)

Operational Settings: To Enable triggering, set D5 to 1. When set up for software triggering, write a 1 to the FIFO Software Trigger register to start the transfer of data to the FIFO. If in external mode and Positive slope is set (D4 = 0), a rising edge of the external trigger input will start the transfer of data to the FIFO. If in external mode and Negative slope is selected (D4 = 1), a falling edge of the external trigger input will start the transfer of data to the FIFO.

|

Note

|

Disabling the trigger while data is being transferred, does NOT stop the data from being written to the FIFO. |

FIFO Trigger Control Description

Bit |

Description |

D31-D7 |

Reserved - Set to 0. |

D6 |

Enable Trigger Always (contact factory) |

D5 |

Trigger Enable |

D4 |

Trigger Slope (0 = Positive, 1 = Negative) |

D3-D2 |

Reserved - Set to 0. |

D1-D0 |

0:0 - External Trigger 0:1 - N/A 1:0 - Software Trigger 1:1 - N/A |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

D |

D |

D |

D |

D |

D |

D |

FIFO Software Trigger

Function: Software trigger is used to kick start the FIFO buffer and the collection of data.

Type: unsigned binary word (32-bit)

Data Range: 0 or 1

Read/Write: W

Initialized Value: 0 (Not Triggered)

Operational Settings: To use this operation, the FIFO Trigger Control register must be set up as software trigger (D1 = 1) and Trigger Enable is enabled (D5 = 1). Write a 1 to this register to trigger FIFO collection for all channels. This register will automatically be cleared.

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

Engineering Scaling Conversion Registers

The LVDT/RVDT Module Threshold and Measurement registers can be programmed to be utilized as IEEE-754 single-precision floating-point values or as 32-bit integer values.

Enable Floating Point Mode

Function: Sets all channels for floating point mode or integer mode.

Type: unsigned binary word (32-bit)

Data Range: 0 or 1

Read/Write: R/W

Initialized Value: 0 (Integer mode)

Operational Settings: Set bit to 1 to enable Floating Point Mode and 0 for Integer Mode.

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

Floating Point Offset

Function: Sets the floating-point offset to add to data. There are separate floating-point offset registers for Position, Velocity, 2-wire Position “B”, and 2-wire Velocity “B” for each channel.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: N/A*

Read/Write: R/W

Initialized Value: 0.0

Operational Settings: Writing a value to one of these registers will add to the Position, Velocity, 2-wire Position “B”, or 2-wire Velocity “B” value based on which register is chosen (when floating-point mode is enabled). For example, if the position is currently at 10.000%, the position floating-point offset register is at 0.000, and floating-point mode is enabled, writing a 2.00 to the position floating-point offset register will result in the position reading 12.000%. If the value written is -1.7, then the position will be at 8.300%.

*Data Range is any acceptable 32-bit IEEE-754 value. Usage is application dependent - see examples within this document.

Floating Point Scale

Function: Sets the floating-point scale to modify the data. The data is multiplied by the floating-point scale divided by 100. There are separate floating-point scale registers for position, velocity, 2-wire position b, and 2-wire velocity b for each channel.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: N/A*

Read/Write: R/W

Initialized Value: 100

Operational Settings: Writing a value to one of these registers will multiply the position, velocity, 2-wire position b, or 2-wire velocity b value by the register value divided by 100 based on which register is chosen (when floating-point mode is enabled). For example, if the position is currently at 10.000%, the position floating-point scale register is at 100.000, and floating-point mode is enabled, writing a 50.00 to the position floating-point scale register will result in the position reading 5.000%.

*Data Range is any acceptable 32-bit IEEE-754 value. Usage is application dependent - see examples within this document.

Floating Point State

Function: Indicates the state of the mode selected (Integer or Floating Point).

Type: unsigned binary word (32-bit)

Data Range: 0 to 1

Read/Write: R

Initialized Value: 0

Operational Settings: Indicates the whether the module registers are in Integer (0) or Floating Point Mode (1). When the Enable Floating Point Mode is modified, the application must wait until this register’s value matches the requested mode before changing the values of the configuration and control registers with the values in the units specified (Integer or Floating Point).

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

Module Common Registers

Refer to “Module Common Registers Module Manual” for the register descriptions.

Status and Interrupt Registers

The LVDT/RVDT Modules provide status registers for BIT, Signal Fault Low, Signal Fault High, Reference Fault Low, Reference Fault High, Delta Position, FIFO, Open Detect, and Short Detect.

Channel Status Enable

Function: Determines whether to update the Latched and Real-Time status states for the channels. The default is channel status enable off (no failure).

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 - 0x0000 000F

Read/Write: R/W

Initialized Value: 0x0000 0000

Operational Settings: When the bit corresponding to a given channel in the Channel Status Enable register is enabled (1), it will allow the statuses for that channel to be updated. When the bit corresponding to a given channel is disabled (0), the statuses for that channel will be masked and reported as “0” or “no failure”.

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch.4 |

Ch.3 |

Ch.2 |

Ch1 |

BIT Status

There are four registers associated with the BIT Status: Dynamic, Latched, Interrupt Enable, and Set Edge/Level Interrupt.

BIT Dynamic Status |

|||||||||||||||

BIT Latched Status |

|||||||||||||||

BIT Interrupt Enable |

|||||||||||||||

BIT Set Edge/Level Interrupt |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch.4 |

Ch.3 |

Ch.2 |

Ch1 |

Function: Sets the corresponding bit associated with the channel’s BIT error.

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0x0000 000F