TE2 Manual

Edit this on GitLab

TE2 DATA SHEET

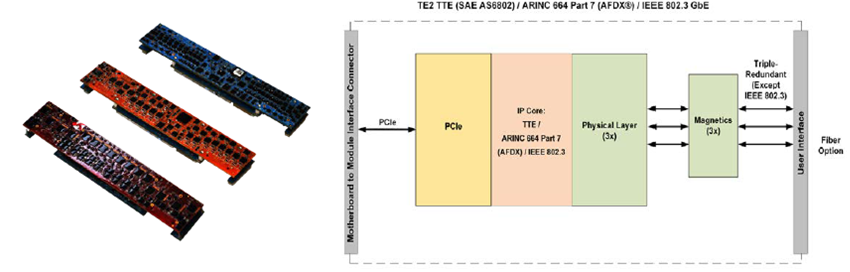

Module TE2 is one of NAI’s latest generation of advanced function Configurable Open Systems Architecture™ (COSA®) compatible modules. The TE2is a certifiable, single-port, tri-redundant, deterministic Ethernet communications interface module that supports TTTech’s certifiable TTEthernet® EndSystem product consisting of three traffic classes: SAE AS6802 (Time-Triggered Ethernet), ARINC 664 Part 7 (Avionics Full-Duplex Switched Ethernet(AFDX®), and/or IEEE 802.3 best-effort protocol. By supporting all three traffic classes, NAI’s TE2 is the ideal solution for current users of IEEE 802.3Ethernet, who plan to upgrade to Deterministic Ethernet (ARINC 664 Part 7 (AFDX®) or Time-Triggered Ethernet SAE AS6802) protocols in the future at any time without changing hardware.

The key feature of the TE2 module is TTEthernet’s ability to support all three protocols as required with triple-redundancy. IEEE 802.3 Ethernet is ubiquitous and has been the standard for many years. It provides best-effort data delivery, but does not provide any guarantee that the data was delivered or that the data was delivered in the sequence that it was sent. Deterministic Ethernet provides safety and mission critical quality of service in data transmission and reception: in the case of ARINC 664 Part 7, data sent from the TE2 through a policing AFDX® or TTE® switch is transmitted with bounded latency and jitter (millisecond precision); in the case of SAE AS6802, data sent from the TE2 through a policing TTE® switch is precisely scheduled with the highest priority and is transmitted at precise times with microsecond precision.

The TE2 module is currently supported on 67PPC2 and 68PPC2 (PowerPC T2080) with Wind River® VxWorks® 653 3.x or DDC-I Deos™. Also available on the 68G5P for 3rd party SBC boards. Contact factory for support.

FEATURES |

|

Three Modes of Ethernet operation: - IEEE 802.3 - ARINC 664 part 7 (AFDX®) - SAE AS6802 TTE Single-port, triple redundant Ethernet Module that supports each protocol Supports 10/100/1000 Mbps Ethernet Supported on 67PPC2 & 68PPC2 (PowerPC T2080) with Wind River® VxWorks® 653 3.x or DDC-I Deos™ Available on the 68G5P for 3rd party SBC boards; contact factory for support |

SPECIFICATIONS |

|

Communication: |

PCIe Gen II (5.0 Gbps) Endpoint |

Protocols: |

IEEE 802.3; ARINC 664 Part 7 (AFDX®); SAE AS6802 (Time Triggered Ethernet). Based onTTTech’s TTEthernet® |

Ethernet Standards: |

10BASE-T, 100BASE-T, 1000BASE-T |

ARINC 664 Part 7 (AFDX) / SAE AS6802 (Time-Triggered Ethernet) Comparison

Both ARINC 664 Part 7 (AFDX®) and SAE AS6802 (Time-Triggered Ethernet) provide time-critical, safety-critical data transmission and receipt sent through a single-port, tri-redundant Ethernet module that can be optimized for specific applications. Major features of ARINC 664 Part 7 (AFDX®) andSAE AS6802 (Time-Triggered Ethernet) are listed below.

ARINC 664 Part 7 |

SAE AS6802 |

|

Communication: |

Asynchronous |

Synchronous |

Jitter: |

up to 2 ms |

~ 1 μs |

Latency (typical): |

1-10 ms |

< 12.5 μs/switch |

INTRODUCTION

This module manual provides information about the North Atlantic Industries, Inc. (NAI) TTEthernet® Module Communications Function Module:TE2. This module is compatible with all NAI Generation 5 motherboards that support local or off-board host processor-direct PCIe interface.

Module TE2 is one of NAI’s latest generation of advanced function Configurable Open Systems Architecture™ (COSA®) compatible modules. The TE2 is a DO-178 and DO-254 certifiable, single-port, tri-redundant, deterministic Ethernet communications interface module that supports TTTech’s certifiable TTEthernet® End System product consisting of three traffic classes:

-

SAE AS6802 (Time-Triggered Ethernet);

-

ARINC 664 Part 7 (Avionics Full-Duplex Switched Ethernet (AFDX®)); and/or

-

IEEE 802.3 best-effort protocol.

By supporting all three traffic classes, NAI’s TE2 is the ideal solution for current users of IEEE 802.3 Ethernet, who plan to upgrade to Deterministic Ethernet (ARINC 664 Part 7 (AFDX®) or Time-Triggered Ethernet SAE AS6802) protocols in the future at any time without changing hardware.

The key feature of the TE2 module is TTEthernet’s ability to support all three protocols as required with triple-redundancy. IEEE 802.3 Ethernet is ubiquitous and has been the standard for many years. It provides best-effort data delivery but does not provide any guarantee that the data was delivered or that the data was delivered in the sequence that it was sent.

Deterministic Ethernet provides safety and mission critical quality of service in data transmission and reception: in the case of ARINC 664 Part 7, data sent from the TE2 through a policing AFDX® or TTE® switch is transmitted with bounded latency and jitter (millisecond precision); in the case of SAE AS6802, data sent from the TE2 through a policing TTE® switch is precisely scheduled with the highest priority and is transmitted at precise times with microsecond precision.

FEATURES

-

TTEthernet’s 3 modes of operation: SAE AS6802 (Time-Triggered Ethernet), ARINC 664 Part 7 (AFDX®), IEEE 802.3

-

Single-port, tri-redundant Ethernet module that supports each protocol

-

Supports 10/100/1000Base-TX Mbps Ethernet

-

Supported on 67PPC2 & 68PPC2 (PPC T2080) with Wind River® VxWorks® 653 3.x or DDC-I Deos

-

Available on the 68G5P for 3rd party SBC boards. Contact factory for support

PRINCIPLE OF OPERATION

Module TE2 provides up to 1 channel programmable SAE AS6802, ARINC 664 PART 7 (AFDX®) or IEEE 802.3 channels with triple redundant ports as applicable. The TE2 communications interface architecture relies upon a TTTech IP and PCIe driver to configure the TTTech enabled network switches.

Once initialized and configured, the Ethernet network class traffic is handled and outed automatically per the traffic class protocol packet and addressing structure. Therefore, TE2 can support multiple SAE AS6802, ARINC 664 PART 7 (AFDX®) OR IEEE 802.3 and 575 channels simultaneously.

REGISTER DESCRIPTIONS

The following is derived from the TTech IP and software PCIe Driver configuration utility. The TE2 does not support direct configuration memory registers as typical NAI smart function modules but rather expects to be initialized and handled through software configuration utilizes supplied by TTech and operational for the IP loaded in the module hardware (as IP/firmware).

Network Description

PCIe Interface

The TE2 communications interface architecture relies upon a TTTech IP and PCIe driver to configure the TTTech enabled network switches.

The TE2 module has two BAR’s

BAR0 is used by the TTTech / DDCI driver

BAR1 is used by the NAI interface

The following registers are accessible from BAR1

Register |

Offset Address |

Description |

Test Register |

0x04 |

Used to test communications to the TE2 module. This is a Read/Write register that can be used to verify that that TE2 module can be access via the PCIe bus. |

FPGA Revision |

0x08 |

This is a read only register that contains the FPGA Revision. |

FPGA Timestamp |

0x14 |

This is a read only register that contains the FPGA build date / time. Data format: Bits 31..27 = Day 26..23 = Mon 22..17 = Yr(2000) 16..12 = Hr 11..6 = Min 5..0 = Sec |

TTE Functions

Message TX/RX APIs

Functions

-

Tte_Es_Ret tte_es_close_iport (Tte_Es_Iport_Hdl *iport, bool_t reset_drops)

-

Tte_Es_Ret tte_es_close_oport (Tte_Es_Oport_Hdl *oport)

-

Tte_Es_Ret tte_es_flush_iport (Tte_Endsystem_Hdl es, Tte_Es_Ap Id ap_id, Tte_Es_Port_Id port_id)

-

Tte_Es_Ret tte_es_get_hdr_ipsap_buf (Tte_Es_Port_Data _buf, Tte_Es_Iport_Ip_Sap *info)

-

Tte_Es_Ret tte_es_get_hdr_ipsap_port (Tte_Es_Iport_Hdl iport, Tte_Es_Iport_Ip_Sap *info)

-

Tte_Es_Ret tte_es_get_hdr_macsap_buf (Tte_Es_Port_Data _buf, Tte_Es_Iport_Mac_Sap *info)

-

Tte_Es_Ret tte_es_get_hdr_udpsap_buf (Tte_Es_Port_Data _buf, Tte_Es_Iport_Udp_Sap *info)

-

Tte_Es_Ret tte_es_get_hdr_udpsap_port (Tte_Es_Iport_Hdl iport, Tte_Es_Iport_Udp_Sap *info)

-

Tte_Es_Data_Size tte_es_get_ihdr_size (Tte_Es_Iport_Type type)

-

Tte_Es_Ret tte_es_get_iport_status (Tte_Es_Iport_Hdl iport, Tte_Es_Iport_Status *status)

-

Tte_Es_Ret tte_es_get_iport_type (Tte_Es_Iport_Hdl iport, Tte_Es_Iport_Type *type)

-

Tte_Es_Data_Size tte_es_get_ohdr_size (Tte_Es_Oport_Type type)

-

Tte_Es_Ret tte_es_get_oport_status (Tte_Es_Oport_Hdl oport, Tte_Es_Oport_Status *oport_status)

-

Tte_Es_Ret tte_es_get_oport_type (Tte_Es_Oport_Hdl oport, Tte_Es_Oport_Type *type)

-

Tte_Es_Ret tte_es_get_raw_imsg (Tte_Es_Iport_Hdl iport, Tte_Es_Port_Data **msg)

-

Tte_Es_Ret tte_es_get_raw_omsg (Tte_Es_Oport_Hdl oport, Tte_Es_Port_Data **msg)

-

Tte_Es_Ret tte_es_get_timestamp (Tte_Es_Iport_Hdl iport, Tte_Es_Iport_Timestamp *timestamp)

-

Tte_Es_Iport_Hdl tte_es_open_iport (Tte_Endsystem_Hdl es, Tte_Es_Ap_Id ap_id, Tte_Es_Port_Id port_id, Tte_Es_Data_Size *size, bool_t *fresh, Tte_Es_Ret *result)

-

Tte_Es_Oport_Hdl tte_es_open_oport (Tte_Endsystem_Hdl es, Tte_Es_Ap_Id ap_id, Tte_Es_Port_Id port_id, Tte_Es_Data_Size msg_len, Tte_Es_Ret *result)

-

Tte_Es_Ret tte_es_query_iport (Tte_Endsystem_Hdl es, Tte_Es_Ap_Id ap_id, Tte_Es_Port_Id port_id, Tte_Es_Iport_Status *status, Tte_Es_Iport_Props *props)

-

Tte_Es_Ret tte_es_query_oport (Tte_Endsystem_Hdl es, Tte_Es_Ap_Id ap_id, Tte_Es_Port_Id port_id, Tte_Es_Oport_Status _status, Tte_Es_Oport_Props *props)

-

Tte_Es_Ret tte_es_read_data (Tte_Es_Iport_Hdl iport, Tte_Es_Port_Data *data, Tte_Es_Data_Size length)

-

Tte_Es_Ret tte_es_set_hdr_ipsap_buf (Tte_Es_Port_Data *buf, Tte_Es_Oport_Ip_Sap *info)

-

Tte_Es_Ret tte_es_set_hdr_ipsap_port (Tte_Es_Oport_Hdl oport, Tte_Es_Oport_Ip_Sap *info)

-

Tte_Es_Ret tte_es_set_hdr_macraw_buf (Tte_Es_Port_Data *buf, Tte_Es_Oport_Mac_Raw *info)

-

Tte_Es_Ret tte_es_set_hdr_macsap_buf (Tte_Es_Port_Data *buf, Tte_Es_Oport_Mac_Sap *info)

-

Tte_Es_Ret tte_es_set_hdr_udpsap_buf (Tte_Es_Port_Data *buf, Tte_Es_Oport_Udp_Sap *info)

-

Tte_Es_Ret tte_es_set_hdr_udpsap_port (Tte_Es_Oport_Hdl oport, Tte_Es_Oport_Udp_Sap *info)

-

Tte_Es_Ret tte_es_write_data (Tte_Es_Oport_Hdl oport, Tte_Es_Port_Data _data, Tte_Es_Data_Size length)

Status APIs

Functions

-

Tte_Es_Ret tte_es_get_bist_status (Tte_Endsystem_Hdl es, Tte_Es_Bist_Status *status)

-

Tte_Es_Ret tte_es_get_channel_stats (Tte_Endsystem_Hdl es, Tte_Es_Channel_Stats *stats)

-

Tte_Es_Ret tte_es_get_clock_corrections (Tte_Endsystem_Hdl es, Tte_Es_Clock_Corrections *corr)

-

Tte_Es_Ret tte_es_get_com_params (Tte_Endsystem_Hdl es, Tte_Es_Dev_Params *params)

-

Tte_Es_Ret tte_es_get_config_status (Tte_Endsystem_Hdl es, Tte_Es_Config_Status *status)

-

Tte_Es_Ret tte_es_get_cycle_time (Tte_Endsystem_Hdl es, uint32_t *time_ns)

-

Tte_Es_Ret tte_es_get_device_info (Tte_Endsystem_Hdl es, Tte_Es_Info *es_info)

-

Tte_Es_Ret tte_es_get_drop_stats (Tte_Endsystem_Hdl es, Tte_Es_Drop_Stats *stats)

-

Tte_Es_Ret tte_es_get_error_status (Tte_Endsystem_Hdl es, Tte_Es_Error_Status *status)

-

Tte_Es_Ret tte_es_get_mac_src_addr (Tte_Endsystem_Hdl es, uint8_t channel, uint8_t *adr)

-

Tte_Es_Ret tte_es_get_no_cots_status (Tte_Endsystem_Hdl es, Tte_Es_No_Cots_Status *status)

-

Tte_Es_Ret tte_es_get_partition_space (Tte_Endsystem_Hdl es, uint8_t part_id, uint16_t *space, uint32_t *threshold_vect)

-

Tte_Es_Ret tte_es_get_partition_status (Tte_Endsystem_Hdl es, Tte_Es_Ap_Id ap_id, Tte_Es_Partition_Status *status)

-

Tte_Es_Ret tte_es_get_prom_mode (Tte_Endsystem_Hdl es, uint8_t channel, bool_t *enable)

-

Tte_Es_Ret tte_es_get_ram_error_status (Tte_Endsystem_Hdl es, Tte_Es_Ram_Error_Status *status)

-

Tte_Es_Ret tte_es_get_rm_error_status (Tte_Endsystem_Hdl es, Tte_Es_Rm_Error_Status *status)

-

Tte_Es_Ret tte_es_get_sync_stats (Tte_Endsystem_Hdl es, Tte_Es_Sync_Stats *stats)

-

Tte_Es_Ret tte_es_get_sync_status (Tte_Endsystem_Hdl es, Tte_Es_Sync_Status *status)

-

Tte_Es_Ret tte_es_get_time (Tte_Endsystem_Hdl es, uint64_t *time_ns)

-

Tte_Es_Ret tte_es_get_time_resolution (Tte_Endsystem_Hdl es, uint32_t *res_ns)

-

Tte_Es_Ret tte_es_get_vl_status (Tte_Endsystem_Hdl es, uint16_t vl_tbl_idx, Tte_Es_Vl_Error_Status *status)

Typical PCIe Enumeration (VxWorks)

Dumping all PCI device headers on PCIe3 vxBus ID 0x809140

[1,0,0] type=NET_CNTLR

status=0x0010 ( CAP DEVSEL=0 )

command=0x0007 ( IO_ENABLE MEM_ENABLE MASTER_ENABLE )

bar0 in 32-bit mem space @ 0xc4000000

bar1 in 32-bit mem space @ 0xc4200000

vendor ID = |

0x1c7e |

device ID = |

0x012a |

command register = |

0x0007 |

status register = |

0x0010 |

revision ID = |

0x00 |

class code = |

0x02 |

sub class code |

0x00 |

programming interface = |

0x00 |

cache line = |

0x10 |

latency time = |

0x00 |

header type = |

0x00 |

BIST = |

0x00 |

base address 0 = |

0xc4000000 |

base address 1 = |

0xc4200000 |

base address 2 = |

0x00000000 |

base address 3 = |

0x00000000 |

base address 4 = |

0x00000000 |

base address 5 = |

0x00000000 |

cardBus CIS pointer = |

0x00000000 |

sub system vendor ID = |

0x1c7e |

sub system ID = |

0x0007 |

expansion ROM base address = |

0x00000000 |

interrupt line = |

0x00 |

interrupt pin = |

0x00 |

min Grant = |

0x00 |

max Latency = |

0x00 |

Capabilities - Power Management |

|

Capabilities - Message Signaled Interrupts: 0x48 control 0x84 Disabled, 64-bit, MME: 0 MMC: 2 |

|

Address: |

0000000000000000 Data: 0x0000 |

Per-vector Mask: |

Unsupported |

Capabilities - PCIe: Endpoint, IRQ 0 |

|

Device: |

Max Payload: 256 bytes, Phantom Funcs 1 msb, Extended Tag: 8-bit |

Acceptable Latency: |

L0 - <64ns, L1 - <1us |

Errors Enabled: |

Relaxed Ordering No Snoop |

Max Read Request: |

512 bytes |

Link: MAX Speed - 5.0Gb/s, MAX Width - by 1 Port - 0 ASPM - L0s |

|

Latency: |

L0s - >4us, L1 - >64us |

ASPM - |

Disabled, RCB - 64bytes |

Speed - |

5.0Gb/s, Width - by 1 |

Ext Capabilities - Device Serial Number. 0x100. Version 1 |

|

Serial Number: |

0x0 0x0 0x0 0x0 0x0 0x0 0x0 0x0 |

The register descriptions provide the register name, Type, Data Range, Read or Write information, Initialized Value, a description of the function and, in most cases, a data table.

FUNCTION REGISTER MAP

Not applicable. (N/A).

The TE2 relies on TTech IP and PCIe driver for initializations and operation set-up.

APPENDIX A: REGISTER NAME CHANGES FROM PREVIOUS RELEASES

Not applicable. (N/A).

The TE2 relies on TTech IP and PCIe driver for initializations and operation set-up.

APPENDIX B: PIN-OUT DETAILS

Pin-out details (for reference) are shown below, with respect to DATAIO. Additional information on pin-outs can be found in the Motherboard Operational Manuals

Module Signal (Ref Only) |

44-Pin I/O |

50-Pin I/O (Mod Slot 1-J3) |

50-Pin I/O (Mod Slot 2-J4) |

50-Pin I/O (Mod Slot 3-J3) |

50-Pin I/O (Mod Slot 3-J4) |

TTE (TE2) |

DATIO1 |

2 |

10 |

1 |

2 |

TTE-ETH1-TP0+ |

|

DATIO2 |

24 |

35 |

26 |

27 |

TTE-ETH1-TP0- |

|

DATIO3 |

3 |

11 |

2 |

3 |

TTE-ETH1-TP1+ |

|

DATIO4 |

25 |

36 |

27 |

28 |

TTE-ETH1-TP1- |

|

DATIO5 |

5 |

13 |

4 |

5 |

TTE-ETH1-TP2+ |

|

DATIO6 |

27 |

38 |

29 |

30 |

TTE-ETH1-TP2- |

|

DATIO7 |

7 |

14 |

5 |

6 |

TTE-ETH1-TP3+ |

|

DATIO8 |

29 |

39 |

30 |

31 |

TTE-ETH1-TP3- |

|

DATIO9 |

8 |

15 |

6 |

7 |

TTE-ETH2-TP0+ |

|

DATIO10 |

30 |

40 |

31 |

32 |

TTE-ETH2-TP0- |

|

DATIO11 |

10 |

17 |

8 |

9 |

TTE-ETH2-TP1+ |

|

DATIO12 |

32 |

42 |

33 |

34 |

TTE-ETH2-TP1- |

|

DATIO13 |

12 |

18 |

9 |

17 |

TTE-ETH2-TP2+ |

|

DATIO14 |

34 |

43 |

34 |

42 |

TTE-ETH2-TP2- |

|

DATIO15 |

13 |

19 |

10 |

18 |

TTE-ETH2-TP3+ |

|

DATIO16 |

35 |

44 |

35 |

43 |

TTE-ETH2-TP3- |

|

DATIO17 |

15 |

21 |

12 |

20 |

TTE-ETH3-TP0+ |

|

DATIO18 |

37 |

46 |

37 |

45 |

TTE-ETH3-TP0- |

|

DATIO19 |

17 |

22 |

13 |

21 |

TTE-ETH3-TP1+ |

|

DATIO20 |

39 |

47 |

38 |

46 |

TTE-ETH3-TP1- |

|

DATIO21 |

18 |

23 |

14 |

22 |

TTE-ETH3-TP2+ |

|

DATIO22 |

40 |

48 |

39 |

47 |

TTE-ETH3-TP2- |

|

DATIO23 |

20 |

25 |

16 |

24 |

TTE-ETH3-TP3+ |

|

DATIO24 |

42 |

50 |

41 |

49 |

TTE-ETH3-TP3- |

|

DATIO25 |

4 |

12 |

3 |

4 |

||

DATIO26 |

26 |

37 |

28 |

29 |

||

DATIO27 |

9 |

16 |

7 |

8 |

Shield |

|

DATIO28 |

31 |

41 |

32 |

33 |

||

DATIO29 |

14 |

20 |

11 |

19 |

||

DATIO30 |

36 |

45 |

36 |

44 |

||

DATIO31 |

19 |

24 |

15 |

23 |

||

DATIO32 |

41 |

49 |

40 |

48 |

||

DATIO33 |

6 |

|||||

DATIO34 |

28 |

|||||

DATIO35 |

11 |

|||||

DATIO36 |

33 |

|||||

DATIO37 |

16 |

|||||

DATIO38 |

38 |

|||||

DATIO39 |

21 |

|||||

DATIO40 |

43 |

|||||

N/A |

REVISION HISTORY

Motherboard Manual - TE2 Revision History |

||

Revision |

Revision Date |

Description |

C |

2023-07-10 |

EC0 C10540, create new I/M; obsolete old I/M. Transition to docbuilder format. Replaced 'Specifications' section with TE2 data sheet. Pg.4, added 3rd paragraph to description. Pg.4, updated 4th features bullet; added 5th bullet. Pg.6, updated 4th features bullet; added 5th bullet. Pg.7, added Network Description section. |

DOCS.NAII REVISIONS

Revision Date |

Description |

2025-02-24 |

Update Network Parameters table to add Device Target column. |

2025-03-13 |

Updated module pinout table to add module I/O pinouts for 44- & 50-pin connectors. |

NAI Cares

Edit this on GitLab

North Atlantic Industries (NAI) is a leading independent supplier of Embedded I/O Boards, Single Board Computers, Rugged Power Supplies, Embedded Systems and Motion Simulation and Measurement Instruments for the Military, Aerospace and Industrial Industries. We accelerate our clients’ time-to-mission with a unique approach based on a Configurable Open Systems Architecture™ (COSA®) that delivers the best of both worlds: custom solutions from standard COTS components.

We have built a reputation by listening to our customers, understanding their needs, and designing, testing and delivering board and system-level products for their most demanding air, land and sea requirements. If you have any applications or questions regarding the use of our products, please contact us for an expedient solution.

Please visit us at: www.naii.com or select one of the following for immediate assistance: