68ARM1 Manual

Edit this on GitLab

INTRODUCTION

North Atlantic Industries (NAI) is a leading independent supplier of rugged COTS embedded computing products for industrial, commercial aerospace, and defense markets. Aligned with MOSA, SOSA and FACE standards, NAI’s Configurable Open System Architecture™ (COSA®) accelerates a customer’s time-to-mission by providing the most modular, agile, and rugged COTS portfolio of embedded smart modules, I/O boards, Single Board Computers (SBCs), Power Supplies and Ruggedized Systems of its kind. COSA products are pre-engineered to work together, enabling easy changes, reuses, or repurposing down the road. By utilizing FPGAs and SoCs, NAI has created smart modules that enable the rapid creation of configurable mission systems while reducing or eliminating SBC overhead.

NAI’s 68ARM1 3U OpenVPX Single Board Computer (SBC) is a rugged processing board which provides low power, cost-sensitive processing capabilities designed for demanding aerospace, defense, and industrial applications. When combined with NAI’s smart modules, the board’s modular I/O approach makes it a highly flexible and integrable solution for demanding computing environments.

68ARM1 Overview

The 68ARM1 3U OpenVPX Single Board Computer (SBC) offers a variety of features designed to meet the needs of complex requirements for integrated multifunction I/O-intensive, mission-critical applications. Some of the key features include:

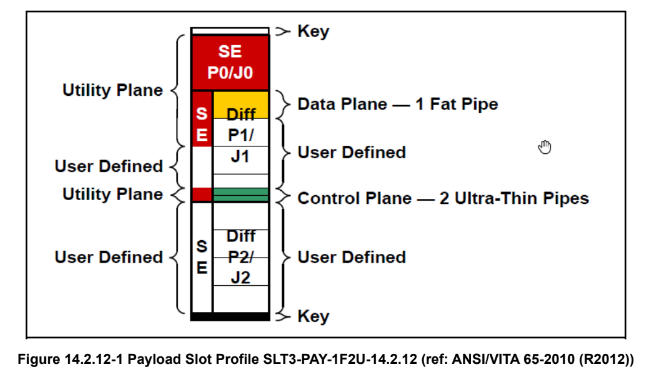

3U Profiles supported: This board is aligned with both VPX and OpenVPX standards, with module and slot profiles specified as

-

MOD3-PAY-1F2U-16.2.11-2

-

SLT3-PAY-1F2U-14.2.12

This compatibility ensures interoperability with other components and promote system-level integration for efficient optimized performance.

Connection Flexibility: The SBC provides flexibility in connectivity options, with the ability to connect to devices via the front panel, rear panel, or both. This feature is particularly useful in different mounting or space-constrained scenarios.

2x 10/100/1000 Base-T and 2x 1000Base-KX Ethernet: The 68ARM1 provides optional 10/100/1000 Base-T Ethernet ports to the front and rear of the board and 1000Base-KX Ethernet ports to the rear of the board. These ports provide data communication capabilities and network connectivity for advanced control and data acquisition applications.

ARM® Cortex®-A9 Dual Core 800 MHz Processor: The 68ARM1 offers a significant advantage by providing enhanced processing power and efficiency. With its dual-core configuration and 800 MHz clock speed, it enables advanced computational tasks and real-time processing capabilities, making it an ideal choice for applications requiring high performance computing within a compact form factor.

512 MB DDR3 SDRAM: The SBC features a 512 MB DDR3 SDRAM, which offers users a dependable memory solution for demanding military, industrial, and aerospace environments:

-

DDR3 SDRAM’s capacity enables efficient data storage and retrieval for critical applications, while its DDR3 architecture ensures high-speed and low latency operation (crucial for real-time processing in dynamic environments).

-

DDR3 SDRAM’s ruggedized design and resistance to extreme temperatures/shock/vibration make it well-suited for deployment in demanding conditions, ensuring consistent and dependable performance in mission-critical scenarios.

32 GB SATA II NAND Flash: The 68ARM1 utilizes a SATA II NAND Flash memory capable of providing up to 32 GB of storage, offering high-capacity, durable, reliable, and rugged data storage. It is well suited for applications where data must be securely stored and accessed in challenging environmental conditions while providing a cost-effective storage solution.

Less than 10 Watts Motherboard Power Dissipation: With a power dissipation of less than 10 watts, the 68ARM1 proves a highly efficient solution, offering superior energy conservation, effective thermal management, extended mission endurance, and heightened reliability for demanding military, industrial, and aerospace applications.

Support for three independent, smart function: The SBC can support up to three independent, smart function modules based on the COSA® architecture. With over 100 modules to choose from, this allows for a wide range of input and output capabilities, including analog and digital I/O, signal generation and acquisition, and communication interfaces. Each function module slot has an independent x1 SerDes interface for motherboard-to-smart module interface, to offload the host processor from I/O management.

-

The 68ARM1’s function slot #2 supports high-speed I/O via rear I/O while function slot #3 supports on-board module or independent external SATA II port access over the VPX backplane. These interfaces facilitate the expansion of external host SBC functions, which enables engineers and system architects to easily configure the board with the necessary modules and accelerate SWaP-optimized system deployment.

Peripheral I/O: The 68ARM1 board features several sophisticated on-board (on motherboard) peripheral I/O interfaces, all of which are rear accessed. Designed to meet the diverse requirements of complex projects, this comprehensive I/O suite includes:

-

One USB 2.0 interface to front maintenance J5 or to the rear I/O, enabling users to transfer data quickly and reliably.

-

An RS-232 console/maintenance port (front and rear) that provides a standard interface for communicating with the board for maintenance and debugging purposes. This serial port can be used for configuring the board or accessing diagnostic information and logs.

Continuous Background Built-In-Test (BIT): Continuously monitoring the board’s health and functionality during operation, this feature allows for proactive maintenance, minimizing downtime and facilitating early issue resolution for uninterrupted performance in demanding operational environments.

Software Support Kits (SSKs): SSKs are provided ‘free of charge' and include base motherboard and function module API libraries and documentation. Sample and source code are also available, as well as support for real-time operating systems (RTOS) such as Wind River® VxWorks®, Xilinx® PetaLinux, and DDC-I Deos™, providing developers with flexibility and customization options for their specific application needs.

VICTORY Interface Services: NAI offers VICTORY Interface Services as an option, providing an open industry-standard approach for integrating different components in a system.

Commercial and rugged mechanical options: The 68ARM1 is available in both commercial and rugged models, making it suitable for a wide range of applications.

-

Operating temperature: The board has a wide operating temperature range, with models operating from:

-

0° C to 70° C (commercial model)

-

-40° C to +85° C (rugged model)

-

SOFTWARE SUPPORT

Edit this on GitLab

The ENAIBL Software Support Kit (SSK) is supplied with all system platform based board level products. This platform’s SSK contents include html format help documentation which defines board specific library functions and their respective parameter requirements. A board specific library and its source code is provided (module level ‘C’ and header files) to facilitate function implementation independent of user operating system (O/S). Portability files are provided to identify Board Support Package (BSP) dependent functions and help port code to other common system BSPs. With the use of the provided help documentation, these libraries are easily ported to any 32-bit O/S such as RTOS or Linux.

The latest version of a board specific SSK can be downloaded from our website www.naii.com in the software downloads section. A Quick-Start Software Manual is also available for download where the SSK contents are detailed, Quick-Start Instructions provided and GUI applications are described therein. For other operating system support, contact factory.

SPECIFICATIONS

General for the Motherboard

Signal Logic Level: |

Supports LVDS PCIe ver. 2.0 bus (x1) |

Power (Motherboard): |

+5 VDC @ 0.70 A (typical) ±12 V @ 0 mA (certain modules may require +/-12 V for operation) +3.3V_AUX @ <100 mA (typical) Then add power for each individual module |

Temperature, Operating: |

"C" =0° C to +70° C, "H" =-40° C to +85° C (see part number) |

Storage Temperature: |

-55° C to +105° C |

Temperature Cycling: |

Each board is cycled from -40° C to +85° C for option “H” |

General size |

|

Height: |

3.94" / 100 mm (3U) |

Width: |

0.8” / 20.3 mm (4HP) or 1.0" / 25.4 mm (5 HP) air cooled front panel options |

Depth: |

6.3“ / 160 mm deep |

Weight: |

12.5 oz. (354 g) unpopulated (approx.) (convection or conduction cooled) >> then add weight for each module (typically 1.5 oz. (42 g) each) |

Specifications are subject to change without notice.

Environmental

Unless otherwise specified, the following table outlines the general Environmental Specifications design guidelines for board level products of North Atlantic Industries. All our cPCI, VME and OpenVPX boards are designed for either air or conduction cooling. All boards also incorporate appropriate stiffening to ensure performance during shock and vibration but also to assure reliable operation (lower fatigue stresses) over the service life of the product.

Parameters |

Level |

||

1 / Commercial-AC (Air Cooled) |

2 / Rugged-AC (Air Cooled) |

3 / Rugged-CC (Conduction Cooled) |

|

Temperature - Operating |

0° C to 70° C, AmbientH |

-40° C to 85° C, AmbientI |

-40° C to 85° C, at wedge lock thermal interface |

Temperature - Storage |

-40° C to 85° C |

-55° C to 105° C |

-55° C to 105° C |

Humidity - Operating |

0 to 95%, non-condensing |

0 to 95%, non-condensing |

0 to 95%, non-condensing |

Humidity - Storage |

0 to 95%, non-condensing |

0 to 95%, non-condensing |

0 to 95%, non-condensing |

Vibration - SineA |

2 g peak, 15 Hz - 2 kHzB |

6 g peak, 15 Hz - 2 kHzB |

10 g peak, 15 Hz - 2 kHzC |

Vibration - RandomD |

.002 g2 /Hz, 15 Hz - 2 kHz |

0.04 g2 /Hz, 15 Hz - 2 kHz |

0.1 g2 /Hz, 15 Hz - 2 kHzE |

ShockF |

20 g peak, half-sine, 11 ms |

30 g peak, half-sine 11 ms |

40 g peak, half-sine, 11 ms |

Low PressureG |

Up to 15,000 ft. |

Up to 50,000 ft. |

Up to 50,000 ft. |

Notes:

-

Based on sweep duration of ten minutes per axis on each of the three mutually perpendicular axes.

-

Displacement limited to 0.10 D.A. from 15 to 44 Hz.

-

Displacement limited to 0.436 D.A. from 15 to 21 Hz.

-

60 minutes per axis on each of the three mutually perpendicular axes.

-

Per MIL-STD-810G, Method 5.14.6 Procedure I, Fig.514.6C-6 Category 7 tailored (11.65 Grms): 15 Hz - 2 kHz; ASD (PSD) at 0.04 g2/Hz between 15 Hz - 150 Hz, increasing @ 4 dB/octave from 0.04 g2/Hz to 0.1 g /Hz between 150 Hz - 300 Hz, 0.1 g2/Hz between 300 Hz - 1000 Hz, decreasing @ 6 dB/octave from 0.1 g2/Hz to 0.025 g2/Hz between 1000 Hz - 2000 Hz. Three hits per direction per axis (total of 18 hits).

-

Three hits per direction per axis (total of 18 hits).

-

For altitudes higher than 50,000 ft., contact NAI.

-

High temperature operation requires 350 lfm minimum air flow across cover/heatsink (module dependent).

-

High temperature operation requires 600 lfm minimum air flow across cover/heatsink (module dependent).

Specifications subject to change without notice

REGISTER MEMORY MAP ADDRESSING

The register map address consists of the following:

-

cPCI/PCIe BAR or Base Address for the Board

-

Module Slot Base Address

-

Function Offset Address

Board Base Address

The table below lists the BAR used for access to the motherboard and module registers. The second BAR is used internally for motherboard and module firmware updates. The other cPCI/PCIe BARs not listed are not used.

NAI Boards |

Device ID |

Bus |

Motherboard and Module Register Access |

Motherboard and Module Firmware Updates |

Controller/Master Boards |

||||

68ARM1 |

0x6884 |

PCIe |

BAR 1 Size: Module Dependent (minimum 64K Bytes) |

BAR 2 Size: 1M Bytes |

Module Slot and Function Addresses

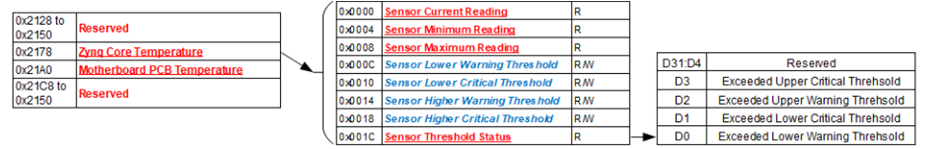

The memory map for the modules are dependent on the types of modules on the board and the order in which the modules are installed on the board as well as the firmware installed on the motherboard. The function modules are enumerated allowing for dynamic memory space allocation and therefore the “start” address of the module function register area is factory pre-defined (and read from) the Module Address register. Refer to Figure 1 for an example.

Figure 1. Register Memory Map Addressing for Motherboards with 3 Modules

Address Calculation

Motherboard Registers

Read/Write access to the motherboard registers starts with the base address for the board and then the motherboard base offset address.

For example, to address Module Slot 1 Start Address register (i.e. register address = 0x0400):

-

Start with the base address for the board.

-

Add the motherboard register address offset.

Motherboard Address = |

Base Address + Motherboard Address Offset |

= 0x0000 0400 |

0x0000 0000 + 0x0400 |

Module Registers:

Read/Write access to the Function module’s registers start with the base address of the board. Add the “content” for the Module Start Address and then, add the specific module function register offset.

For example, to address an appropriate/specific function module with a register offset:

-

Start with the base address for the board.

-

Add the value (contents) from the module base address offset register (contents/value of Motherboard Memory register for Module 1 (i.e., @ 0x0400) = 0x4000.

-

Then add the specific module function Register Offset of interest (i.e., A/D Reading Ch 1 @ 0x1000)

(Function Specific) Address = |

Base Address |

Module Base Address Offset |

Function Register Offset |

= 0x0000 5000 |

0x0000 0000 |

0x4000 |

0x1000 |

REGISTER DESCRIPTIONS

Module Information Registers

The Module Slot Addressing Ready, Module Slot Address, Module Slot Size and Module Slot ID provide information about the modules detected on the board.

Module Slot Addressing Ready |

|

Function: |

Indicates that the module slots are ready to be addressed. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

0xA5A5A5A5 |

Operational Settings: |

This register will contain the value of 0xA5A5A5A5 when the module addresses have been determined. |

Module Slot Address |

|

Function: |

Specifies the Base Address for the module in the specific slot position. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Based on board’s module configuration. |

Operational Settings: |

0x0000 0000 indicates no Module found. |

Module Slot Size |

|

Function: |

Specifies the Memory Size (in bytes) allocated for the module in the specific slot position. |

Type: |

unsigned binary word (32-bit) |

Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Assigned by factory for the module. |

Operational Settings: |

0x0000 0000 indicates no Module found. |

Module Slot ID |

|

Function: |

Specifies the Model ID for the module in the specified slot position. |

Type: |

4-character ASCII string |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Assigned by factory for the module. |

Operational Settings: |

The Module ID is formatted as four ASCII bytes: three characters followed by a space. Module IDs are in little-endian order with a single space following the first three characters. For example, 'TL1' is '1LT', 'SC1' is '1CS' and so forth. Example below is for “TL1” (MSB justified). All value of 0000 0000 indicates no Module found. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

ASCII Character (ex: 'T' - 0x54) |

ASCII Character (ex: 'L' - 0x4C) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ASCII Character (ex: '1' - 0x31) |

ASCII Space (' ' - 0x20) |

||||||||||||||

Hardware Information Registers

The registers identified in this section provide information about the board’s hardware.

Product Serial Number |

|

Function: |

Specifies the Board Serial Number. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Serial number assigned by factory for the board. |

Operational Settings: |

N/A |

Platform

Function: Specifies the Board Platform Identifier. Values are for the ASCII characters for the NAI valid platforms (Identifiers).

Type: unsigned binary word (32-bit)

Data Range: See table below.

Read/Write: R

Initialized Value: ASCII code is for the Platform Identifier of the board

Operational Settings: Valid NAI platform and the associated value for the platform is shown below:

NAI Platform |

Platform Identifier |

ASCII Binary Values (Note: little-endian order of ascii values) |

3U VPX |

68 |

0x0000 3836 |

Model

Function: Specifies the Board Model Identifier. Value is for the ASCII characters for the NAI valid model.

Type: unsigned binary word (32-bit)

Data Range: See table below.

Read/Write: R

Initialized Value: ASCII code is for the Model Identifier of the board

Operational Settings: Example of NAI model and the associated value for the model is shown below:

NAI Model |

ASCII Binary Values (Note: little-endian order of ascii values) |

ARM |

0x004D 5241 |

Generation

Function: Specifies the Board Generation. Identifier values are for the ASCII characters for the NAI valid generation identifiers.

Type: unsigned binary word (32-bit)

Data Range: See table below.

Read/Write: R

Initialized Value: ASCII code is for the Generation Identifier of the board

Operational Settings: Example of NAI generation and the associated value for the generation is shown below:

NAI Generation |

ASCII Binary Values (Note: little-endian order of ascii values) |

1 |

0x0000 0031 |

Processor Count/Ethernet Count

Function: Specifies the Processor Count and Ethernet Count

Type: unsigned binary word (32-bit)

Data Range: See table below.

Read/Write: R

Operational Settings:

Processor Count - Integer: indicates the number of unique processor types on the motherboard.

NAI Board |

Processor Count |

Description |

|

3U-VPX |

68ARM1 |

1 |

Xilinx Zynq 7015 with Dual Core Cortex A9 |

Ethernet Interface Count - Indicates the number of Ethernet interfaces on the product motherboard. For example, Single Ethernet = 1; Dual Ethernet = 2.

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Processor Count (See Table) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Ethernet Count (Based on Part Number Ethernet Options) |

|||||||||||||||

Maximum Module Slot Count/ARM Platform Type

Function: Specifies the Maximum Module Slot Count and ARM Platform Type.

Type: unsigned binary word (32-bit)

Data Range: See table below.

Read/Write: R

Operational Settings:

Maximum Module Slot Count - Indicates the number of modules that can be installed on the product.

ARM Platform - Altera = 1; Xilinx X1 = 2; Xilinx X2 = 3; UltraScale = 4

NAI Board |

Maximum Module Slot Count |

ARM Platform Type |

|

3U-VPX |

68ARM1 |

3 |

Xilinx X2 = 3 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Maximum Module Slot Count (See Table) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ARM Platform Type (See Table) |

|||||||||||||||

Motherboard Firmware Information Registers

The registers in this section provide information on the revision of the firmware installed on the motherboard.

Motherboard Core (MBCore) Firmware Version |

|

Function: |

Specifies the Version of the NAI factory provided Motherboard Core Application installed on the board. |

Type: |

Two (2) unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Operational Settings: |

The motherboard firmware version consists of four components: Major, Minor, Minor 2 and Minor 3. |

Motherboard Core Firmware Version (Note: little-endian order in register) (ex. 4.7.0.0) |

|||||||||||||||

Word 1 (Ex. 0007 0004 = 4.7 (Major.Minor) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Minor (ex: 0x0007 = 7) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Major (ex: 0x0004 = 4) |

|||||||||||||||

Word 2 (Ex. 0x0000 0000 = 0000 = 0.0 (Minor2.Minor3)) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Minor 3 (ex: 0x000 = 0) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Minor 2 (ex: 0x000 = 0) |

|||||||||||||||

Motherboard Firmware Build Time/Date |

|

Function: |

Specifies the Build Date/Time of the NAI factory provided Motherboard Core Application installed on the board. |

Type: |

Two (2) unsigned binary word (32-bit) |

Data Range: |

N/A |

Read/Write: |

R |

Operational Settings: |

The motherboard firmware time consists of the Build Date and Build Time. NOTE: On some builds the the Date/Time fields are fixed to 0000 0000 to maintain binary consistency across builds. |

Motherboard Firmware Build Time (Note: little-endian order in register) |

|||||||||||||||

Word 1 - Build Date (ex. 0x030C 07E2 = 2018-12-03) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Day (ex: 0x03 = 3) |

Month (ex: 0x0C = 12) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Year (ex: 0x07E2 = 2018) |

|||||||||||||||

Word 2 - Build Time (ex. 0x001B 3B0A = 10:59:27) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

null (0x00) |

Seconds (ex: 0x1B = 27) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Minutes (ex: 0x3B = 59) |

Hours (ex: 0x0A = 10) |

||||||||||||||

Motherboard Monitoring Registers

The registers in this provide motherboard temperature measurement information, and where applicable the slave processor measurements.

Temperature Readings Register

Edit this on GitLab

The temperature registers provide the current, maximum (from power-up) and minimum (from power-up) for the processor and PCB for Zynq processor, and for the Slave processor.

These registers are only available on Xilinx Generation 5 platforms, and are periodically populated by the motherboard core application, which only runs in Petalinux and BareMetal. For other operating systems, refer to the naibrd Software Support Kit (SSK) naibsp_system_Monitor_Temperature_Get() routine to manually retrieve the temperature (NOTE: this feature is typically utilized for development/factory use only; contact the factory for additional details on potential use, if required).

Function: Specifies the Measured Temperatures on Motherboard.

Type: signed byte (8-bits) for each temperature reading - Six (6) 32-bit words

Data Range: 0x0000 0000 to 0xFFFF 0000

Read/Write: R

Initialized Value: Value corresponding to the measured temperatures based on the table below.

Operational Settings: The 8-bit temperature readings are signed bytes. For example, if the following register contains the value 0x6955 0000:

Example:

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Max Zynq Core Temperature |

Max Zynq PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

The values would represent the following temperatures:

Temperature Measurements |

Data Bits |

Value |

Temperature (Celsius) |

Max Zynq Core Temperature |

D31:D24 |

0x69 |

+105° |

Max Zynq PCB Temperature |

D23:D16 |

0x55 |

+85° |

Temperature Readings

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Zynq Core Temperature |

Zynq PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Slave Zynq Core Temperature |

Slave Zynq PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Max Zynq Core Temp |

Max Zynq PCB Temp |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0x00 |

0x00 |

||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Max Slave Zynq Core Temp |

Max Slave Zynq PCB Temp |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Min Zynq Core Temperature |

Min Zynq PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Min Slave Zynq Core Temperature |

Min Slave Zynq PCB Temperature |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Higher Precision Temperature Readings Register

These registers provide higher precision readings of the current Zynq and PCB temperatures.

Higher Precision Zynq Core Temperature |

|

Function: |

Specifies the Higher Precision Measured Zynq Core temperature on Interface Board. |

Type: |

signed word (16-bits) for integer part and unsigned word (16-bits) for fractional part |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Measured Zynq Core temperature on Interface Board |

Operational Settings: |

The upper 16-bits represent the signed integer part of the temperature and the lower 16-bits represent the fractional part of the temperature with the resolution of 1/1000 of degree Celsius. For example, if the register contains the value 0x002B 0271, this represents Zynq Core Temperature = 43.625° Celsius, and value 0xFFF6 0177 represents -10.375° Celsius. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Signed Integer Part of Temperature |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Fractional Part of Temperature |

|||||||||||||||

Higher Precision Motherboard PCB Temperature |

|

Function: |

Specifies the Higher Precision Measured Motherboard PCB temperature. |

Type: |

signed word (16-bits) for integer part and unsigned word (16-bits) for fractional part |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Measured Motherboard PCB temperature |

Operational Settings: |

The upper 16-bits represent the signed integer part of the temperature and the lower 16-bits represent the fractional part of the temperature with the resolution of 1/1000 of degree Celsius. For example, if the register contains the value 0x0020 007D, this represents Interface PCB Temperature = 32.125° Celsius, and value 0xFFE8 036B represents -24.875° Celsius. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Signed Integer Part of Temperature |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Fractional Part of Temperature |

|||||||||||||||

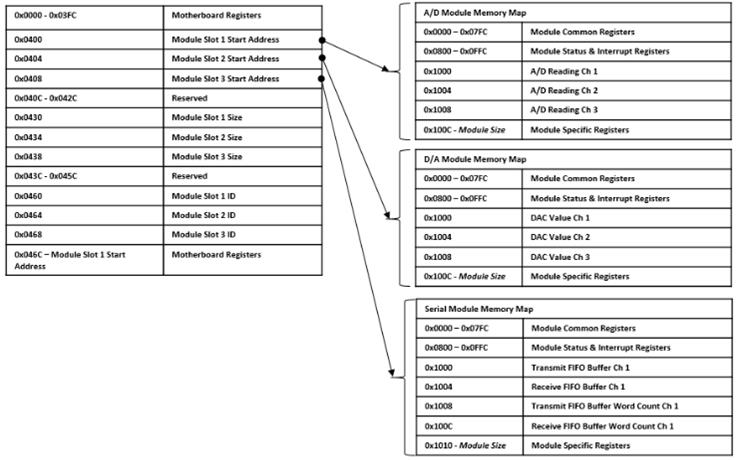

Motherboard Health Monitoring Registers

The registers in this section provide a summary of motherboard temperature sensors and their corresponding bits. Additionally, this section provides an overview of the registers allocated to those sensors, which are used to monitor current/minimum/maximum temperature readings, upper & lower critical/warning temperature thresholds, and whether or not a programmed temperature threshold has been exceeded.

These registers are only available on Xilinx Generation 5 platforms, and are periodically populated by the motherboard core application, which only runs in Petalinux and BareMetal. For other operating systems, refer to the naibrd Software Support Kit (SSK) naibsp_system_Monitor_Temperature_Get() routine to manually retrieve the temperature (NOTE: this feature is typically utilized for development/factory use only; contact the factory for additional details on potential use, if required).

Motherboard Sensor Summary Alarm |

|

Function: |

The corresponding sensor bit is set if the sensor has crossed any of its thresholds. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table below |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

This register provides a summary for motherboard sensors. When the corresponding sensor bit is set, the Sensor Threshold Status register for that sensor will indicate the threshold condition that triggered the event. |

Bit(s) |

Sensor |

D31:D5 |

Reserved |

D4 |

Motherboard PCB Temperature |

D3 |

Zynq Core Temperature |

D2:D0 |

Reserved |

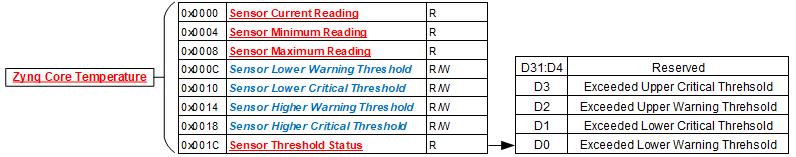

Motherboard Sensor Registers

Edit this on GitLab

The registers listed in this section apply to each module sensor listed for the Motherboard Sensor Summary Status register. Each individual sensor register provides a group of registers for monitoring motherboard temperatures readings. From these registers, a user can read the current temperature of the sensor in addition to the minimum and maximum temperature readings since power-up. Upper and lower critical/warning temperature thresholds can be set and monitored from these registers. When a programmed temperature threshold is crossed, the Sensor Threshold Status register will set the corresponding bit for that threshold. The figure below shows the functionality of this group of registers when accessing the Zynq Core Temperature sensor as an example.

Sensor Threshold Status |

|

Function: |

Reflects which threshold has been crossed |

Type: |

unsigned binary word (32-bits) |

Data Range: |

See table below |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

The associated bit is set when the sensor reading exceed the corresponding threshold settings. |

Bit(s) |

Description |

D31:D4 |

Reserved |

D3 |

Exceeded Upper Critical Threshold |

D2 |

Exceeded Upper Warning Threshold |

D1 |

Exceeded Lower Critical Threshold |

D0 |

Exceeded Lower Warning Threshold |

Sensor Current Reading |

|

Function: |

Reflects current reading of temperature sensor |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

The register represents current sensor reading as a single precision floating point value. For example, for a temperature sensor, register value 0x41C6 0000 represents temperature = 24.75° Celsius. |

Sensor Minimum Reading |

|

Function: |

Reflects minimum value of temperature sensor since power up |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

The register represents minimum sensor value as a single precision floating point value. For example, for a temperature sensor, register value 0x41C6 0000 represents temperature = 24.75° Celsius. |

Sensor Maximum Reading |

|

Function: |

Reflects maximum value of temperature sensor since power up |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

The register represents maximum sensor value as a single precision floating point value. For example, for a temperature sensor, register value 0x41C6 0000 represents temperature = 24.75° Celsius. |

Sensor Lower Warning Threshold |

|

Function: |

Reflects lower warning threshold of temperature sensor |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R/W |

Initialized Value: |

Default lower warning threshold (value dependent on specific sensor) |

Operational Settings: |

The register represents sensor lower warning threshold as a single precision floating point value. For example, for a temperature sensor, register value 0xC220 0000 represents temperature = -40.0° Celsius. |

Sensor Lower Critical Threshold |

|

Function: |

Reflects lower critical threshold of temperature sensor |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R/W |

Initialized Value: |

Default lower critical threshold (value dependent on specific sensor) |

Operational Settings: |

The register represents sensor lower critical threshold as a single precision floating point value. For example, for a temperature sensor, register value 0xC25C 0000 represents temperature = -55.0° Celsius. |

Sensor Upper Warning Threshold |

|

Function: |

Reflects upper warning threshold of temperature sensor |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R/W |

Initialized Value: |

Default upper warning threshold (value dependent on specific sensor) |

Operational Settings: |

The register represents sensor upper warning threshold as a single precision floating point value. For example, for a temperature sensor, register value 0x42AA 0000 represents temperature = 85.0° Celsius. |

Sensor Upper Critical Threshold |

|

Function: |

Reflects upper critical threshold of temperature sensor |

Type: |

Single Precision Floating Point Value (IEEE-754) |

Data Range: |

Single Precision Floating Point Value (IEEE-754) |

Read/Write: |

R/W |

Initialized Value: |

Default upper critical threshold (value dependent on specific sensor) |

Operational Settings: |

The register represents sensor upper critical threshold as a single precision floating point value. For example, for a temperature sensor, register value 0x42FA 0000 represents temperature = 125.0° Celsius. |

Ethernet Configuration Registers

Edit this on GitLab

The registers in this section provide information about the Ethernet Configuration for the two ports on the board.

Important: Regardless if the board is configured for one or two Ethernet ports, the second IP address cannot be on the same Subnet as the First IP Address. The table below provides examples of valid and invalid IP Addresses and Subnet Mask Addresses.

First Port (A) IP Address |

First Port (A) Subnet Mask |

Second Port (B) IP Address |

Second Port (B) Subnet Mask |

Result |

192.168.1.5 |

255.255.255.0 |

192.168.2.5 |

255.255.255.0 |

Good |

192.168.1.5 |

255.255.0.0 |

192.168.2.5 |

255.255.0.0 |

Conflict |

192.168.1.5 |

255.255.0.0 |

192.168.2.5 |

255.255.255.0 |

Conflict |

10.0.0.15 |

255.0.0.0 |

192.168.1.5 |

255.255.255.0 |

Good |

Ethernet MAC Address and Ethernet Settings |

|

Function: |

Specifies the Ethernet MAC Address and Ethernet Settings for the Ethernet port. |

Type: |

Two (2) unsigned binary word (32-bit) |

Data Range: |

See table. |

Read/Write: |

R |

Operational Settings: |

The Ethernet MAC Address consists of six octets. The Ethernet Settings are defined in table. |

Bits |

Description |

Values |

D31:D23 |

Reserved |

0 |

D22:D21 |

Duplex |

00 = Not Specified, |

D20:D18 |

Speed |

000 = Not Specified, |

D17 |

Auto Negotiate |

0 = Enabled, |

D16 |

Static IP Address |

0 = Enabled, |

Ethernet MAC Address and Ethernet Settings (Note: little-endian order in register) |

|||||||||||||||

Word 1 (Ethernet MAC Address (Octets 1-4)) (ex: aa:bb:cc:dd:ee:ff) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

MAC Address Octet 4 (ex: 0xDD) |

MAC Address Octet 3 (ex: 0xCC) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

MAC Address Octet 2 (ex: 0xBB) |

MAC Address Octet 1 (ex: 0xAA) |

||||||||||||||

Word 2 (Ethernet MAC Address (Octets 5-6) and Ethernet Settings) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Ethernet Settings (See table) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

MAC Address Octet 6 (ex: 0xFF) |

MAC Address Octet 5 (ex: 0xEE) |

||||||||||||||

Ethernet Interface Name |

|

Function: |

Specifies the Ethernet Interface Name for the Ethernet port. |

Type: |

8-character ASCII string |

Data Range: |

See table. |

Read/Write: |

R |

Operational Settings: |

The Ethernet Interface Name (eth0, eth1, etc) for the Ethernet port. |

Ethernet Interface Name (Note: ascii string in register) (ex. “eth0”) |

|||||||||||||||

Word 1 (Bit 0-31) (ex: 0x3068 7465 = “0hte”) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

ASCII Character (ex: '0' - 0x30) |

ASCII Character (ex: 'h' - 0x68) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ASCII Character (ex: 't' - 0x74) |

ASCII Character (ex: 'e' - 0x65) |

||||||||||||||

Word 2 (Bit 32-63) (ex: 0x0000 0000) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

ASCII Character (ex: null - 0x00) |

ASCII Character (ex: null - 0x00) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ASCII Character (ex: null - 0x00) |

ASCII Character (ex: null - 0x00) |

||||||||||||||

Ethernet IPv4 Address |

|

Function: |

Specifies the Ethernet IPv4 Address for the Ethernet port. |

Type: |

Three (3) unsigned binary word (32-bit) |

Data Range: |

See table. |

Read/Write: |

R |

Operational Settings: |

The Ethernet IPv4 Address consists of three parts: IPv4 Address, IPv4 Subnet Mask and IPv4 Gateway. |

Ethernet IPv4 Address (Note: little-endian order in register) |

|||||||||||||||

Word 1 (Ethernet IPv4 Address) (ex: 0x1001 A8C0 = 192.168.1.16) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

IPv4 Address Octet 4 (ex: 0x10 = 16) |

IPv4 Address Octet 3 (ex: 0x01 = 1) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

IPv4 Address Octet 2 (ex: 0xA8 = 168) |

IPv4 Address Octet 1 (ex: 0xC0 = 192) |

||||||||||||||

Word 2 (Ethernet IPv4 Subnet) (ex: 0x00FF FFFF = 255.255.255.0) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

IPv4 Subnet Octet 4 (ex: 0x00 = 0) |

IPv4 Subnet Octet 3 (ex: 0xFF = 255) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

IPv4 Subnet Octet 2 (ex: 0xFF = 255) |

IPv4 Subnet Octet 1 (ex: 0xFF = 255) |

||||||||||||||

Word 3 (Ethernet IPv4 Gateway) (ex: 0x0101 A8C0 = 192.168.1.1) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

IPv4 Gateway Octet 4 (ex: 0x01 = 1) |

IPv4 Gateway Octet 3 (ex: 0x01 = 1) |

||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

IPv4 Gateway Octet 2 (ex: 0xA8 = 168) |

IPv4 Gateway Octet 1 (ex: 0xC0 = 192) |

||||||||||||||

| Ethernet IPv6 Address | |

|---|---|

Function: |

Specifies the Ethernet IPv6 Address for the Ethernet port. |

Type: |

Five (5) unsigned binary word (32-bit) |

Data Range: |

See table. |

Read/Write: |

R |

Operational Settings: |

The IPv6 Prefix length indicates the network portion of an IPv6 address using the following format: * IPv6 address/prefix length |

The following is an illustration of IPv6 addressing with IPv6 Prefix length of 64.

64 bits |

64 bits |

||||||

Prefix |

Interface ID |

||||||

Prefix 1 |

Prefix 2 |

Prefix 3 |

Subnet ID |

Interface ID 1 |

Interface ID 2 |

Interface ID 3 |

Interface ID 4 |

Example: 2002:c0a8:101:0:7c99:d118:9058:1235/64 |

|||||||

2002 |

C0A8 |

0101 |

0000 |

7C99 |

D118 |

9058 |

1235 |

Ethernet IPv6 Address (Note: little-endian order within 32-bit and 16-bit words in register) (ex. IPv6 Address: 2002:c0a8:201:0:7c99:d118:9058:1235 IPv6 Prefix: 64) |

|||||||||||||||

Word 1 (Ethernet IPv6 Address (Prefix 1-2)) (ex:0xA8C0 0220 = 2002 C0A8) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Prefix 2 (ex: 0xA8C0 = C0A8) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Prefix 1 (ex: 0x0220 = 2002) |

|||||||||||||||

Word 2 (Ethernet IPv6 Address (Prefix 3/Subnet ID)) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Subnet ID (ex: 0x0000 = 0000) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Prefix 3 (ex: 0x0101 = 0101) |

|||||||||||||||

Word 3 (Ethernet IPv6 Address (Interface ID 1-2)) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Interface ID 2 (ex: 0x18D1 = D118) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Interface ID 1 (ex: 0x997C = 7C99) |

|||||||||||||||

Word 4 (Ethernet IPv6 Address (Interface ID 3-4)) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Interface ID 4 (ex: 0x3512 = 1235) |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Interface ID 3 (ex: 0x5890 = 9058) |

|||||||||||||||

Word 5 (Ethernet IPv6 Prefix Length) |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Prefix Length (ex: 0x0040 = 64) |

|||||||||||||||

Interrupt Vector and Steering

Edit this on GitLab

When interrupts are enabled, the interrupt vector associated with the specific interrupt can be programmed (typically with a unique number/identifier) such that it can be utilized in the Interrupt Service Routine (ISR) to identify the type of interrupt. When an interrupt occurs, the contents of the Interrupt Vector registers is reported as part of the interrupt mechanism. In addition to specifying the interrupt vector, the interrupt can be directed (“steered”) to the native bus or to the application running on the onboard ARM processor.

|

Note

|

The Interrupt Vector and Interrupt Steering registers are mapped to the Motherboard Common Memory and these registers are associated with the Module Slot position (refer to Function Register Map). |

Interrupt Vector |

|

Function: |

Set an identifier for the interrupt. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, this value is reported as part of the interrupt mechanism. |

Interrupt Steering |

|

Function: |

Sets where to direct the interrupt. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

See table |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, the interrupt is sent as specified: |

Direct Interrupt to VME |

1 |

Direct Interrupt to ARM Processor (via SerDes) |

2 |

Direct Interrupt to PCIe Bus |

5 |

Direct Interrupt to cPCI Bus |

6 |

Module Control Command Registers

Edit this on GitLab

Modules Control Command Requests |

|

Function: |

Provides the ability to command individual Modules to Reset, Power-down, or Power-up. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Operational Settings: |

The Module Control Commands registers provide the ability to request individual Modules to perform one of the following functions - Reset, Power-down, Power-up. Only one command can be requested at a time per Module. For example, one can’t request a Reset and a Power-down at the same time for the same Module. Once the command is recognized and handled, the bit will be cleared. |

|

Note

|

Clearing of the command request bit only indicates the command has been recognized and initiated, it does not indicate that the command action has been completed. |

There is one Control Command Request register per Module. Each register is Bit-mapped as shown in the table below:

Bit(s) |

Description |

D31:D3 |

Reserved |

D2 |

Module Power-up |

D1 |

Module Power-down |

D0 |

Module Reset |

Modules Health Monitoring Registers

Module Communications Status |

|

Function: |

Provides the ability to monitor factors may effect communication status of a Module. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Operational Settings: |

The Module Communications registers provide the ability to monitor factors that may effect the Communications Status of individual Modules. There is one register per Module. Each communication factor is bit mapped to the register as shown in the table below: |

Bit(s) |

Description |

D31:D5 |

Reserved |

D4 |

Module Communications Error Detected |

D3 |

Module Firmware Not Ready |

D2 |

Module LinkInit Not Done |

D1 |

Module Not Detected |

D0 |

Module Powered-down |

Module Powered-down: The user can request an individual Module be powered-down (see Module Control Command Requests). Once the request is detected and acted upon, this bit will be set. Once powered-down, you will not be able to communicate with the Module.

Module Not Detected: If a Module in this slot has not been detected, you will not be able to communicate with the Module.

Module LinkInit Not Done: Module communications is accomplished via SERDES. LinkInit is required to establish a connection to the Module. If the LinkInit has not been successfully completed, you will not be able to communicate with the Module.

Module Firmware Not Ready: Each Module has Firmware that is ready from Module QSPI and loaded for execution. If this Firmware was not loaded and started successfully, you may not be able to communicate with the Module.

Module Communications Error Detected: If at some point during run-time, communications with the Module has failed, this bit will be set.

Module BIT Status

Edit this on GitLab

Function: |

Provides the ability to monitor the individual Module BIT Status. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Operational Settings: |

The Module BIT Status registers provide the ability to monitor individual Module BIT results as Latched and current value. A 1 is any bit field indicates BIT failure for the Module in that slot. |

Bit(s) |

Description |

D31:D20 |

Reserved |

D19 |

Module Slot 3 BIT Failure (current value) |

D18 |

Module Slot 2 BIT Failure (current value) |

D17 |

Module Slot 1 BIT Failure (current value) |

D16 |

Reserved |

D15:D4 |

Reserved |

D3 |

Module Slot 3 BIT Failure - Latched |

D2 |

Module Slot 2 BIT Failure - Latched |

D1 |

Module Slot 1 BIT Failure - Latched |

D0 |

Reserved |

Scratchpad Area

Edit this on GitLab

Scratchpad Area |

|

Function: |

Registers reserved as scratch pad for customer use. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Operational Settings: |

This area in memory is reserved for customer use. |

MOTHERBOARD FUNCTION REGISTER MAP

Key:

Bold Underline = Measurement/Status/Board Information

Bold Italic = Configuration/Control

Module Information Registers

0x03FC |

Module Slot Addressing Ready |

R |

0x0400 |

Module Slot 1 Address |

R |

0x0404 |

Module Slot 2 Address |

R |

0x0408 |

Module Slot 3 Address |

R |

0x0430 |

Module Slot 1 Size |

R |

0x0434 |

Module Slot 2 Size |

R |

0x0438 |

Module Slot 3 Size |

R |

0x0460 |

Module Slot 1 ID |

R |

0x0464 |

Module Slot 2 ID |

R |

0x0468 |

Module Slot 3 ID |

R |

Hardware Information Registers

0x0020 |

Product Serial Number |

R |

0x0024 |

Platform |

R |

0x0028 |

Model |

R |

0x002C |

Generation |

R |

0x0030 |

Processor Count/Ethernet Count |

R |

0x0034 |

Maximum Module Slot Count/ARM Platform Type |

R |

Motherboard Firmware Information Registers

0x0100 |

MBCore Major/Minor Version |

R |

0x0104 |

MBCore Minor 2/3 Version |

R |

0x0108 |

MBCore Build Date (Bit 0-31) |

R |

Motherboard Monitoring Registers

Temperature Readings

0x0200 |

Current Zynq Temperatures |

R |

0x0204 |

Current Slave Zynq Temperatures |

R |

0x0208 |

Max Zynq Temperatures |

R |

0x020C |

Max Slave Zynq Temperatures |

R |

0x0210 |

Min Zynq Temperatures |

R |

0x0214 |

Min Slave Zynq Temperatures |

R |

Higher Precision Temperature Readings

0x0230 |

Current Zynq Core Temperature |

R |

0x0234 |

Current Motherboard PCB Temperature |

R |

Ethernet Configuration Registers

0x0070 |

Ethernet A MAC (Octets 1-4) |

R |

0x0074 |

Ethernet A MAC (Octets 5-6)/Misc Settings |

R |

0x0078 |

Ethernet A Interface Name (Bit 0-31) |

R |

0x007C |

Ethernet A Interface Name (Bit 32-63) |

R |

0x0080 |

Ethernet A IPv4 Address |

R |

0x0084 |

Ethernet A IPv4 Subnet Mask |

R |

0x0088 |

Ethernet A IPv4 Gateway |

R |

0x008C |

Ethernet A IPv6 Address (Prefix 1-2) |

R |

0x0090 |

Ethernet A IPv6 Address (Prefix 3/Subnet ID) |

R |

0x0094 |

Ethernet A IPv6 Address (Interface ID 1-2) |

R |

0x0098 |

Ethernet A IPv6 Address (Interface ID 3-4) |

R |

0x009C |

Ethernet A IPv6 Prefix Length |

R |

0x00A0 |

Ethernet B MAC (Octets 1-4) |

R |

0x00A4 |

Ethernet B MAC (Octets 5-6)/Misc Settings |

R |

0x00A8 |

Ethernet B Interface Name (Bit 0-31) |

R |

0x00AC |

Ethernet B Interface Name (Bit 32-63) |

R |

0x00B0 |

Ethernet B IPv4 Address |

R |

0x00B4 |

Ethernet B IPv4 Subnet Mask |

R |

0x00B8 |

Ethernet B IPv4 Gateway |

R |

0x00BC |

Ethernet B IPv6 Address (Prefix 1-2) |

R |

0x00C0 |

Ethernet B IPv6 Address (Prefix 3/Subnet ID) |

R |

0x00C4 |

Ethernet B IPv6 Address (Interface ID 1-2) |

R |

0x00C8 |

Ethernet B IPv6 Address (Interface ID 3-4) |

R |

0x00CC |

Ethernet B IPv6 Prefix Length |

R |

Interrupt Vector and Steering

0x0500 - 0x057C |

Module 1 Interrupt Vector 1 - 32 |

R/W |

0x0700 - 0x077C |

Module 2 Interrupt Vector 1 - 32 |

R/W |

0x0900 - 0x097C |

Module 3 Interrupt Vector 1 - 32 |

R/W |

0x0600 - 0x067C |

Module 1 Interrupt Steering 1 - 32 |

R/W |

0x0800 - 0x087C |

Module 2 Interrupt Steering 1 - 32 |

R/W |

0x0A00 - 0x0A7C |

Module 3 Interrupt Steering 1 - 32 |

R/W |

Module Control Command Requests

0x01D8 |

Module Slot 1 Command Request |

R/W |

0x01DC |

Module Slot 2 Command Request |

R/W |

0x01E0 |

Module Slot 3 Command Request |

R/W |

ETHERNET

Edit this on GitLab

(For detailed supplement, please visit the NAI web-site specific product page and refer to: Ethernet Interface for Generation 5 SBC and Embedded IO Boards Specification)

|

Note

|

For products capable of 10/100/1000Base-KX functionality - the product Ethernet PHY supports 1000BASE-X. Product interoperability with 10/100/1000BASE-KX is supported with 1000BASE-X (provided that auto-negotiation is disabled). |

The Ethernet Interface Option allows communications and control access to all function modules either via the system BUS or Ethernet ports 1 or 2.

Ethernet 1 |

Ethernet 2 |

Ethernet 3* |

Ethernet 4* |

|

(REF PORT A) |

(REF PORT B) |

(REF PORT C) |

(REF PORT D) |

|

The default IP address: |

192.168.1.16 |

192.168.2.16 |

192.168.3.16 |

192.168.4.16 |

The default subnet: |

255.255.255.0 |

255.255.255.0 |

255.255.255.0 |

255.255.255.0 |

The default gateway: |

192.168.1.1 |

192.168.2.1 |

192.168.3.1 |

192.168.4.1 |

*see Part Number Designation for applicability.

|

Note

|

Actual "as shipped" card Ethernet default IP addresses may vary based upon final ATP configuration(s). |

The NAI interface supports IPv4 and IPv6 and both the TCP and UDP protocols. The Ethernet Operation Mode Command Listener application running on the motherboard host processor implements the operation interface. The listener is operational on startup through the nai_MBStartup process and listen on specific ports for commands to process. The default ports are listed below:

-

TCP1 - Port 52801

-

TCP2 - Port 52802

-

UDP1 - Port 52801

-

UDP2 - Port 52802

While the listener is active, note that interrupts from the motherboard do not trigger. The listener can be disabled by turning off the nai_MBStartup process through the Motherboard EEPROM. To turn off nai_MBStartup use the command mbeeprom_util set MBStartupInitOnlyFlag 1 in the console, either by serial port or telnet to the motherboard, and then reboot the system. To turn on the nai_MBStartup use the command mbeeprom_util set MBStartupInitOnlyFlag 0 in the console, either by serial port or telnet to the motherboard, and then reboot the system.

Ethernet Message Framework

The interface uses a specific message framework for all commands and responses. All messages begin with a Preamble code and end with a Postamble code. The message framework is shown below.

|

Preamble 2 bytes Always 0xD30F |

SequenceNo 2 bytes |

Type Code 2 byte |

Message Length (2 bytes) |

Payload (0..1414 bytes) |

Postamble 2 bytes Always 0xF03D |

Message Elements

Preamble |

The Preamble is used to delineate the beginning of a message frame. The Preamble is always 0xD30F. |

SequenceNo |

The SequenceNo is used to associate Commands with Responses. |

Type Code |

Type Codes are used to define the type of Command or Response the message contains. |

Message Length |

The Message Length is the number of bytes in the complete message frame starting with and including the Preamble and ending with and including the Postamble. |

Payload |

The Payload contains the unique data that makes up the command or response. Payloads vary based on command type. |

Postamble |

The Postamble is use to delineate the end of a message frame. The Postamble is always 0xF03D. |

Notes

-

The messaging protocol applies only to card products.

-

Messaging is managed by the connected (client) computer. The client computer will send a single message and wait for a reply from the card. Multiple cards may be managed from a single computer, subject to channel and computer capacity.

Board Addressing

The interface provides two main addressing areas: Onboard and Off-board.

Onboard addressing refers to accessing resources located on the board that is implementing the operation interface (including its modules).

Off-board addressing refers to accessing resources located on another board reachable via VME, PCI, or other bus. Off-board addressing requires a Master/Slave configuration.

The user must always specify if a particular address is Onboard or Off-board. See the command descriptions for the onboard and off-board flags.

Within a particular board (Onboard or Off-board), the address space is broken up into two areas: Motherboard Common Address Space and Module Address Space. All addresses are 32-bit.

Motherboard Common Address Space starts at 0x00000000 and ends at 0x00004000. This is a 4Kx32-bit address space (16 kbytes).

Module Address Space starts at 0x00004000. Module addressing is dynamically configured at startup. NAI boards support between 1 and 6 modules. The minimum module address space size is 4Kx32 (16 kbytes) and module sizes are always a multiple of 4Kx32.

Module addressing is dynamic and cumulative. The first detected module (starting with Slot 1) is given an address of 0x00004000. The 2nd detected Module is given an address of:

First_Detected_Module_Address + First_Detected_Module_Size

|

Note

|

Slots do not define addresses. |

If no module is detected in a module slot, that slot is not given an address. Therefore, if the first detected Module is in Slot 2, then that module address will be 0x00004000. If the next detected module is in Slot 4, then the address of that Module will be:

Second_Detected_Module_Address = First_Detected_Module_Address + First_Detected_Module_Size

If a 3rd Module is detected in Slot 6, then the address of that Module will be:

Third_Detected_Module_Address = Second_Detected_Module_Address + Second_Detected_Module_Size

|

Note

|

Module addresses are calculated at each board startup when the modules are detected. Therefore, if a module should fail to be detected due to malfunction or because it was removed from the motherboard, the addresses of the modules that follow it in the slot sequence will be altered. This is important to note when programming to this interface. |

Users can always retrieve the Module Addresses, Module Sizes and Module IDs from the fixed Motherboard Common address area. This data is set upon each board startup. While the Module Addressing is dynamic, the address where these addresses are stored is fixed. For example, to find the startup address of the module location in Slot 3, refer to the MB Common Address 0x00000408 from the Motherboard Common Addresses table that follows.

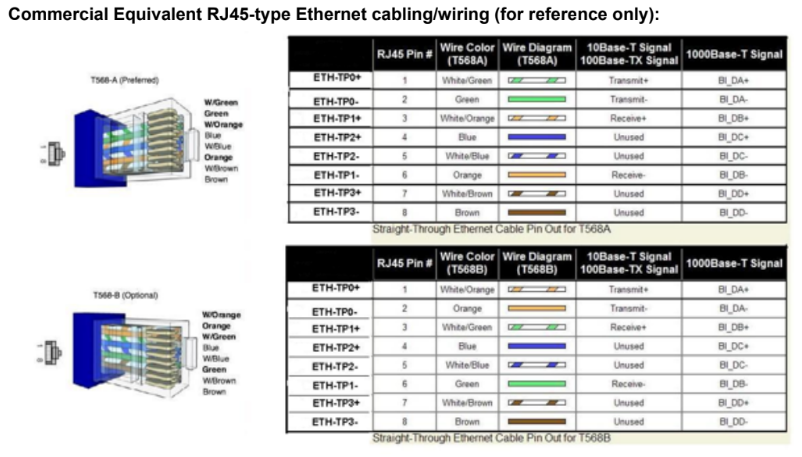

Ethernet Wiring Convention

RJ-45 Pin |

T568A Color |

T568B Color |

10/100Base-T |

1000BASE-T |

NAI wiring convention |

1 |

white/green stripe |

white/orange stripe |

TX+ |

DA+ |

ETH-TP0+ |

2 |

green |

orange |

TX- |

DA- |

ETH-TP0- |

3 |

white/orange stripe |

white/green stripe |

RX+ |

DB+ |

ETH-TP1+ |

4 |

blue |

blue |

DC+ |

ETH-TP2+ |

|

5 |

white/blue stripe |

white/blue stripe |

DC- |

ETH-TP2- |

|

6 |

orange |

green |

RX- |

DB- |

ETH-TP1- |

7 |

white/brown stripe |

white/brown stripe |

DD+ |

ETH-TP3+ |

|

8 |

brown |

brown |

DD- |

ETH-TP3- |

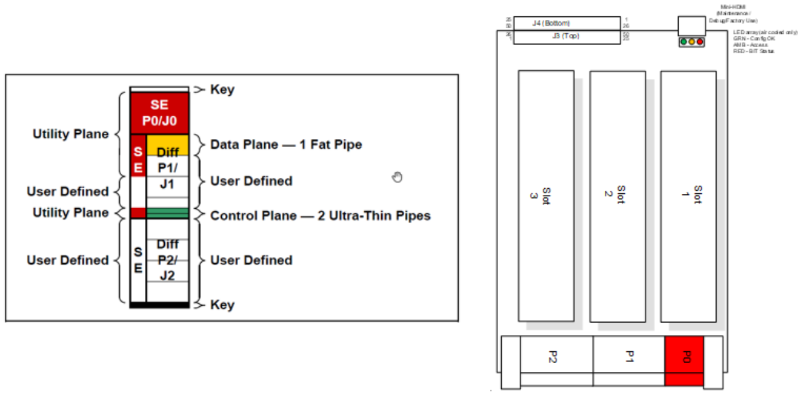

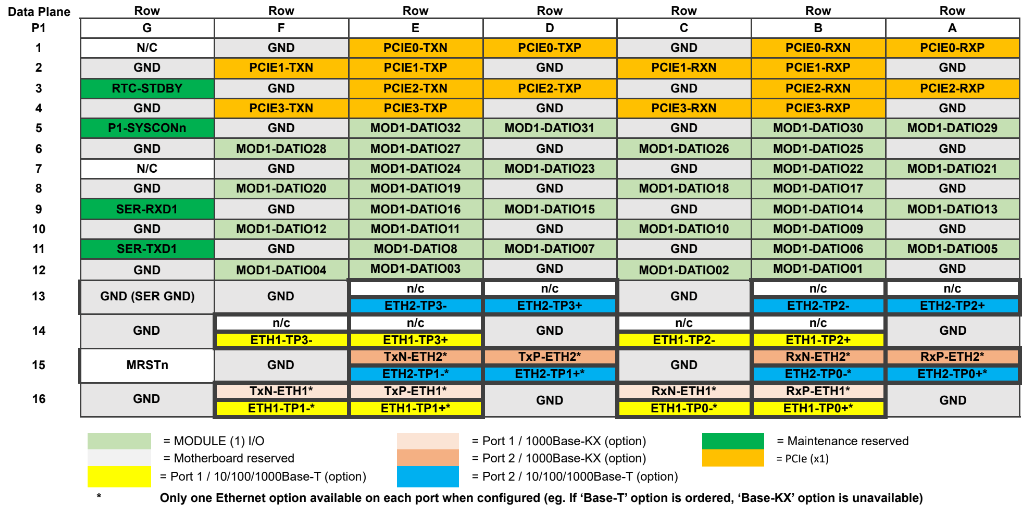

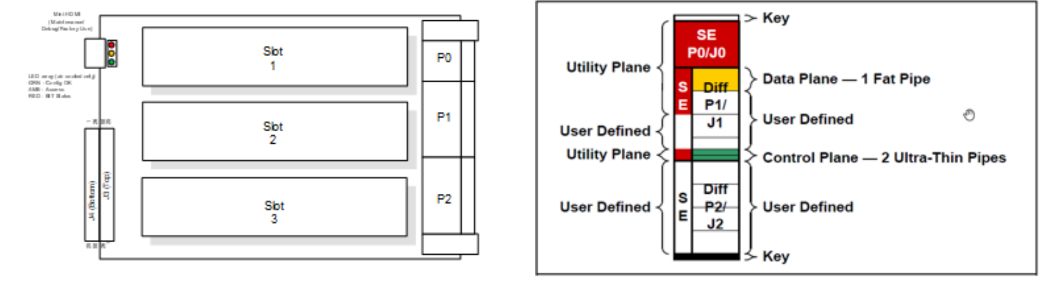

68ARM1 CONNECTOR/PIN-OUT INFORMATION

Front and Rear Panel Connectors

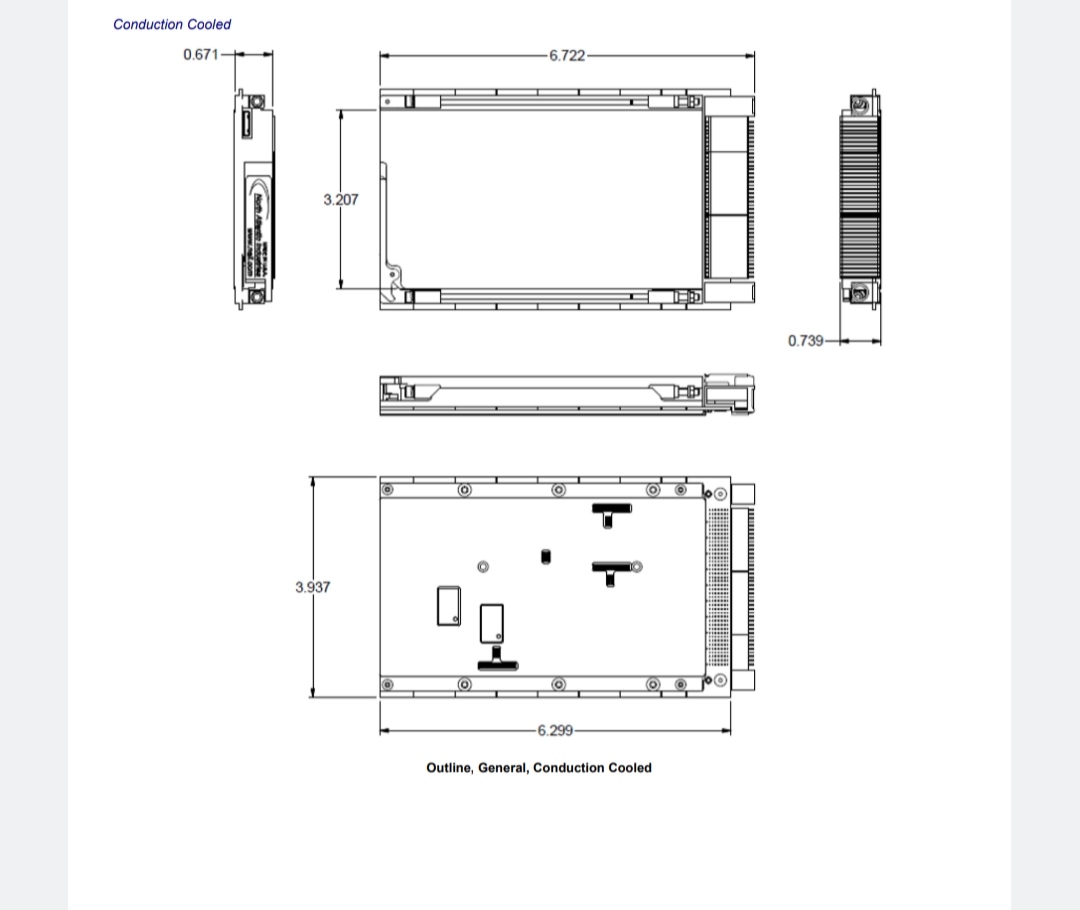

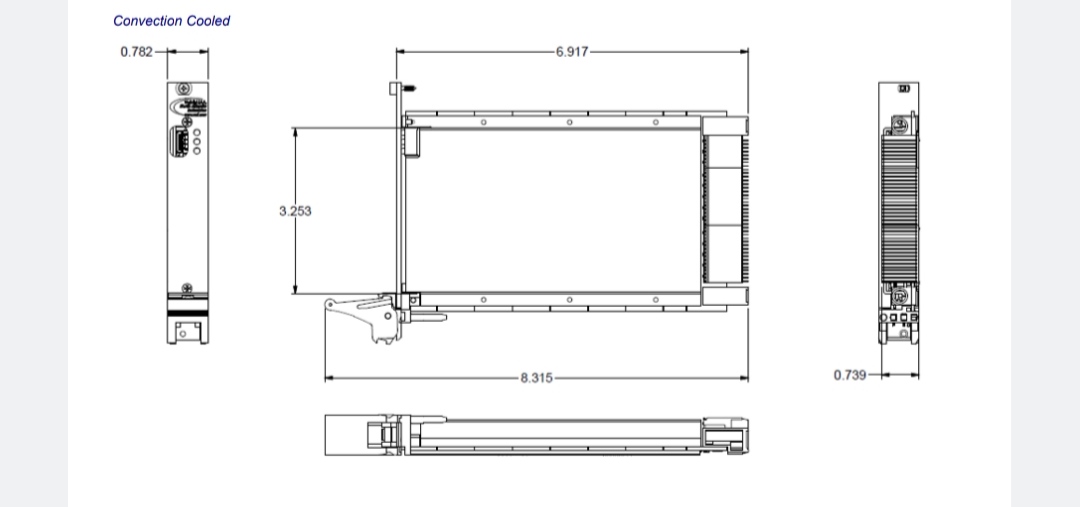

The 68ARM1 3U OpenVPX SBC & Multifunction I/O board is available in two configurations: convection-cooled and conduction-cooled. The 68ARM1 follows the OpenVPX “Payload Slot Profile” configured as:

Slot profile: SLT3-PAY-1F2U-14.2.12

Module profile: MOD3-PAY-1F2U-16.2.11-2

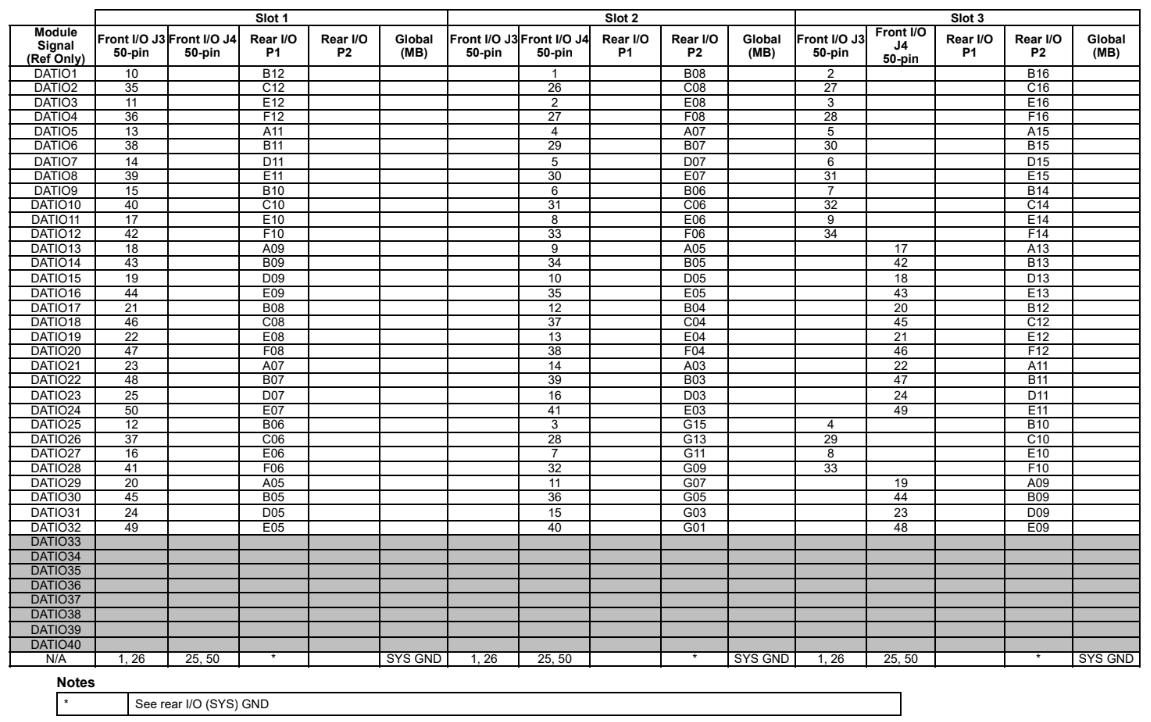

User I/O is available through the (J3, J4) front panel connectors when card is configured with front panel I/O and through the OpenVPX user defined rear I/O connectors P1, P2 (see part number and pin-out information).

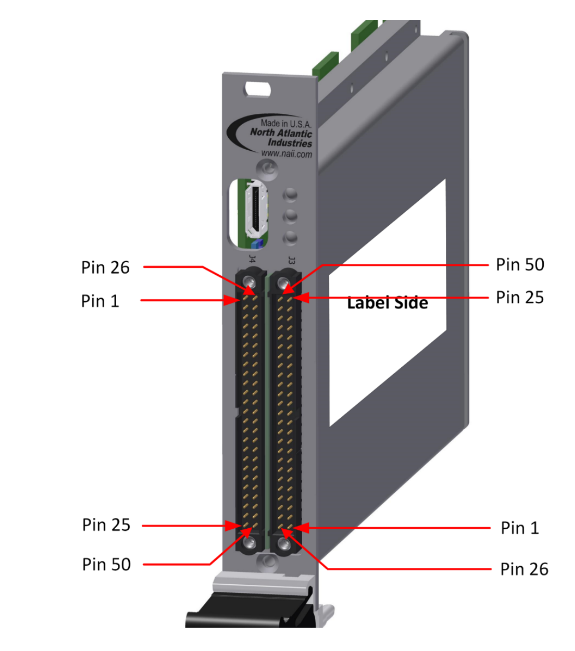

Front Panel Connectors J3, J4 (Convection-Cooled)

50-pin male connectors, 2 mm, Harwin P/N M80-5S25022M3.

Mate kit: Harwin M80-486 product family (mating connector kit is available from Harwin as P/N M80-9415005). This mating connector may be purchased separately under NAI P/N 05-0118 (contact factory).

Panel LEDs

Front Panel LEDs indications (only available on air-cooled units).

LED |

ILLUMINATED |

EXTINGUISHED |

GRN |

Blinking: initializing Steady On: Power-On/Ready |

Power Off |

RED |

Module BIT error |

No BIT fault |

YELLOW (flashing) |

Card Access (bus or Gig-E activity) |

No card activity |

Chassis Ground

Front Panel: No dedicated chassis GND pins available. Jack screw sockets are chassis GND.

Rear connector key guides are chassis ground.

Front Panel System (Power/Signal) Ground Reference

Front Panel: J3 pins 1, 26; J4 pins 25, 50 (connected to card power/system ground).

Front I/O Utility Connector J5 (Convection and Conduction-Cooled)

The 68ARM1 utilizes a Mini-HDMI (Type-C) type card edge connector J5, available on either convection or conduction-cooled configurations that provides the following signals:

-

USB

-

Serial (RS-232 debug/console only)

-

Ethernet port 1 (factory configuration option – Ethernet port1 may be redirected to rear I/O J2)

NAI also provides an optional “breakout” adapter board (NAI P/N 75SBC4-BB) with a mini-HDMI to mini-HDMI type cable. The “breakout” adapter board and a Micro-HDMI cable (NAI P/N 75SBC4-BB) allow for standard I/O connections to Ethernet and asynchronous serial (DB9). Consult the factory for availability.

| Front J5 | Standard Configuration |

|---|---|

J5-01 |

N/C |

J5-02 |

ETH1-TP0+ (option) |

J5-03 |

ETH1-TP0- (option) |

J5-04 |

N/C |

J5-05 |

ETH1-TP1+ (option) |

J5-06 |

ETH-TP1- (option) |

J5-07 |

N/C |

J5-08 |

ETH1-TP2+ (option) |

JT-09 |

ETH1-TP2- (option) |

J5-10 |

N/C |

J5-11 |

ETH1-TP3+ (option) |

J5-12 |

ETH1-TP3- (option) |

J5-13 |

GND |

J5-14 |

+5V-USB |

J5-15 |

USB-DP |

J5-16 |

USB-DM |

J5-17 |

SER1-RXD |

J5-18 |

SER1-TXD |

J5-19 |

GND |

|

Note

|

N/C = not connected |

Signal Descriptions J5

Signal Name |

Description |

ETH1-TPx |

Ethernet port 1 signals (4 pair) 10/100/1000 twisted pair signals (Optional - available only if NOT re-directed to rear I/O (see part number configuration options) |

USB-DP |

Front Panel USB Data Plus |

USB-DM |

Front Panel USB Data Minus |

SER1-TXD |

Asynchronous transmit serial data port 1 (out) / RS232 debug/console port only |

SER1-RXD |

Asynchronous received serial data port 1 (in) / RS232 debug/console port only |

GND |

System Ground (return) |

Rear I/O VPX Connectors P0-P2 (Conduction-Cooled)

The 68ARM1 3U OpenVPX SBC and Multifunction I/O board provides interface via the rear VPX connectors.

Rear I/O Summary

P0 - Utility plane. Contains the following signal definitions:

Power: |

Primary +5V, +3.3V_AUX, +/- 12V and System GND |

Geographical Address Pins: |

GA0# - GA4#, GAP# |

Card reset: |

SYSRST# signal |

VPX AUX/REF CLK |

(as/if applicable) |

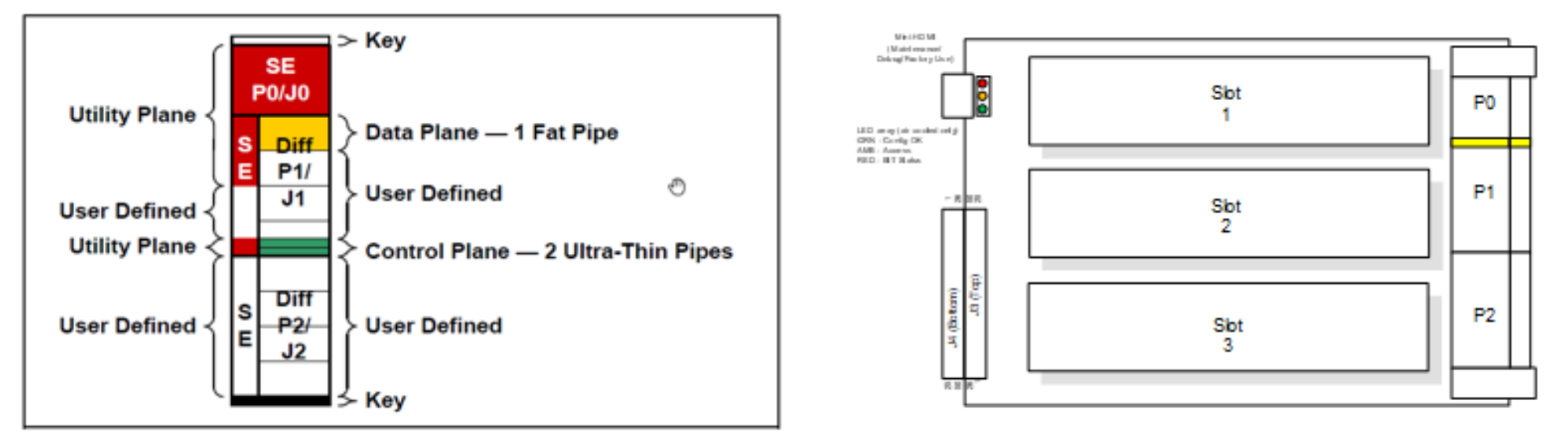

P1 - Defined as primarily Data/Control Planes (User defined I/O secondary)

High Speed Switched Fabric Interface: |

Root-complex ultra-thin pipes; four (4) PCIe ver. 2.0 (x1) ports. |

Ethernet: |

Dual Gig-E port option(s) are available and defined (See Part Number Designation section) |

P2 - User defined I/O (primary)

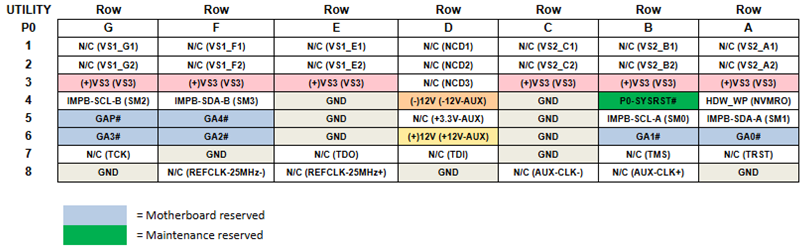

Rear I/O Utility Plane (P0)

The P0 (Utility) Plane contains the primary power, bus and utility signals for the OpenVPX board. Additionally, several of the user defined pins can be utilized for Geographical Addressing and a parallel SYSRST# signal. Signals defined as N/C currently have no functionality associated and is not required for general operation.

Rear I/O Data/Control Planes (P1)

The 68ARM1 is a root-complex SBC with four (4) PCIe ver. 2.0 x1 high-speed serial interface fabric bus lanes. As defined in the OpenVPX payload slot specifications, the 68ARM1 provides four 'ultra-thin pipe' (one Tx and one Rx differential pair), which provides additional user I/O definition opportunity. Additionally, the 68ARM1 can be commanded/controlled via dual port Gig-E (options for either 10/100/1000Base-T and/or 1000Base-KX (SerDes) Interfaces). Additional module I/O is also defined on the P1 user defined plane. Signals defined as N/C currently have no functionality associated or are considered optional and are not required for general operation.

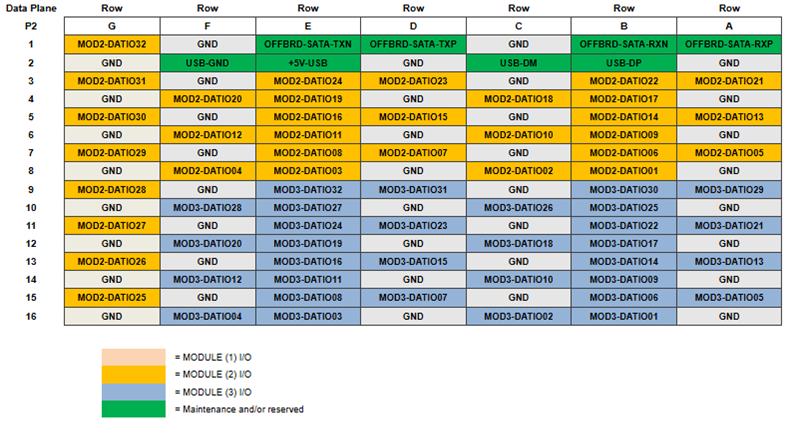

USER I/O - Defined Area (User Defined I/O) (P2)

The following pages contain the ‘user defined’ I/O data area front and rear panel pin-outs with their respective signal designations for all module types currently offered/configured for the 68ARM1 platform. The card is designed to route the function module I/O signals to the front and rear I/O connector. The following I/O connector pin-out is based upon the function module designated in the module slot. Signals defined as N/C currently have no functionality associated or are considered optional and are not required for general operation.

J3/J4 Front Panel Connector Pinout Mapping Summary (Convection-Cooled)

The following provides connector/pinout data for Front Panel connectors J3 and J4. Each connector provides 50 pins of I/O.

Front Panel Connectors J3/J4 Generic User I/O Mapping

(System Ground REF) |

GND |

1 |

26 |

GND |

(System Ground REF) |

M3_DAT01 |

S-MOD-M3-DAT01 |

2 |

27 |

S-MOD-M3-DAT02 |

M3_DAT02 |

M3_DAT03 |

S-MOD-M3-DAT03 |

3 |

28 |

S-MOD-M3-DAT04 |

M3_DAT04 |

M3_DAT25 |

S-MOD-M3-DAT25 |

4 |