VR1 Manual

Edit this on GitLab

INTRODUCTION

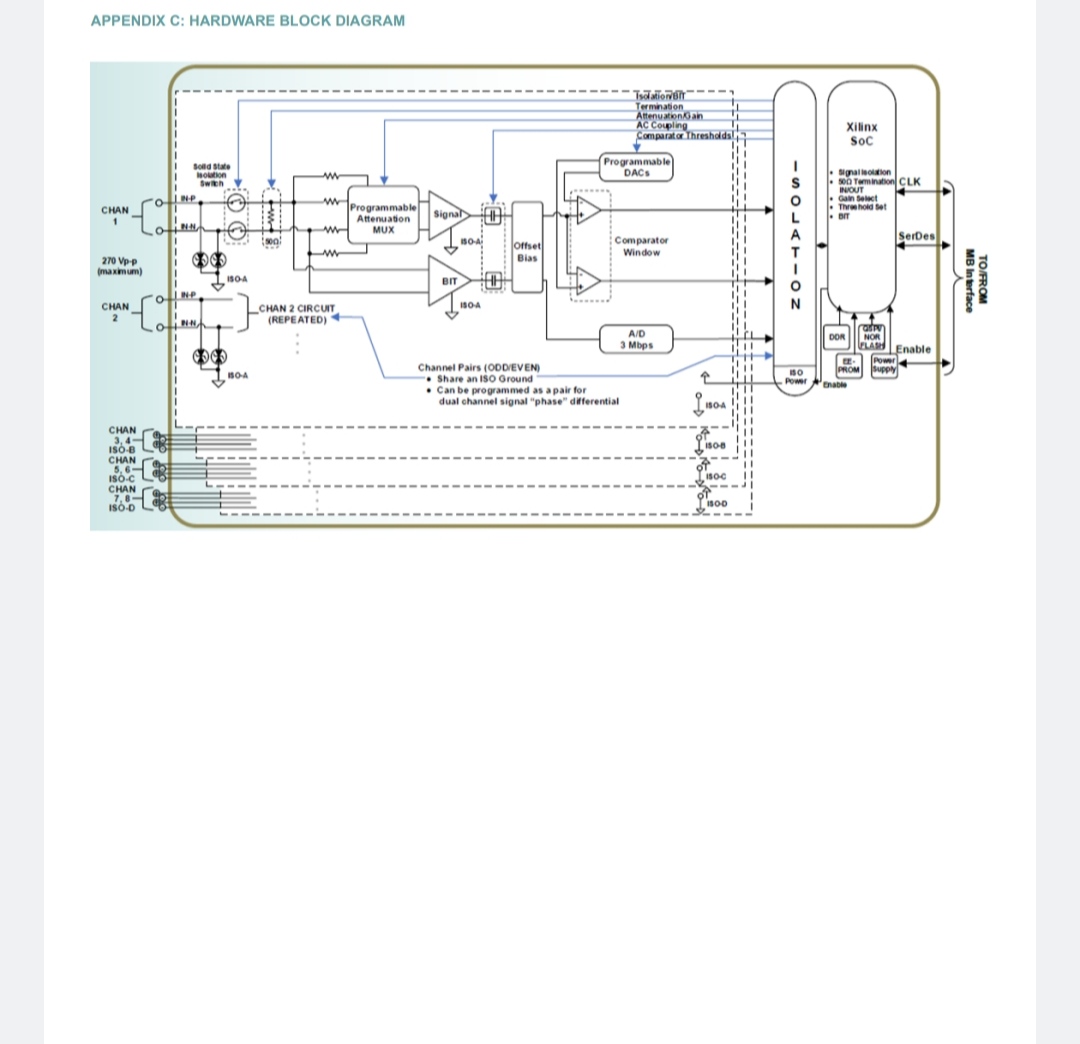

This module manual provides information about the North Atlantic Industries, Inc. (NAI) Variable Reluctance and General-Purpose Pulse Counter Module: VR1. This module is compatible with all NAI Generation 5 motherboards.

VRS (Variable Reluctance Speed) sensors are designed to detect the speed and position of rotating shafts. These passive VRS sensors are simple, rugged devices that do not require an external voltage source for operation. A permanent magnet in the sensor establishes a fixed magnetic field. The approach and passing of a ferrous metal target near the sensor’s pole piece (sensing area) changes the flux of the magnetic field, dynamically changing its strength. This change in magnetic field strength induces a current into a coil winding which is attached to the output terminals. The output signal of a VRS sensor is an AC voltage that varies in amplitude and frequency as the speed of the monitored device changes and is usually expressed in peak-to-peak voltage (Vp-p). One complete cycle occurs as each tooth passes the sensor’s pole piece.

The signal characteristics of the VR sensor can vary greatly with the speed and proximity of the sensor pickup in relation to the shaft. The VR1 sensor interface is ideal for speed sensing for aircraft, marine or automotive crankshafts, camshafts, brake or gear rotors, transmission shafts, etc. The VR1 provides the measurement basis for linear velocity, angular velocity, and torque. The VR1 interface channels are uniquely designed to compensate for the inherent, typically 'less-than-ideal', sensor output signal characteristics. The VR1 integrates a programmable high-gain front end precision amplifier and comparator with adaptive threshold and conditioning circuits that discern and re-define the pulses, even in the presence of substantial system noise or extremely weak VR signals. In paired mode, the conditioned channel pulses, with high slew rates, provide channel-to-channel pulse alignment, eliminating sources of timing error. Paired mode provides the ability to calculate shaft torque by measuring the shaft 'twist angle' resulting from the period measurement between the two channel pulses.

The VR1 is also uniquely designed to process signals as general-purpose counter, that can operate and process a wide variety of AC and Pulse input signals as high as ±100 V*. The VR1 is capable of measurements with signal frequencies to 1 MHz (4 MHz is potentially achievable based upon settings e.g. minimal filtering). With auto threshold and auto ranging modes enabled, max operational frequencies to 20 kHz is achievable.

|

Note

|

for modules with FPGA rev 1.x, the input voltage range is ±60 V. |

The VR1 provides eight isolated, wide voltage input range Variable Reluctance (VR) signal or general-purpose Pulse Counter measurement interfaces. Channels can be programmed to operate individually or combined in pairs.

Clarifying Terms:

VR (variable reluctance) sensors are known by many other application-specific names. A few examples are:

Magnetic-pickups, Speed sensors, Motion sensors, Pulse generators, Frequency generators, Transducers, Magnetic probes, Timing probes, Monopoles and Pickoffs.

Clarifying Operation Modes:

Monopole sensor type = single sensor pulse train

Dipole sensor type = dual sensor pulse train (can be a single channel interlaced input on Monopole type/mode dual paired channels). Dipoles typically refers to any measurements involving phase (twist, torque), whether in the single channel or dual paired channels modes.

The VR1 can be used for the following signal/pulse measurements:

“Monopole” is defined as the Single Sensor Pulse Train signal type (typically, for measuring RPM, frequency, etc.) - this is defined as a reference term within this document.

“Dipole” will be defined as the Double Pulse signal type (typically, for discerning phase between the double signal pulses for torque/twist measurement) - this is defined as a reference term within this document.

|

Note

|

The “Dipole” signal type can be generated (and will be measured) via a single independent composite signal (one signal, with two interlaced sensor inputs) |

A dual set of independent signals (two distinct, yet dependent, synchronized signal inputs) where one can manage the measurement with the unique “paired channel mode”.

VR1 Overview

The VR1 module offers a wide range of features designed to suit a variety of system requirements. Some of the key features include:

Variable Reluctance Interface:

-

Eight (8) isolated, differential input channels: These channels provide flexibility in interfacing with various sensor types, ensuring compatibility with the user’s specific application requirements.

-

Independent or paired mode: The VR1 module allows you to configure these input channels independently or in paired mode, enhancing versatility in data acquisition.

-

Large voltage range input: With a range of ±100 V, the VR1 module accommodates a wide range of signal amplitudes, making it suitable for diverse applications.

-

Large pulse train detection: Achieve precise pulse counting with an effective resolution of 8 ns in 1 ns step settings, ensuring accurate data capture even in high-speed scenarios.

General Purpose Counter:

-

32-bit pulse counter: The VR1 boasts a 32-bit counter that enables high-resolution pulse counting.

-

Single channel increment: The VR1 module simplifies pulse counting by incrementing on a single channel, streamlining data acquisition tasks.

-

Frequency: The VR1 module is capable of measurements with signal frequencies up to 1 MHz (maximum, continuous).

|

Note

|

Depending on some settings, such as filtering, 4 Mbps is potentially achievable. With auto threshold and auto ranging modes enabled, the frequency limit reaches 20 kHz for a broader range of frequency measurement capabilities. |

-

Independent channel configuration: Tailor the VR1 module to interface seamlessly with different sensor types by adjusting programmable parameters. Choose between independent or paired mode configurations to suit your specific application needs.

-

Isolated channels: The VR1 module incorporates isolated channels to minimize the risk of false trigger counts due to electrical noise, ensuring data accuracy.

-

Built-in Test: The VR1 module comes with a built-in test feature, providing assurance of its operational integrity and reliability.

PRINCIPLE OF OPERATION

The VR1 module provides both Variable Reluctance and General-Purpose Counter capability. Programmable parameters allow for this module to be used on many different sensor types. In addition, the VR1 module includes internal built-in tests that provide monitoring of the circuitry.

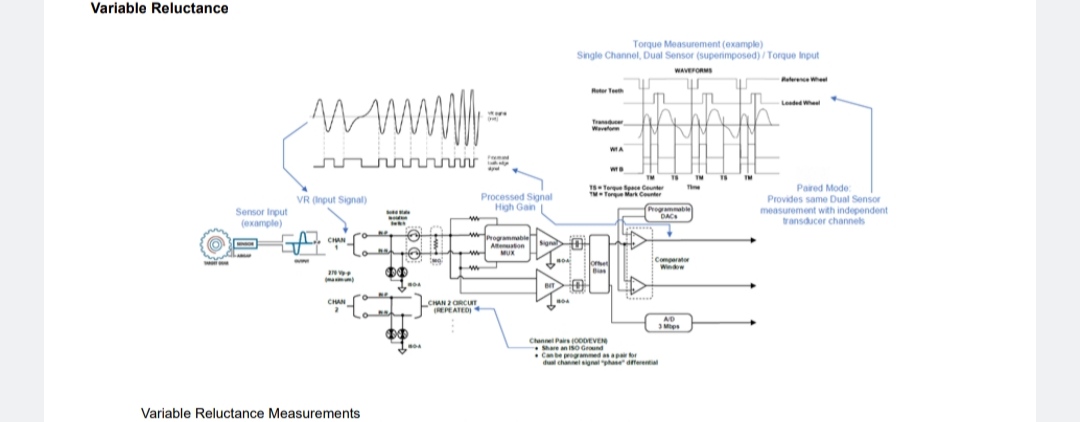

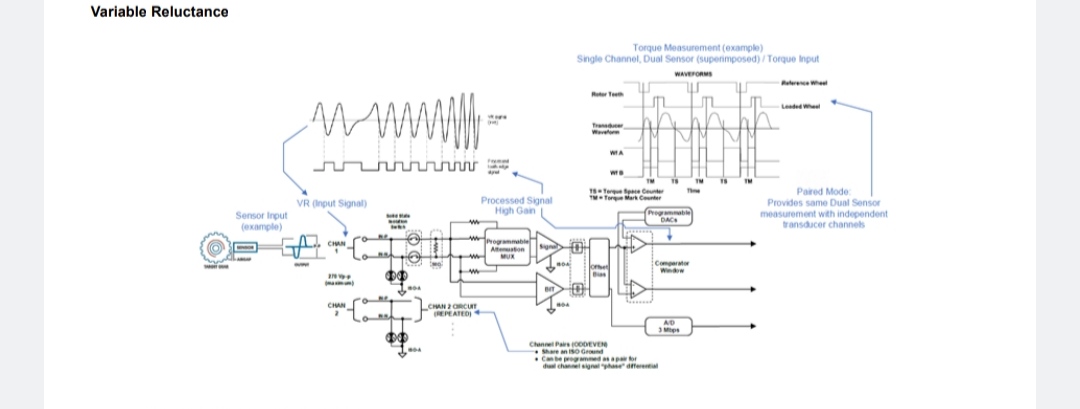

Variable Reluctance

Variable Reluctance Measurements

The VR1 provides several measurements of the signal characteristics including:

Monopole type/mode:

-

Signal Amplitude measured as the absolute value of the maximum positive or negative peak

-

Signal Frequency

-

Period of the signal

-

RPM based on number of teeth on wheel sensor

Dipole type/mode:

-

Phase measurement between interposed signal trains (either single or paired channel mode)

Monopole/Dipole

When operating in Dipole mode, the VR1 measures the relative phase between the two Dipole pulses on a single channel, reporting the smaller phase measurement to determine the change in phase from a user reference phase setting. This change is used to calculate the percentage torque reading.

For measurement stability, dipole phase readings crossing through the 0.0/180-degree transitions should be avoided. Optimal configuration is achieved with phase measurements centered about 90 degrees.

When operating in Monopole mode, the VR1 measures the relative phase between pulses on individual channels within channel pairs, reports the phase measurement, and determines the change in phase from a user reference phase setting. This is used for calculation of the percentage torque on a shaft.

For measurement stability, monopole phase readings crossing through the 0.0/360-degree transitions should be avoided. Optimal configuration is achieved with phase measurements centered about 180 degrees.

Sensor Characteristic Compensation

The following sensor signal parameters are programmable to adjust for different sensor type characteristics.

-

Programmable Voltage Range

-

Automatic Gain Control, to adjust amplifier gain, based on measured signal level.

-

Input transition High Threshold

-

Input transition Low Threshold

-

Polarity Select - Measure time from rising or falling edges.

-

AC-coupling Enable

-

Input Termination Enable

-

Measurement Averaging Time

-

Debounce Time

-

Monopole/Dipole Mode

General Purpose Counter

The VR1 can also be used as a general counter for a variety of AC or pulsed signal sensors including Hall effect sensors. Count up mode is presently supported by the module.

Status and Interrupts

The Variable Reluctance and General-Purpose Counter Function Module provide registers that indicate faults or events. Refer to “Status and Interrupts Module Manual” for the Principle of Operation description.

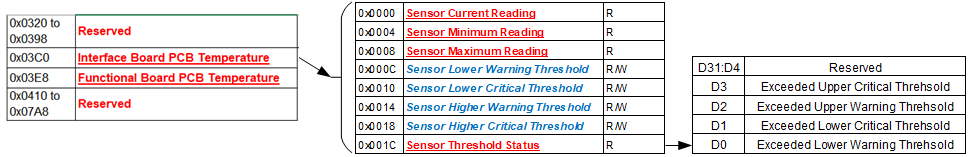

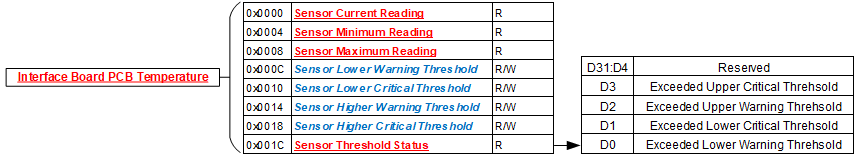

Module Common Registers

The Variable Reluctance and General-Purpose Counter Function Module include module common registers that provide access to module-level bare metal/FPGA revisions & compile times, unique serial number information, and temperature/voltage/current monitoring. Refer to “Module Common Registers Module Manual” for the detailed information.

REGISTER DESCRIPTIONS

The register descriptions provide the register name, Type, Data Range, Read or Write information, Initialized Value, a description of the function and, in most cases, a data table.

VR/Counter Measurement Registers

The measurements of the input signal to the Variable Reluctance/Counter can be read from the registers described in this section.

Measured Period

Function: |

This value is the measured period of the input signal per individual channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 1 nanosecond. |

Measured Phase

Function: |

This value is the phase measurement of a Dipole input signal per individual channel or if the Dipole Enable register is set for Monopole mode, this is the phase measurement with respect to the channel it is paired with (when using Paired Channel Mode) |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0x0005 7E3F (0 to 359.999º) |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 0.001°. |

Measured Percent Torque

Function: |

This value is the percent torque measurement of the input signal per individual channel calculated as follows: Percent Torque = 100 * (Phase Measurement - Zero Torque Signal Phase) / Max Torque Signal Phase |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 0.001%. |

Measured Amplitude

Function: |

This value is the absolute value of the maximum positive or negative signal peak amplitude of the input signal per individual channel measured by peak sampling of the input signal. Peak detected values are recorded on an ongoing basis at 1 second intervals. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 1 mV. |

Measured Frequency

Function: |

This value is the measured frequency of the input signal per individual channel. NOTE: the frequency readings in dipole mode will be half the apparent frequency as dual-timing references are assumed to be interleaved on the single channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 0.001 Hz. |

Measured RPM

Function: |

This value is the measured velocity in RPM (rotations/minute) of the shaft per individual channel. The velocity is based the on Number of Teeth setting for the individual channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 0.001 RPM. |

Measured Cycle Count

Function: |

Reads the cycle counter, which counts the number of signal transitions of the channel since it was last reset. The cycle counter will roll over to a '0' count on the next count following a 0xFFFF FFFF terminal count. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Read/Write: |

R |

Initialized Value: |

0x0000 0000 |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF |

Operational Settings: |

Integer Mode: LSB is 1 cycle. |

VR/Counter Control Registers

Control of the Variable Reluctance/Counter features are based on the configuration of the registers in this section.

Power Supply Enable

Function: |

Enables the VR1 module. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 0001 |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0001 (Channel power is enabled) |

Operational Settings: |

Set bit to 1 to enable the power. Set bit to 0 to disable the power. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

Channel Enable

Function: |

Enables the channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 00FF (all channels enabled) |

Operational Settings: |

Set bit to 1 to enable the channel. Set bit to 0 to disable the channel. When both channels of an unused channel pair are disabled, channel operations are suspended for a reduction in power requirements. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Dipole Enable

Function: |

Enables a single channel to be used for reading a dipole VR sensor. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (default is considered “paired channel mode” or “combined signal disabled”) |

Operational Settings: |

Sets what type of sensor is being interfaced to, where 0 = Monopole and 1 = Dipole. In default Monopole mode (Dipole Enable = 0), the channel 1’s phase is measured with respect to channel 2 (a.k.a Paired Mode). Channels are paired in groups of two. Pairs are (1,2) (3,4) (5,6) (7,8). Setting this bit (Dipole Enable = 1) makes the channel independent of its paired channel and assumes that both signals are combined on the selected channel. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Falling Edge Measurement Enable

Function: |

Sets the signal edge on which to take measurements on the channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (rising edge) |

Operational Settings: |

Set bit to 1 to measure on falling edge for that channel. Set bit to 0 to measure on rising edge. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Termination Enable

Function: |

Enables Termination on the channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (all channels unterminated) |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

AC Couple Enable

Function: |

Enables AC Coupling on the channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (all channels DC coupled) |

Operational Settings: |

Set bit to 1 to enable AC coupling on the channel. Set bit to 0 for DC coupling. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Range Select

Function: |

Selects the signal gain, which sets the effective measuring range on the channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (auto range) |

Operational Settings: |

Set 4-bit groups to select the signal gain for the specified channel. e.g. 0xAA0 will set channels 2 and 3 to 50V range. Set bit group to 0 for auto ranging. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Ch8 |

Ch8 |

Ch8 |

Ch8 |

Ch7 |

Ch7 |

Ch7 |

Ch7 |

Ch6 |

Ch6 |

Ch6 |

Ch6 |

Ch5 |

Ch5 |

Ch5 |

Ch5 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Ch4 |

Ch4 |

Ch4 |

Ch4 |

Ch3 |

Ch3 |

Ch3 |

Ch3 |

Ch2 |

Ch2 |

Ch2 |

Ch2 |

Ch1 |

Ch1 |

Ch1 |

Ch1 |

Channel Value |

Range |

0x0 |

Auto Range |

0x1 |

±50mV |

0x2 |

±100mV |

0x3 |

±250mV |

0x4 |

±500mV |

0x5 |

±1V |

0x6 |

±2.5V |

0x7 |

±5V |

0x8 |

±12.5V |

0x9 |

±25V |

0xA |

±50V |

0xB |

±100V |

Auto Down-Range Time

Function: |

Sets the amount of time for the auto-ranging detection to down-range (increase the gain). |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Initialized Value: |

0x2 (1s) |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Channel Value |

Range |

0x0 |

100 ms |

0x1 |

500 ms |

0x2 |

1 s |

0x3 |

2 s |

0x4 |

5 s |

0x5 |

10 s |

Number of Teeth

Function: |

Sets the number of teeth on the reluctor ring, which is used for RPM calculations. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF Integer Mode: LSB is 1 tooth. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0001 |

Operational Settings: |

Sets the number of teeth for the channel. |

Zero Torque Signal Phase

Function: |

Sets the zero-torque signal phase value to use for torque calculations of the channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF Integer Mode: LSB is .001°. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (0°) |

Operational Settings: |

Sets the zero-torque signal reference used for torque calculations. This register can be also set automatically by strobing the set zero torque signal phase register, to transfer the current reading and null the torque value. |

Zero Torque Signal Phase to Phase Reading

Function: |

Sets the current phase as the zero-torque signal phase value for the channels. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF Read/Write: |

Read/Write: |

W (always reads 0x0000 0000) |

Initialized Value: |

0x0000 0000 |

Operational Settings: |

Set bit to 1 to transfer the present phase readings to the zero-torque signal phase settings for the specified channels. This allows for nulling of the torque reading to zero for the present conditions. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Max Torque Signal Phase

Function: |

Sets the max torque signal phase value to use for torque calculations for the channel. This is a scaling value that represents the amount of change in the phase measurement from the Zero Torque Signal Phase reference setting for 100% torque. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF Integer Mode: LSB is .001°. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 03E8 (1°) |

Operational Settings: |

Sets the max torque signal value to use for torque calculations for the channel. |

Averaging Time

Function: |

Sets the averaging time for all readings of the channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (no averaging) |

Operational Settings: |

Sets the averaging time for the channel. Higher averaging times provide improved accuracy and measurement stability, with longer update rates. |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF Integer Mode: LSB is 1us. |

Debounce Time

Function: |

Sets the debounce time for all readings of the channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF Integer Mode: LSB is 1ns, with effective debounce gradations of 8ns implemented. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (no debounce) |

Operational Settings: |

Sets the debounce time for the channel, to reject spurious noise transitions. |

Voltage Threshold High

Function: |

Sets the high threshold voltage, used in the input comparator of the channel. |

Type: |

2’s compliment (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0x0001 7318 Integer Mode: LSB is 1mV. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (0V) |

Operational Settings: |

Sets the high threshold trigger voltage for the channel. The operational range should be limited to +95V. |

Voltage Threshold Low

Function: |

Sets the low threshold voltage, used for the input comparator of the channel. |

Type: |

2’s compliment (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0xFFFE 8CE8 to 0xFFFF FFFF Integer Mode: LSB is 1mV. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (0V) |

Operational Settings: |

Sets the Voltage Threshold Low for the channel. The operational range should be limited to -95V. |

Minimum Amplitude

Function: |

Sets the minimum amplitude threshold for triggering a signal loss status on the channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF Integer Mode: LSB is 1mV. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (0V) |

Operational Settings: |

Sets the Minimum Amplitude for the channel. Suggested operational range is 0V to 100V. |

Minimum Frequency

Function: |

Sets the minimum frequency threshold for triggering a signal loss status on the channel. |

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0xFFFF FFFF Integer Mode: LSB is .001Hz. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 00FA (.25Hz) |

Operational Settings: |

Sets the Minimum Frequency for the channel. |

Reset Cycle Count

Function: |

Resets the cycle count value for the channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

W (always reads 0x0000 0000) |

Initialized Value: |

0x0000 0000 |

Operational Settings: |

Set bit to 1 to reset the cycle count value for the specified channels. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Auto Threshold Percent

Function: |

Sets the percent of peak amplitude to set the active edge threshold in auto threshold mode of the channel. |

Type: |

2’s compliment (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0x0001 86A0 Integer Mode: LSB is .001%. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (0%) |

Operational Settings: |

Sets the percent of peak amplitude to set the active edge threshold in auto threshold mode of the channel. The maximum value is 100% (0x186A0). |

Auto Threshold Hysteresis

Function: |

Sets the percentage of hysteresis to set the opposite edge threshold in auto threshold mode of the channel. |

Type: |

2’s compliment (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

(Integer Mode): 0x0000 0000 to 0x0001 86A0 Integer Mode: LSB is .001%. |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (0%) |

Operational Settings: |

Sets the Auto Threshold Hysteresis for the channel. The opposite edge threshold is used to reset the trigger detection circuit. Larger values afford greater immunity from multiple trigger events due to noise but should be set low enough for proper response with low signal amplitudes. The maximum value is 100% (0x186A0). |

Auto Threshold Enable

Function: |

Enables automatic threshold levels for the channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R/W |

Initialized Value: |

0x0000 0000 (disabled) |

Operational Settings: |

Set bit to 1 to enable auto threshold for the channel and automatically set input gain range based on the detected signal. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Unit Conversion Programming Registers

The Enable Floating Point register provides the ability to read the measurement registers as floating-point values. The purpose for this feature is to offload the processing that is normally performed by the mission processor to convert the integer values to floating-point values.

Enable Floating Point Mode

Function: |

Sets all channels for floating point mode or integer module. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0 to 1 |

Read/Write: |

R/W |

Initialized Value: |

0 |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

D |

D |

D |

D |

D |

D |

D |

Floating Point State

Function: |

Indicates the state of the mode selected (Integer or Floating Point). |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0 to 1 |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

Indicates the whether the module registers are in Integer (0) or Floating Point Mode (1). When the Enable Floating Point Mode is modified, the application must wait until this register’s value matches the requested mode before changing the values of the configuration and control registers with the values in the units specified (Integer or Floating Point). |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

Test Registers

The Variable Reluctance module provides the ability to run an initiated test (IBIT).

Test Enable

Function: |

Set bit IBIT to enable the associated Initiated Built-In-Test. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0 to 0x0000 0008 |

Read/Write: |

R/W |

Initialized Value: |

0x0 |

Operational Settings: |

Command strobe for Initiated BIT test. Writing 0x8 to set bit D3 in the register will initiate an internal test on all enabled channels, taking approximately 1 ms to complete. Channel operations will be offline during the test. The register will read back 0 upon completion. Failures in the BIT test are reflected in the BIT Status registers for non-compliant channels. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

IBIT |

0 |

0 |

0 |

Module Common Registers

Refer to “Module Common Registers Module Manual” for the register descriptions.

Status and Interrupt Registers

The VR1 Module provides status registers for BIT, Termination Fault, Signal Loss and Summary Status.

Channel Status Enabled

Function: |

Determines whether to update the status for the channels. This feature can be used to “mask” status bits of unused channels in status registers that are bitmapped by channel. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 00FF (Channel Status) |

Read/Write: |

R/W |

Initialized Value: |

0x0000 00FF |

Operational Settings: |

When the bit corresponding to a given channel in the Channel Status Enabled register is not enabled (0) the status will be masked and report “0” or “no failure”. This applies to all statuses that are bitmapped by channel (BIT Status, Termination Fault Status and Summary Status). |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

BIT Status

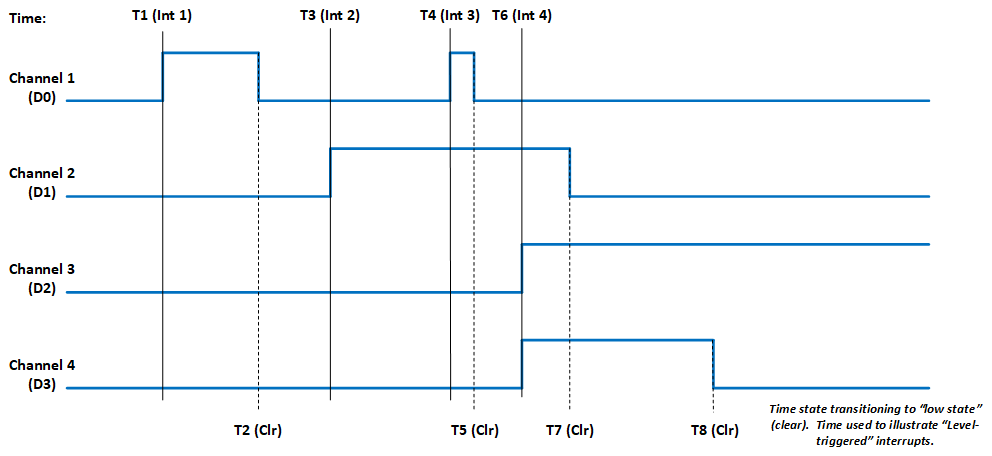

There are four registers associated with the BIT Status: Dynamic Status, Latched Status, Interrupt Enable, and Set Edge/Level Interrupt.

Function: |

Sets the corresponding bit associated with the channel’s BIT error. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt) |

Initialized Value: |

0 |

BIT Set Edge/Level Interrupt |

|||||||||||||||

BIT Interrupt Enable |

|||||||||||||||

BIT Latched Status |

|||||||||||||||

BIT Dynamic Status |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Termination Fault Status

There are four registers associated with the Termination Fault Status: Dynamic Status, Latched Status, Interrupt Enable, and Set Edge/Level Interrupt.

Function: |

Status for termination fault. If the input voltage exceeds 5 volts while termination is enabled, the bit associated with that channel will be set to a 1. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt) |

Initialized Value: |

0x00000000 |

Termination Fault Set Edge/Level Interrupt |

|||||||||||||||

Termination Fault Interrupt Enable |

|||||||||||||||

Termination Fault Latched Status |

|||||||||||||||

Termination Fault Dynamic Status |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Signal Loss Status

There are four registers associated with the Signal Loss Status: Dynamic Status, Latched Status, Interrupt Enable, and Set Edge/Level Interrupt.

Function: |

Status for termination fault. If the input voltage exceeds 5 volts while termination is enabled, the bit associated with that channel will be set to a 1. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt) |

Initialized Value: |

0x00000000 |

Signal Loss Set Edge/Level Interrupt |

|||||||||||||||

Signal Loss Interrupt Enable |

|||||||||||||||

Signal Loss Latched Status |

|||||||||||||||

Signal Loss Dynamic Status |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Summary Status

There are four registers associated with the Summary Status: Dynamic Status, Latched Status, Interrupt Enable, and Set Edge/Level Interrupt.

Function: |

Sets the corresponding bit associated with the channel that has an error condition - BIT, Termination Fault or Signal Loss. |

Type: |

unsigned binary word (32-bits) |

Data Range: |

0x0000 0000 to 0x0000 00FF |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Set Edge/Level Interrupt) |

Initialized Value: |

NA |

Summary Set Edge/Level Interrupt |

|||||||||||||||

Summary Interrupt Enable |

|||||||||||||||

Summary Latched Status |

|||||||||||||||

Summary Dynamic Status |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch8 |

Ch7 |

Ch6 |

Ch5 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Interrupt Vector and Summary

When interrupts are enabled, the interrupt vector associated with the specific interrupt can be programmed (typically with a unique number/identifier) such that it can be utilized in the Interrupt Service Routine (ISR) to identify the type of interrupt. When an interrupt occurs, the contents of the Interrupt Vector register is reported as part of the interrupt mechanism.

In addition to specifying the interrupt vector, the interrupt can be directed (“steered”) to the native bus or to the application running on the onboard ARM processor.

|

Note

|

The Interrupt Vector and Interrupt Steering registers are mapped to the Motherboard Common Memory and these registers are associated with the Module Slot position (refer to Function Register Map). |

Interrupt Vector

Function: |

Set an identifier for the interrupt. Type: unsigned binary word (32-bit) |

Type: |

unsigned binary word (32-bit) |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, this value is reported as part of the interrupt mechanism. |

Interrupt Steering

Function: |

Sets where to direct the interrupt. Type: unsigned binary word (32-bit) |

Type: |

unsigned binary word (32-bit) |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, the interrupt is sent as specified: |

Direct Interrupt to VME |

1 |

Direct Interrupt to ARM Processor (via SerDes) (Custom App on ARM or NAI Ethernet Listener App) |

2 |

Direct Interrupt to PCIe Bus |

5 |

Direct Interrupt to cPCI Bus |

6 |

FUNCTION REGISTER MAP

Key:

Bold Italic |

= Configuration/Control |

Bold Underline |

= Status |

*When an event is detected, the bit associated with the event is set in this register and will remain set until the user clears the event bit. Clearing the bit requires writing a 1 back to the specific bit that was set when read (i.e., write-1-to-clear, writing a “1” to a bit set to “1” will set the bit to “0).

~ Data is always in Floating Point

VR/Counter Measurement Registers

Addr (Hex) |

Name |

Read/Write |

0x2010 |

Measured Period Ch 1 |

R |

0x2110 |

Measured Period Ch 2 |

R |

0x2210 |

Measured Period Ch 3 |

R |

0x2310 |

Measured Period Ch 4 |

R |

0x2410 |

Measured Period Ch 5 |

R |

0x2510 |

Measured Period Ch 6 |

R |

0x2610 |

Measured Period Ch 7 |

R |

0x2710 |

Measured Period Ch 8 |

R |

Addr (Hex) |

Name |

Read/Write |

0x2014 |

Measured Phase Ch 1 |

R |

0x2114 |

Measured Phase Ch 2 |

R |

0x2214 |

Measured Phase Ch 3 |

R |

0x2314 |

Measured Phase Ch 4 |

R |

0x2414 |

Measured Phase Ch 5 |

R |

0x2514 |

Measured Phase Ch 6 |

R |

0x2614 |

Measured Phase Ch 7 |

R |

0x2714 |

Measured Phase Ch 8 |

R |

Addr (Hex) |

Name |

Read/Write |

0x2018 |

Measured Percent Torque Ch 1 |

R |

0x2118 |

Measured Percent Torque Ch 2 |

R |

0x2218 |

Measured Percent Torque Ch 3 |

R |

0x2318 |

Measured Percent Torque Ch 4 |

R |

0x2418 |

Measured Percent Torque Ch 5 |

R |

0x2518 |

Measured Percent Torque Ch 6 |

R |

0x2618 |

Measured Percent Torque Ch 7 |

R |

0x2718 |

Measured Percent Torque Ch 8 |

R |

Addr (Hex) |

Name |

Read/Write |

0x201C |

Measured Amplitude Ch 1 |

R |

0x211C |

Measured Amplitude Ch 2 |

R |

0x221C |

Measured Amplitude Ch 3 |

R |

0x231C |

Measured Amplitude Ch 4 |

R |

0x241C |

Measured Amplitude Ch 5 |

R |

0x251C |

Measured Amplitude Ch 6 |

R |

0x261C |

Measured Amplitude Ch 7 |

R |

0x271C |

Measured Amplitude Ch 8 |

R |

Addr (Hex) |

Name |

Read/Write |

0x2020 |

Measured Frequency Ch 1 |

R |

0x2120 |

Measured Frequency Ch 2 |

R |

0x2220 |

Measured Frequency Ch 3 |

R |

0x2320 |

Measured Frequency Ch 4 |

R |

0x2420 |

Measured Frequency Ch 5 |

R |

0x2520 |

Measured Frequency Ch 6 |

R |

0x2620 |

Measured Frequency Ch 7 |

R |

0x2720 |

Measured Frequency Ch 8 |

R |

Addr (Hex) |

Name |

Read/Write |

0x2028 |

Measured RPM Ch 1 |

R |

0x2128 |

Measured RPM Ch 2 |

R |

0x2228 |

Measured RPM Ch 3 |

R |

0x2328 |

Measured RPM Ch 4 |

R |

0x2428 |

Measured RPM Ch 5 |

R |

0x2528 |

Measured RPM Ch 6 |

R |

0x2628 |

Measured RPM Ch 7 |

R |

0x2728 |

Measured RPM Ch 8 |

R |

Addr (Hex) |

Name |

Read/Write |

0x203C |

Measured Cycle Count Ch 1 |

R |

0x213C |

Measured Cycle Count Ch 2 |

R |

0x223C |

Measured Cycle Count Ch 3 |

R |

0x233C |

Measured Cycle Count Ch 4 |

R |

0x243C |

Measured Cycle Count Ch 5 |

R |

0x253C |

Measured Cycle Count Ch 6 |

R |

0x263C |

Measured Cycle Count Ch 7 |

R |

0x273C |

Measured Cycle Count Ch 8 |

R |

VR/Counter Control Registers

Addr (Hex) |

Name |

Read/Write |

0x0250 |

Power Supply Enable |

R/W |

0x02B0 |

Channel Status Enable |

R/W |

0x1000 |

Channel Enable |

R/W |

0x1004 |

Dipole Enable |

R/W |

0x1008 |

Falling Edge Measurement Enable |

R/W |

0x100C |

Termination Enable |

R/W |

0x1010 |

AC Couple Enable |

R/W |

0x1014 |

Range Select |

R/W |

0x1018 |

Zero Torque Signal Phase to Phase Reading |

R/W |

0x101C |

Reset Cycle Count |

R/W |

0x1020 |

Auto Threshold Enable |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2000 |

Voltage Threshold High Ch 1 |

R/W |

0x2100 |

Voltage Threshold High Ch 2 |

R/W |

0x2200 |

Voltage Threshold High Ch 3 |

R/W |

0x2300 |

Voltage Threshold High Ch 4 |

R/W |

0x2400 |

Voltage Threshold High Ch 5 |

R/W |

0x2500 |

Voltage Threshold High Ch 6 |

R/W |

0x2600 |

Voltage Threshold High Ch 7 |

R/W |

0x2700 |

Voltage Threshold High Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2008 |

Zero Torque Signal Phase Ch 1 |

R/W |

0x2108 |

Zero Torque Signal Phase Ch 2 |

R/W |

0x2208 |

Zero Torque Signal Phase Ch 3 |

R/W |

0x2308 |

Zero Torque Signal Phase Ch 4 |

R/W |

0x2408 |

Zero Torque Signal Phase Ch 5 |

R/W |

0x2508 |

Zero Torque Signal Phase Ch 6 |

R/W |

0x2608 |

Zero Torque Signal Phase Ch 7 |

R/W |

0x2708 |

Zero Torque Signal Phase Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2024 |

Number of Teeth Ch 1 |

R/W |

0x2124 |

Number of Teeth Ch 2 |

R/W |

0x2224 |

Number of Teeth Ch 3 |

R/W |

0x2324 |

Number of Teeth Ch 4 |

R/W |

0x2424 |

Number of Teeth Ch 5 |

R/W |

0x2524 |

Number of Teeth Ch 6 |

R/W |

0x2624 |

Number of Teeth Ch 7 |

R/W |

0x2724 |

Number of Teeth Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2004 |

Voltage Threshold Low Ch 1 |

R/W |

0x2104 |

Voltage Threshold Low Ch 2 |

R/W |

0x2204 |

Voltage Threshold Low Ch 3 |

R/W |

0x2304 |

Voltage Threshold Low Ch 4 |

R/W |

0x2404 |

Voltage Threshold Low Ch 5 |

R/W |

0x2504 |

Voltage Threshold Low Ch 6 |

R/W |

0x2604 |

Voltage Threshold Low Ch 7 |

R/W |

0x2704 |

Voltage Threshold Low Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x200C |

Max Torque Signal Phase Ch 1 |

R/W |

0x210C |

Max Torque Signal Phase Ch 2 |

R/W |

0x220C |

Max Torque Signal Phase Ch 3 |

R/W |

0x230C |

Max Torque Signal Phase Ch 4 |

R/W |

0x240C |

Max Torque Signal Phase Ch 5 |

R/W |

0x250C |

Max Torque Signal Phase Ch 6 |

R/W |

0x260C |

Max Torque Signal Phase Ch 7 |

R/W |

0x270C |

Max Torque Signal Phase Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x202C |

Averaging Time Ch 1 |

R/W |

0x212C |

Averaging Time Ch 2 |

R/W |

0x222C |

Averaging Time Ch 3 |

R/W |

0x232C |

Averaging Time Ch 4 |

R/W |

0x242C |

Averaging Time Ch 5 |

R/W |

0x252C |

Averaging Time Ch 6 |

R/W |

0x262C |

Averaging Time Ch 7 |

R/W |

0x272C |

Averaging Time Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2030 |

Debounce Time Ch 1 |

R/W |

0x2130 |

Debounce Time Ch 2 |

R/W |

0x2230 |

Debounce Time Ch 3 |

R/W |

0x2330 |

Debounce Time Ch 4 |

R/W |

0x2430 |

Debounce Time Ch 5 |

R/W |

0x2530 |

Debounce Time Ch 6 |

R/W |

0x2630 |

Debounce Time Ch 7 |

R/W |

0x2730 |

Debounce Time Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2038 |

Minimum Frequency Ch 1 |

R/W |

0x2138 |

Minimum Frequency Ch 2 |

R/W |

0x2238 |

Minimum Frequency Ch 3 |

R/W |

0x2338 |

Minimum Frequency Ch 4 |

R/W |

0x2438 |

Minimum Frequency Ch 5 |

R/W |

0x2538 |

Minimum Frequency Ch 6 |

R/W |

0x2638 |

Minimum Frequency Ch 7 |

R/W |

0x2738 |

Minimum Frequency Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2044 |

Auto Threshold Hysteresis Ch 1 |

R/W |

0x2144 |

Auto Threshold Hysteresis Ch 2 |

R/W |

0x2244 |

Auto Threshold Hysteresis Ch 3 |

R/W |

0x2344 |

Auto Threshold Hysteresis Ch 4 |

R/W |

0x2444 |

Auto Threshold Hysteresis Ch 5 |

R/W |

0x2544 |

Auto Threshold Hysteresis Ch 6 |

R/W |

0x2644 |

Auto Threshold Hysteresis Ch 7 |

R/W |

0x2744 |

Auto Threshold Hysteresis Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2034 |

Minimum Amplitude Ch 1 |

R/W |

0x2134 |

Minimum Amplitude Ch 2 |

R/W |

0x2234 |

Minimum Amplitude Ch 3 |

R/W |

0x2334 |

Minimum Amplitude Ch 4 |

R/W |

0x2434 |

Minimum Amplitude Ch 5 |

R/W |

0x2534 |

Minimum Amplitude Ch 6 |

R/W |

0x2634 |

Minimum Amplitude Ch 7 |

R/W |

0x2734 |

Minimum Amplitude Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2040 |

Auto Threshold Percent Ch 1 |

R/W |

0x2140 |

Auto Threshold Percent Ch 2 |

R/W |

0x2240 |

Auto Threshold Percent Ch 3 |

R/W |

0x2340 |

Auto Threshold Percent Ch 4 |

R/W |

0x2440 |

Auto Threshold Percent Ch 5 |

R/W |

0x2540 |

Auto Threshold Percent Ch 6 |

R/W |

0x2640 |

Auto Threshold Percent Ch 7 |

R/W |

0x2740 |

Auto Threshold Percent Ch 8 |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x2048 |

Auto Down-Range Time Ch 1 |

R/W |

0x2148 |

Auto Down-Range Time Ch 2 |

R/W |

0x2248 |

Auto Down-Range Time Ch 3 |

R/W |

0x2348 |

Auto Down-Range Time Ch 4 |

R/W |

0x2448 |

Auto Down-Range Time Ch 5 |

R/W |

0x2548 |

Auto Down-Range Time Ch 6 |

R/W |

0x2648 |

Auto Down-Range Time Ch 7 |

R/W |

0x2748 |

Auto Down-Range Time Ch 8 |

R/W |

Unit Conversion Programming Registers

Addr (Hex) |

Name |

Read/Write |

0x0264 |

Floating Point Mode |

R |

0x02B4 |

Floating Point Enable |

R/W |

Module Common Registers

Refer to “Module Common Registers Module Manual” for the Module Common Registers Function Register Map.

Status Registers

BIT Status

Addr (Hex) |

Name |

Read/Write |

0x0800 |

Dynamic Status |

R |

0x0804 |

Latched Status* |

R/W |

0x0808 |

Interrupt Enable |

R/W |

0x080C |

Set Edge/Level Interrupt |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0248 |

Test Enable |

R/W |

Termination Fault Status

Addr (Hex) |

Name |

Read/Write |

0x0810 |

Dynamic Channel Status |

R |

0x0814 |

Latched Channel Status |

R/W |

0x0818 |

Termination Fault Interrupt Enable |

R/W |

0x081C |

Termination Fault Set Edge/Level Interrupt |

R/W |

Signal Loss Status

Addr (Hex) |

Name |

Read/Write |

0x0820 |

Dynamic Channel Status |

R |

0x0824 |

Latched Channel Status |

R/W |

0x0828 |

Signal Loss Interrupt Enable |

R/W |

0x082C |

Signal Loss Set Edge/Level Interrupt |

R/W |

Summary Status

Addr (Hex) |

Name |

Read/Write |

0x09A0 |

Dynamic Summary Status |

R |

0x09A4 |

Latched Summary Status |

R/W |

0x09A8 |

Summary Interrupt Enable |

R/W |

0x09AC |

Summary Set Edge/Level Interrupt |

R/W |

Interrupt Registers

The Interrupt Vector and Interrupt Steering registers are mapped to the Motherboard Memory Space and these addresses are absolute based on the module slot position. Do not apply the Module Address offset to these addresses.

Addr (Hex) |

Name |

Read/Write |

0x0500 |

Module 1 Interrupt Vector 1 - BIT |

R/W |

0x0504 |

Module 1 Interrupt Vector 2 - Termination Fault Status |

R/W |

0x0508 |

Module 1 Interrupt Vector 3 - Signal Loss Status |

R/W |

0x050C to 0x0564 |

Module 1 Interrupt Vector 4-26 - Reserved |

R/W |

0x0568 |

Module 1 Interrupt Vector 27 - Summary |

R/W |

0x056C to 0x057C |

Module 1 Interrupt Vector 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0600 |

Module 1 Interrupt Steering 1 - BIT |

R/W |

0x0604 |

Module 1 Interrupt Steering 2 - Termination Fault Status |

R/W |

0x0608 |

Module 1 Interrupt Steering 3 - Signal Loss Status |

R/W |

0x060C to 0x0664 |

Module 1 Interrupt Steering 4-26 - Reserved |

R/W |

0x0668 |

Module 1 Interrupt Steering 27 - Summary |

R/W |

0x066C to 0x067C |

Module 1 Interrupt Steering 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0700 |

Module 2 Interrupt Vector 1 - BIT |

R/W |

0x0704 |

Module 2 Interrupt Vector 2 - Termination Fault Status |

R/W |

0x0708 |

Module 2 Interrupt Vector 3 - Signal Loss Status |

R/W |

0x070C to 0x0764 |

Module 2 Interrupt Vector 4-26 - Reserved |

R/W |

0x0768 |

Module 2 Interrupt Vector 27 - Summary |

R/W |

0x076C to 0x077C |

Module 2 Interrupt Vector 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0800 |

Module 2 Interrupt Steering 1 - BIT |

R/W |

0x0804 |

Module 2 Interrupt Steering 2 - Termination Fault Status |

R/W |

0x0808 |

Module 2 Interrupt Steering 3 - Signal Loss Status |

R/W |

0x080C to 0x0864 |

Module 2 Interrupt Steering 4-26 - Reserved |

R/W |

0x0868 |

Module 2 Interrupt Steering 27 - Summary |

R/W |

0x086C to 0x087C |

Module 2 Interrupt Steering 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0900 |

Module 3 Interrupt Vector 1 - BIT |

R/W |

0x0904 |

Module 3 Interrupt Vector 2 - Termination Fault Status |

R/W |

0x0908 |

Module 3 Interrupt Vector 3 - Signal Loss Status |

R/W |

0x090C to 0x0964 |

Module 3 Interrupt Vector 4-26 - Reserved |

R/W |

0x0968 |

Module 3 Interrupt Vector 27 - Summary |

R/W |

0x096C to 0x097C |

Module 3 Interrupt Vector 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0A00 |

Module 3 Interrupt Steering 1 - BIT |

R/W |

0x0A04 |

Module 3 Interrupt Steering 2 - Termination Fault Status |

R/W |

0x0A08 |

Module 3 Interrupt Steering 3 - Signal Loss Status |

R/W |

0x0A0C to 0x0A64 |

Module 3 Interrupt Steering 4-26 - Reserved |

R/W |

0x0A68 |

Module 3 Interrupt Steering 27 - Summary |

R/W |

0x0A6C to 0x0A7C |

Module 3 Interrupt Steering 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0B00 |

Module 4 Interrupt Vector 1 - BIT |

R/W |

0x0B04 |

Module 4 Interrupt Vector 2 - Termination Fault Status |

R/W |

0x0B08 |

Module 4 Interrupt Vector 3 - Signal Loss Status |

R/W |

0x0B0C to 0x0B64 |

Module 4 Interrupt Vector 4-26 - Reserved |

R/W |

0x0B68 |

Module 4 Interrupt Vector 27 - Summary |

R/W |

0x0B6C to 0x0B7C |

Module 4 Interrupt Vector 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0C00 |

Module 4 Interrupt Steering 1 - BIT |

R/W |

0x0C04 |

Module 4 Interrupt Steering 2 - Termination Fault Status |

R/W |

0x0C08 |

Module 4 Interrupt Steering 3 - Signal Loss Status |

R/W |

0x0C0C to 0x0C64 |

Module 4 Interrupt Steering 4-26 - Reserved |

R/W |

0x0C68 |

Module 4 Interrupt Steering 27 - Summary |

R/W |

0x0C6C to 0x0C7C |

Module 4 Interrupt Steering 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0D00 |

Module 5 Interrupt Vector 1 - BIT |

R/W |

0x0D04 |

Module 5 Interrupt Vector 2 - Termination Fault Status |

R/W |

0x0D08 |

Module 5 Interrupt Vector 3 - Signal Loss Status |

R/W |

0x0D0C to 0x0D64 |

Module 5 Interrupt Vector 4-26 - Reserved |

R/W |

0x0D68 |

Module 5 Interrupt Vector 27 - Summary |

R/W |

0x0D6C to 0x0D7C |

Module 5 Interrupt Vector 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0E00 |

Module 5 Interrupt Steering 1 - BIT |

R/W |

0x0E04 |

Module 5 Interrupt Steering 2 - Termination Fault Status |

R/W |

0x0E08 |

Module 5 Interrupt Steering 3 - Signal Loss Status |

R/W |

0x0E0C to 0x0E64 |

Module 5 Interrupt Steering 4-26 - Reserved |

R/W |

0x0E68 |

Module 5 Interrupt Steering 27 - Summary |

R/W |

0x0E6C to 0x0E7C |

Module 5 Interrupt Steering 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x0F00 |

Module 6 Interrupt Vector 1 - BIT |

R/W |

0x0F04 |

Module 6 Interrupt Vector 2 - Termination Fault Status |

R/W |

0x0F08 |

Module 6 Interrupt Vector 3 - Signal Loss Status |

R/W |

0x0F0C to 0x0F64 |

Module 6 Interrupt Vector 4-26 - Reserved |

R/W |

0x0F68 |

Module 6 Interrupt Vector 27 - Summary |

R/W |

0x0F6C to 0x0F7C |

Module 6 Interrupt Vector 28 - 32 - Reserved |

R/W |

Addr (Hex) |

Name |

Read/Write |

0x1000 |

Module 6 Interrupt Steering 1 - BIT |

R/W |

0x1004 |

Module 6 Interrupt Steering 2 - Termination Fault Status |

R/W |

0x1008 |

Module 6 Interrupt Steering 3 - Signal Loss Status |

R/W |

0x100C to 0x1064 |

Module 6 Interrupt Steering 4-26 - Reserved |

R/W |

0x1068 |

Module 6 Interrupt Steering 27 - Summary |

R/W |

0x106C to 0x107C |

Module 6 Interrupt Steering 28 - 32 - Reserved |

R/W |

APPENDIX A: REGISTER NAME CHANGES FROM PREVIOUS RELEASES

This section provides a mapping of the register names used in this document against register names used in previous releases.

Rev C - Register Names |

Rev A1 - Register Names |

VR/Counter Measurement Registers |

|

Measured Period |

Period Measurement |

Measured Phase |

Phase Measurement |

Measured Percent Torque |

Percent Torque Measurement |

Measured Amplitude |

Amplitude Voltage Reading |

Measured Frequency |

Frequency Reading |

Measured RPM |

Velocity Measurement |

Measured Cycle Count |

Cycle Count |

VR/Counter Control Registers |

|

Power Supply Enable |

Power Supply Enable |

Channel Enable |

Channel Enable |

Dipole Enable |

Dipole Enable |

Falling Edge Measurement Enable |

Polarity Select |

Termination Enable |

Termination Enable |

AC Couple Enable |

AC Couple Enable |

Range Select |

Range Select |

Auto Down-Range Time |

|

Number of Teeth |

Reluctor Ring Teeth |

Zero Torque Signal Phase |

Zero Torque Signal Phase |

Zero Torque Signal Phase to Phase Reading |

Set Zero Torque Signal Phase |

Max Torque Signal Phase |

Max Torque Signal Phase |

Averaging Time |

Averaging Time |

Debounce Time |

Debounce Time |

Voltage Threshold High |

Voltage Threshold High |

Voltage Threshold Low |

Voltage Threshold Low |

Minimum Amplitude |

Minimum Signal Amplitude |

Minimum Frequency |

Minimum Signal Frequency |

Reset Cycle Count |

Reset Cycle Count |

Auto Threshold Percent |

Auto Threshold Percent |

Auto Threshold Hysteresis |

Auto Threshold Hysteresis |

Auto Threshold Enable |

Auto Threshold Enable |

Engineering Scaling Conversion Registers |

|

Enable Floating Point Mode |

Enable Floating Point Mode |

Floating Point State |

Floating Point State |

Test Registers |

|

Test Enable |

Test Enable |

Status and Interrupt Registers |

|

Channel Status Enabled |

Channel Status Enabled |

BIT Dynamic Status |

BIT Dynamic Status |

BIT Latched Status |

BIT Latched Status |

BIT Interrupt Enable |

BIT Interrupt Enable |

BIT Set Edge/Level Interrupt |

BIT Set Edge/Level Interrupt |

Termination Fault Dynamic Status |

Termination Fault Dynamic Status |

Termination Fault Latched Status |

Termination Fault Latched Status |

Termination Fault Interrupt Enable |

Termination Fault Interrupt Enable |

Termination Fault Set Edge/Level Interrupt |

Termination Fault Set Edge/Level Interrupt |

Signal Loss Dynamic Status |

Signal Loss Dynamic Status |

Signal Loss Latched Status |

Signal Loss Latched Status |

Signal Loss Interrupt Enable |

Signal Loss Interrupt Enable |

Signal Loss Set Edge/Level Interrupt |

Signal Loss Set Edge/Level Interrupt |

Summary Dynamic Status |

Summary Dynamic Status |

Summary Latched Status |

Summary Latched Status |

Summary Interrupt Enable |

Summary Interrupt Enable |

Summary Set Edge/Level Interrupt |

Summary Set Edge/Level Interrupt |

Interrupt Vector |

Interrupt Vector |

Interrupt Steering |

Interrupt Steering |

APPENDIX B: INTEGER/FLOATING POINT MODE PROGRAMMING

Integer/Floating Point Mode Supported Registers

-

Measured Period

-

Measured Phase

-

Measured Percent Torque

-

Measured Amplitude

-

Measured Frequency

-

Measured RPM

-

Measured Cycle Count

-

Voltage Threshold High

-

Voltage Threshold Low Zero

-

Torque Signal Phase

-

Max Torque Signal Phase

-

Number of Teeth

-

Averaging Time

-

Debounce Time

-

Minimum Amplitude

-

Minimum Frequency

-

Auto Threshold Percent

-

Auto Threshold Hysteresis

Integer/Floating Mode Example (Measured Period)

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

Enable Floating Point Mode: 0 (Integer Mode) 0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 1 nanosecond. Floating Point Mode: Read as a Single Precision Floating Point Value (IEEE-754) where the units are in seconds. |

Example: 1ms period

Integer mode 0x000F4240

Floating point mode 0x3a83126f

Integer/Floating Mode Example (Measured Phase)

Type: |

unsigned binary word (32-bit) (Integer Mode) or Single Precision Floating Point Value (IEEE-754) (Floating Point Mode) |

Data Range: |

Enable Floating Point Mode: 0 (Integer Mode) 0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

N/A |

Operational Settings: |

Integer Mode: LSB is 0.001°. Floating Point Mode: Read as a Single Precision Floating Point Value (IEEE-754) where the units are in degrees. |

Example 120.5° phase

Integer mode: 0x0001D6b4

Floating point mode: 0x42f10000

APPENDIX D: GETTING STARTED

The power-on initialized values of the Variable Reluctance/Counter module will enable the module to obtain several measurements.

To obtain accurate RPM/Velocity measurements you will need to set the number of teeth by writing to the Reluctor Ring Teeth Number register of the channel. Definition:

Monopole sensor type = single sensor pulse train

Dipole sensor type = dual sensor pulse train (can be a single channel interlaced input or dual paired channels).

A distinction is that dipole typically refers to any measurements involving phase, whether in the single channel or dual paired channels modes.

The power on default for the sensor type is Monopole. For measurements with a Dipole sensor configuration, set the applicable bits in the Dipole Enable register.

The initialized values for the Power Supply Enable register (i.e. module power) and the Channel Enable register (to enable each individual channel) are such that the module is powered on and all eight channels are enabled.

The Register chapter of the manual is intended to provide a concise description of each register. At times, some additional information or definition is needed to assist the user in understand the benefits of each register.

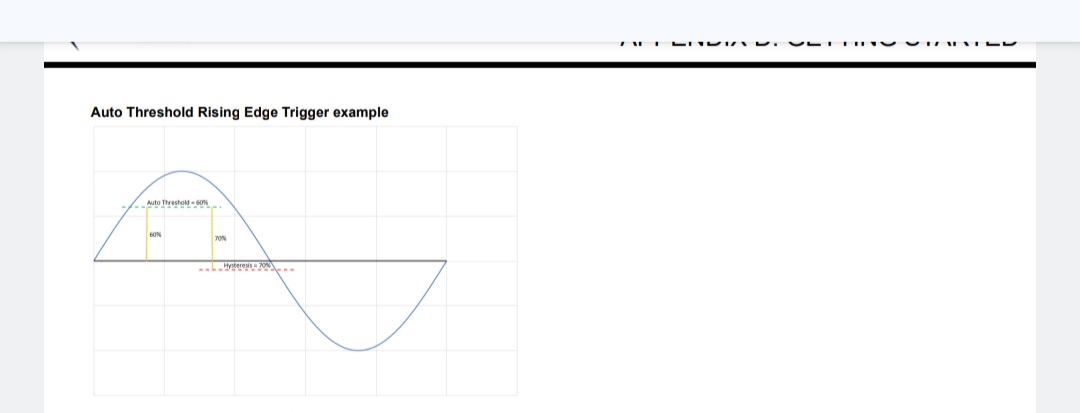

Auto Threshold Enable

Peak detected value from prior cycle is dynamically used to set the thresholds based on the configuration settings for threshold percent and hysteresis. Peak detection is from either a positive or negative peak.

For channels with Auto Threshold enabled, the upper and lower thresholds will be automatically adjusted based on the channel amplitude measurement, auto threshold percentage setting, and the auto threshold hysteresis setting. Adjustment is done at 1 second intervals.

For rising edge polarity settings:

The upper level will be set to a value of

[ channel amplitude reading X Auto Threshold percentage setting ].

The lower threshold level will be set to a level of

[ upper threshold - ( channel amplitude x Auto Threshold hysteresis % ) ]

For falling edge polarity settings:

The Lower threshold level will be set to a value of

[ -channel amplitude reading X Auto Threshold percentage setting ].

The upper threshold level will be set to a level of

[ lower threshold + ( channel amplitude x Auto Threshold hysteresis % ) ]

|

Note

|

channel amplitude measurement is always returned positive, as an absolute number, and represents the peak excursion from 0V, whether negative or positive. Signals are expected to be symmetrical about zero when using this mode. If there is a significant DC offset, then AC coupling or manual threshold settings may be preferable. |

Auto Threshold Percent

Sets the percent of peak amplitude to set the active edge threshold in automatic mode. When configured for auto threshold, the trigger threshold is automatically adjusted to the specified percentage of the peak amplitude reading to compensate for varying signal amplitudes, at one second intervals.

Auto Threshold Hysteresis

Sets the percent of hysteresis to set the opposite edge threshold in automatic mode.

Auto Threshold Rising Edge Trigger example

Auto Threshold Falling Edge Trigger example

Termination Enable