FTA-FTF Manual

Edit this on GitLab

INTRODUCTION

As a leading manufacturer of smart function modules, NAI offers over 100 different modules that cover a wide range of I/O, measurement and simulation, communications, Ethernet switch, and SBC functions. Our MIL-STD-1553 communication smart function modules provide programmable 1-, 2-, or 4-channel, dual-redundant, transformer-coupled (FTA, FTB, FTC) or direct-coupled (FTD, FTE, FTF) interfaces, possessing an improved assisted mode. MIL-STD-1553 is a military standard published by the United States Department of Defense that defines the mechanical, electrical, and functional characteristics of a serial data bus. It features a dual-redundant, balanced-line, physical layer; a (differential) network interface; time division multiplexing; half-duplex command/response protocol; and up to 31 remote terminals (devices). This user manual is designed to help you get the most out of our MIL-STD-1553 smart function modules.

For a brief description of the module and complete list of specifications, click here for the FTA-FTF data sheet.

FTA-FTF Overview

NAI’s FTA-FTF modules offers a range of features designed to suit a variety of system requirements, including:

Independent Dual-Redundant Channels: The FTA-FTF modules provide up to four dual-redundant MIL-STD-1553 interface channels. Each channel can be configured to act as a Bus Controller (BC), Remote Terminal (RT), Bus Monitor (BM), or RT/BM combined mode. This flexibility allows for versatile operation and redundancy in critical systems.

Assisted Mode (AM): The FTA-FTF modules utilize a built-in secondary (ARM) processor dedicated to 'assisting' the movement of 1553 messages from the 1553 device to host interface, minimizing host CPU activity (reads & writes to device), reducing application memory required on the host, and improving data transfer time between 1553 device and host interface while also reducing data transfer delays.

Ample On-Board Memory: With a substantial 16K words of on-board memory per channel, this module offers ample storage capacity for data and messages, facilitating efficient data handling and processing.

IP-Core Register Compatibility: Users familiar with the DDC™ family of devices will appreciate that the module’s IP-core registers are compatible with these devices. This compatibility ensures seamless integration into existing systems and reduces the learning curve for engineers already familiar with DDC™ products.

Message Retry Policy: The FTA-FTF modules provide the ability to configure and set a message retry policy, proving invaluable in ensuring data integrity and system reliability, particularly in environments where communication errors may occur.

Message Scheduling Capability: This feature allows precise timing and coordination of messages, making it ideal for applications that require synchronized data exchange.

Asynchronous Message Capability: The FTA-FTF modules supports asynchronous messaging, which is crucial for real-time systems where data needs to be transmitted and received without fixed time intervals. This feature ensures efficient communication in dynamic environments.

Message FIFO Capability: The inclusion of a message FIFO (First-In-First-Out) capability enhances data management and flow control. Users can optimize data handling and prioritize messages as needed, contributing to system efficiency.

PRINCIPLE OF OPERATION

MIL-STD-1553 is a military standard that defines the characteristic for a Digital Time Division Command/Response Multiplexed Data Bus. The 1553 data bus is a dual-redundant, bi-directional, Manchester II encoded data bus with a high bit error reliability. It is used commonly for both military and civilian applications in avionics, aircraft and spacecraft data handling.

Table 1 provides a summary of the MIL-STD-1553 characteristics.

Terminal Types |

Bus Controller Remote Terminal Bus Monitor |

Number of Remote Terminals |

Maximum of 31 |

Transmission Technique |

Half-duplex |

Operation |

Asynchronous |

Encoding |

Manchester II bi-phase level |

Fault Tolerance |

Typically, Dual-Redundant Bus, which means there are two independent bus networks (one bus is called the Primary or “A” bus and the other is the Secondary or “B” bus. 1553 messages are usually only transmitted on either the A or B bus network at a time, but it does not usually matter which bus is used for the message transfer - devices on the 1553 network are supposed to handle messages on either the A or B bus with equal priority. |

Coupling |

Transformer or direct |

Data Rate |

1 MHz |

Word Length |

20 bits |

Data Bits/Word |

16 bits |

Message Length |

Maximum of 32 Data Words |

Protocol |

Command/response |

Message Formats |

Bus Controller to Remote Terminal (BC-RT message) |

The MIL-STD-1553 Data Bus is defined as a twisted shielded pair transmission line consisting of the main bus and a number of stubs. There is one stub for each remote terminal connected to the bus. The main bus is terminated at each end with a resistance equal to the cable’s characteristic impedance (± 2%). This termination makes the data bus behave electrically like an infinite transmission line. Stubs, which are added to the main bus to connect the terminals, provide “local” loads and produce impedance mismatch where added. This mismatch, if not properly controlled, produces electrical reflections and degrades the performance of the main bus. Table 2 provides a summary of the MIL-STD-1553 Transmission Media characteristics.

Cable Type |

Twisted Shielded Pair |

Capacitance |

30.0 pF/ft max, wire to wire |

Characteristic Impedance |

70.0 to 85.0 ohms at 1 MHz |

Cable Attenuation |

1.5 dB/100 ft. max, at 1 MHz |

Cable Twists |

4 Twists per ft., minimum |

Shield Coverage |

90% minimum |

Cable Termination |

Cable impedance (± 2%) |

Direct Coupled Stub Length |

Maximum of 1 foot |

XFMR Coupled Stub Length |

Maximum of 20 feet |

Each 1553 channel on the FTA-FTF modules employs a Sital Technology BRM1553D core, which is based on Sital’s proven 1553 IP cores, with DDC® Enhanced Mini-Ace® compatible interface. The core may operate in Bus Controller (BC), Remote Terminal (RT), Bus Monitor (BM) or RT/BM combined mode.

Bus Controller

The Bus Controller (BC) provides data flow control for all transmissions on the bus. In addition to initiating all data transfers, the BC must transmit, receive and coordinate the transfer of information on the data bus. All information is communicated in command/response mode - the BC sends a command to the RTs, which reply with a response, unless the message is BC→broadcast receive message, in which case, there will be no RT response.

Remote Terminal

The Remote Terminal (RT) is a device designed to interface various subsystems with the 1553 data bus. The RT receives and decodes commands from the BC, detects any errors and reacts to those errors. The RT must be able to properly handle both protocol errors (missing data, extra words, etc.) and electrical errors (waveform distortion, rise time violations, etc.). RT characteristics include:

-

Up to 31 Remote Terminals can be connected to the data bus

-

Each Remote Terminal can have 31 Sub addresses, where SA 0 and SA 31 signify a Mode code message. In which case the data word count would be the Mode Code number.

-

No Remote Terminal shall speak unless spoken to first by the Bus Controller and specifically commanded to transmit.

Bus Monitor

The Bus Monitor (BM) listens to all messages on the data bus and records selected activities. The BM is a passive device that collects data for real-time or post capture analysis. The BM can store all or portions of traffic on the bus, including electrical and protocol errors. BMs are primarily used for instrumentation and data bus testing.

MIL-STD-1553

MIL-STD-1553 data bus system consists of a Bus Controller (BC) controlling multiple Remote Terminals (RT) all connected by a data bus providing a single data path between the Bus Controller and all the associated Remote Terminals. There may also be one or more Bus Monitors (BM); however, Bus Monitors are specifically not allowed to take part in data transfers and are only used to capture or record data for analysis.

Message Formats

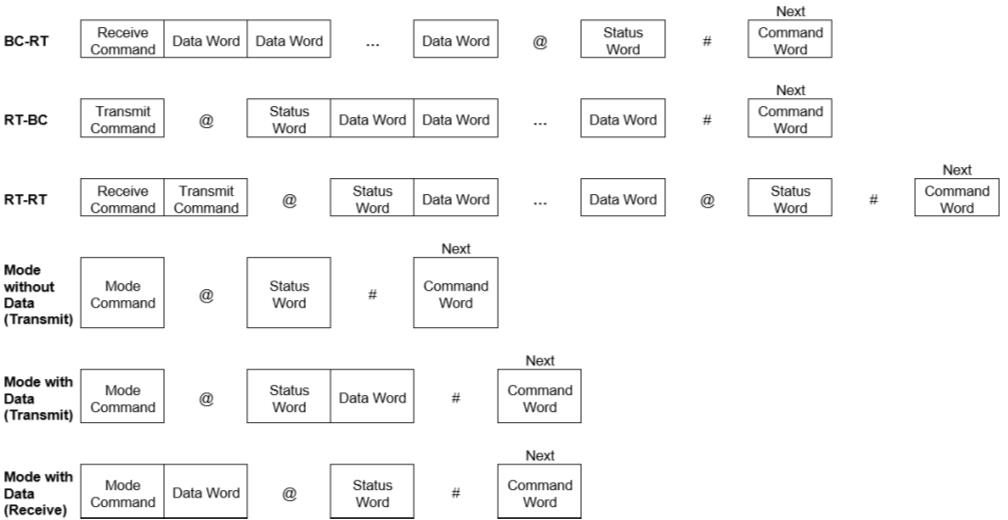

The following transactions are allowed between the BC and a specific RT:

-

BC to RT Transfer - The Bus Controller sends one 16-bit receive command word, immediately followed by 1 to 32 16-bit data words. The selected Remote Terminal then sends a single 16-bit Status word

-

RT to BC Transfer - The Bus Controller sends one transmit command word to a Remote Terminal. The Remote Terminal then sends a single Status word, immediately followed by 1 to 32 data words.

-

Mode Command Without Data Word (Transmit) - The Bus Controller sends one command word with a Sub-address of 0 or 31 signifying a Mode Code type command. The Remote Terminal responds with a Status word

-

Mode Command with Data Word (Transmit) - The Bus Controller sends one command word with a Sub-address of 0 or 31 signifying a Mode Code type command. The Remote Terminal responds with a Status word immediately followed by a single Data word

-

Mode Command with Data Word (Receive) - The Bus Controller sends one command word with a Sub-address of 0 or 31 signifying a Mode Code type command immediately followed by a single data word. The Remote Terminal responds with a Status word

The following transaction is allowed between the BC and a pair of RTs:

-

RT to RT Transfers - The Bus Controller sends out one receive command word immediately followed by one transmit command word. The transmitting Remote Terminal sends a Status word to the BC, immediately followed by 1 to 32 data words to the receiving RT. The receiving Terminal then sends its Status word to the BC.

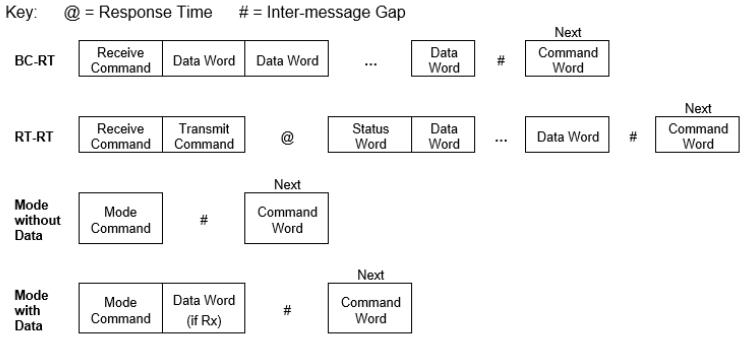

The following are broadcast transactions that are allowed between the BC and all capable RTs:

-

BC to RT(s) Transfers - The Bus Controller sends one receive command word with a Terminal address of 31 signifying a broadcast type command, immediately followed by 0 to 32 data words. All Remote Terminals will accept the data but will not respond back to the BC.

-

RT to RT(s) Transfers - The Bus Controller sends out one receive command word with a Terminal address of 31 signifying a broadcast type command, immediately followed by one transmit command. The transmitting Remote Terminal sends a Status word immediately followed by 1 to 32 data words to all other RT(s). All Remote Terminals will accept the data but will not respond back to the BC.

-

Mode Code without Data Word (Broadcast) - The Bus Controller sends one command word with a Terminal address of 31 signifying a broadcast type command and a sub-address of 0 or 31 signifying a Mode Code type command. No Remote Terminals will respond back to the BC.

-

Mode Code with Data Word (Broadcast) - The Bus Controller sends one command word with a Terminal address of 31 signifying a broadcast type command and a sub-address of 0 or 31 signifying a Mode Code type command, immediately followed by one Data word, if it is an Rx Mode code. No Remote Terminals will respond.

MIL-STD-1553 Message Information Transfer Formats

Key: @ = Response Time; # = Inter-message Gap

MIL-STD-1553 Broadcast Message Information Transfer Formats

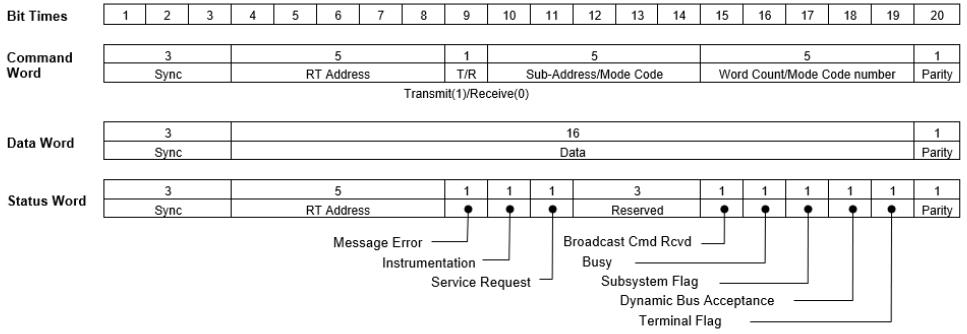

Message Components

The following are three components that make up the 1553 messages:

-

Command Word

-

Data Word

-

Status Word

Each word type is 20 bits in length. The first 3 bits are used as a synchronization field, thereby allowing the decode clock to re-sync at the beginning of each new word. The next 16 bits are the information field. The last bit is the parity bit. Parity is based on odd parity for the single word.

Command Word

The Command Word specifies the function that the Remote Terminal is to perform.

The RT Address field states which unique remote terminal the command is intended for (no two terminals may have the same address). Note the address of 0x00 (00000b) is a valid address, and the address 0x1F (11111b) is always reserved as a broadcast address. The maximum number of terminals the data bus can support is 31.

The Transmit/Receive bit defines the direction of information flow and is always from the point of view of the Remote Terminal. A transmit command (logic 1) indicates that the Remote Terminal is to transmit data, while a receive command (logic 0) indicates that the Remote Terminal is going to receive data

The Sub-Address/Mode Code and Word Count/Mode Code fields are defined as follows:

Sub-Address/Mode Command Field |

Word Count/Mode Code Field |

0x00 (00000b) or 0x1F (11111b) indicates Mode Code Command |

Mode Code number to be performed |

0x01 (00001b) to 0x1E (11110b) indicates the Sub-Address 1 to Sub-Address 30 |

Word Count - note 0x00 (00000b) is decoded as 32 data words |

Data Word

The Data Word contains the actual information that is being transferred within a message. Data Words can be transmitted by either a Remote Terminal (Transmit command) or a Bus Controller (Receive command).

Status Word

When the Remote Terminal receives a message, it will respond with a Status Word. The Status Word is used to convey to the Bus Controller whether a message was properly received or to convey the state of the Remote Terminal (i.e., service request, busy, etc.).

The RT Address in the Status Word should match the RT Address within the Command Word that the Remote Terminal received. With a RT-RT Transfer message, the RT address within either Status Word received (Rx or Tx), should match the RT address within the corresponding Command word sent (Rx or Tx).

Status Bit |

Description |

Message Error (Bit 9) |

This bit is set by the Remote Terminal upon detection of an error in the message or upon detection of an invalid message (i.e. Illegal Command). The error may occur in any of the Data Words within the message. When the terminal detects an error and sets this bit, none of the data received within the message is used. |

Instrumentation (Bit 10) |

This bit is always set to logic 0. |

Service Request (Bit 11) |

This bit is set to a logic 1 by the subsystem if servicing is needed. This bit is typically used when the Bus Controller is “polling” terminals to determine if they require processing. |

Broadcast Command Received (Bit 15) |

This bit indicates that the Remote Terminal received a valid broadcast command. On receiving a valid broadcast command, the Remote Terminal sets this bit to logic 1 and suppresses the transmission of its Status Word. The Bus Controller may issue a Transmit Status Word or Transmit Last Command Word Mode Code to determine if the Remote Terminal received the message properly. |

Busy (Bit 16) |

This bit indicates to the Bus Controller that the Remote Terminal is unable to move data between the Remote Terminal and the Sub-system in compliance to a command from the Bus Controller. In the earlier days of 1553, the Busy bit was required because many subsystem interfaces (analog, synchros, etc.) were much slower compared to the speed of the multiplex data bus. So instead of losing data, a terminal was able to set the Busy bit indicating to the Bus Controller to try again later. As new systems have been developed, the need for the busy bit has been reduced. |

Subsystem Flag (Bit 17) |

This bit provides “health” data regarding the subsystems to which the Remote Terminal is connected. Multiple subsystems may logically “OR” their bits together to form a composite health indicator. |

Dynamic Bus Control Acceptance Bit (Bit 19) |

This bit informs the Bus Controller that the Remote Terminal has received the Dynamic Bus Control Mode Code and has accepted control of the bus. The Remote Terminal, on transmitting its status word, becomes the Bus Controller. The Bus Controller, on receiving the status word from the Remote Terminal with this bit set, ceases to function as the Bus Controller and may become a Remote Terminal or Bus Monitor. |

Terminal Flag (Bit 20) |

This bit informs the Bus Controller of a fault or failure within the Remote Terminal. A logic 1 indicates a fault condition. |

MIL-STD-1553 Word Formats

External RT Address and Auto Start-up Modes

External discrete signals are available to support “hardwired” RT Address and configuration as well as start-up modes for MIL-STD-1760A.

External RT Address

The 1553 modules are completely software RT Address programmable and configurable. Notice 2 of the MIL-STD-1553 standard requires that the Remote Terminal address be wire-programmable from an external I/O connector, and the Remote Terminal perform an odd parity test upon on the wired terminal address. An open circuit on an address line is detected as a logic 1 and connecting the address line to ground is detected as a logic 0. The 1553 modules provided the ability to externally set the RT Address and Parity via discrete signals (CHx-RT-ADDR (0-4) and CHx- PARITY). These discrete signals are considered additional and optional based on specific application requirements. The discrete signals are single-ended and System-GND referenced.

Because of the platform (module-thru-board) available physical pin limitations, only one set of discrete signals are provided for a channel (CH) pair (channel pair 1 = CH1, CH2 and channel pair 2 = CH3, CH4). The discrete pins are provided for the odd-numbered channel, which will use these signals directly. The even channel of the channel pair will use these same pins, but the RT addressing for the even channel will be set as a “hard +1” offset from the odd-channel discrete pattern.

For example:

If the CH1 external pins are either grounded or left open to yield:

CH1-RT-ADDR0-4 pins + Parity pin = (MSB) 01101 (LSB) + 0 (defined as Odd Parity) =0xD (13d)

and the hard offset for CH2 is “1” (0x1)

then, the CH1 RT address is 0xD (13d) (wired) and the CH2 RT address will be 0xE (14d) (wired plus the hard offset).

DISCRETE SIGNAL PIN |

DESCRIPTION (Grounding a pin = “0”, leaving a pin open = “1”. Unit signal pins are defaulted “open = 1”) |

CHx-RT-ADDR0 thru CHx-RT-ADDR4 |

Five (5) External RT address signal pins, binary bit-weighted (ADDR0=LSB); for applying a “hardwire” RT address (special applications only). MSB - (…ADDR4, …ADDR3, …ADDR2, …ADDR1, …ADDR0) - LSB |

CHx-PARITY |

Used in conjunction with external RT address signal pins. A single bit that complements the parity of CHx-RT-ADDR wire to odd parity. If the wrong parity is detected by core, only Broadcast commands would be valid for the core. If not masked, an interrupt will be generated in the event of wrong parity. |

Start-Up Modes

In addition to supporting external RT Addressing, the 1553 modules provide discrete signals (CHx-STANDARD and CHx-MODE0) to support MIL- STD-1760 auto start-up modes.

DISCRETE SIGNAL PIN |

DESCRIPTION (Grounding a pin = “0”, leaving a pin open = “1”. Unit signal pins are defaulted “open = 1”) |

CHx-STANDARD |

'1' - Support for MIL-STD-1760. Will power up as RT with Busy bit set. '0' - Powers up as inactive BC or Idle. |

CHx-MODE0 |

'1' - Disables the BC mode even if software enables BC. '0' - BC mode controlled by software. |

Assisted Mode

The FTA module has been improved to include the “Assisted Mode (AM)” feature.

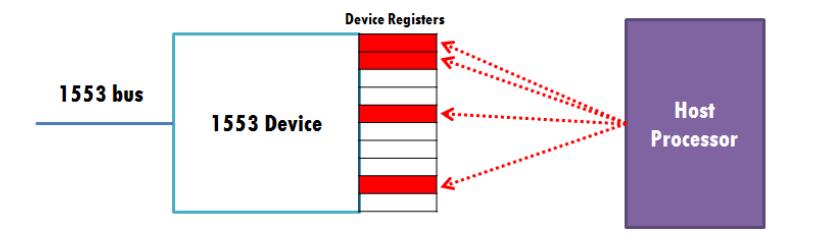

In the legacy FT1-FT6 modules, the 1553 messages are fetched from the 1553 device by accessing device registers directly from the host application as shown in Figure 1. The dotted lines indicate read/write access over the bus interface. The bus interface in some cases may be relatively “slow” (ex. Ethernet interface). In this design, four bus accesses are required from the host to fetch one new 1553 message. The number of accesses increases proportionately with the number of 1553 messages to fetch from the 1553 device.

Figure 1. Legacy FT1-FT6 Message Fetch Processing

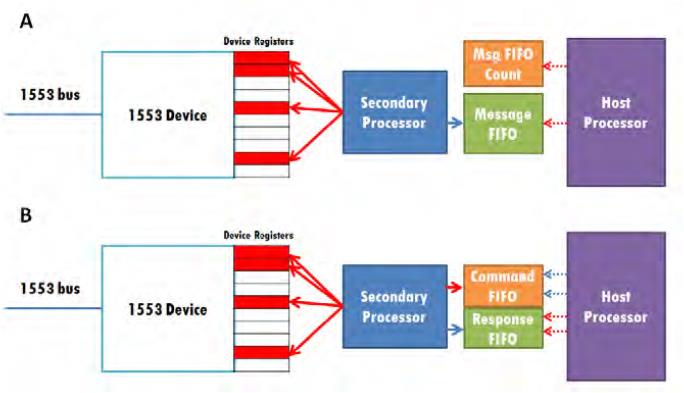

The FTA 1553 module utilizes the secondary (ARM) processor built into the module that is dedicated for the purpose of “assisting” the movement of 1553 messages from the 1553 device to the host interface. This is made possible through a system of FIFOs that carry command and response messages to and from the host CPU to a bare metal application running on the secondary processor (refer to Diagram B in Figure 2). In addition, these modules have the option of funneling all 1553 messages (per channel) to a 4k byte Message FIFO (refer to Diagram A in Figure 2) that is accessible from the host.

Figure 2. AM FIFO and Bus Access

In Figure 2, the dotted lines indicate slower bus read/write accesses (PCI, Ethernet) whereas the solid lines indicate fast bus accesses. When the Message FIFO is utilized (Diagram A), the Message FIFO is filled as new 1553 messages arrive. Moving the 1553 messages from the Message FIFO to the Host Processor requires 2 “slower” bus accesses to fetch all the new 1553 messages that are in the Message FIFO.

If the Message FIFO is not utilized (Diagram B only), for example to fully support DDC API compatibility, 2 writes and at least 2 reads via the “slower” bus is required to fetch one new 1553 message. The write access to the Command FIFO initiates the transfer of 1553 messages from the device to the Response FIFO and when the transfer is complete, the host can read the Response FIFO. In DDC API compatibility mode, the benefits of the “assisted” design provide significantly improved response times compared to the legacy FT module(s), especially with bulk 1553 transfers.

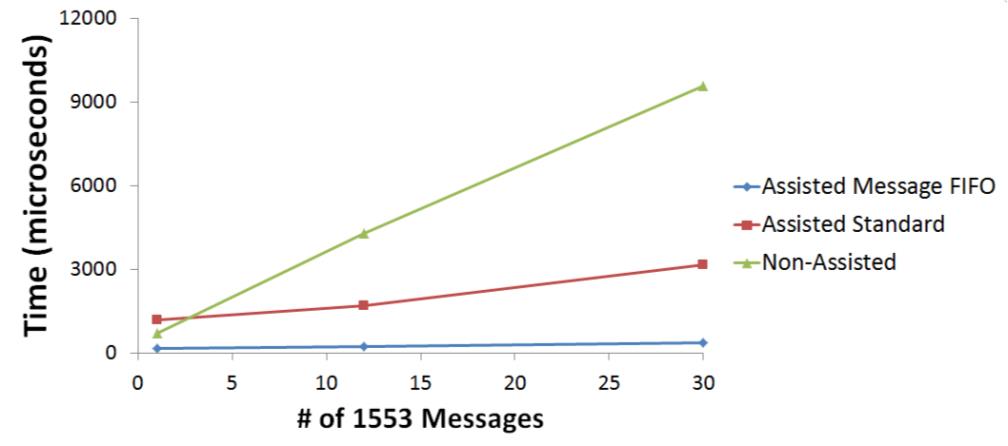

Figure 3 and Table 3 depict the latent time (time required for 1553 message(s) transfer from 1553 device to host memory when initiated by the host CPU) as a function of the number of 1553 messages being transferred. The three candidates for comparison are (1) Assisted Module running in Message FIFO Mode, (2) Assisted Module running in Standard Mode and (3) the Non-Assisted (Legacy) FT Module.

Figure 3. AM Transfer Comparisons

1553 Msgs |

Assisted Message FIFO |

Assisted Standard |

Non-Assisted |

|||

Average |

Worst-Case |

Average |

Worst-Case |

Average |

Worst-Case |

|

1 |

163.630 |

182.445 |

1169.992 |

1193.958 |

695.578 |

705.235 |

12 |

239.0805 |

261.298 |

1698.532 |

1735.622 |

4286.303 |

5574.973 |

30 |

366.4155 |

399.722 |

3179.139 |

3198.554 |

9566.732 |

9610.468 |

The benefits of this approach include:

-

Reduced number of host CPU reads and writes to the device.

-

Reduced host memory footprint (less application memory required on the host).

-

Lower latency from 1553 bus to host memory.

Status and Interrupts

The FTA-FTF Function Modules provide registers that indicate faults or events. Refer to “Status and Interrupts Module Manual” for the Principle of Operation description.

Module Common Registers

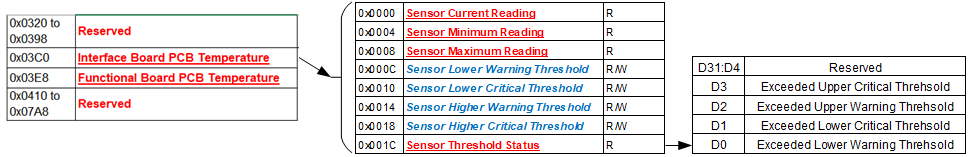

The FTA-FTF Function Modules provide module common registers that provide access to module-level bare metal/FPGA revisions & compile times, unique serial number information, and temperature/voltage/current monitoring. Refer to “Module Common Registers Module Manual” for the detailed information.

REGISTER DESCRIPTIONS

The register descriptions provide the register name, Type, Data Range, Read or Write information, Initialized Value, a description of the function and, in most cases, a data table.

Assisted Mode Registers

The Assisted Mode registers are comprised of registers that support the AM Command and AM 1553 Message FIFOs.

AM Command Registers

The registers associated with the AM Commands are divided into the following:

-

Command FIFO Management (FIFO Buffer, FIFO Count, FIFO Update)

-

Response FIFO Management (FIFO Buffer, FIFO Count)

The Command FIFO registers are used by the host to send commands to the AM processor in order to configure and operate the 1553 IP core. For every command sent from the host processor to the AM processor, the AM processor responds with a message that is sent to the host processor via the Response FIFO Buffer. The content of the response message will vary depending on the command and may contain configuration information, status information or 1553 data.

AM Command FIFO Buffer |

|

Function: |

Used to communicate with the 1553 core via the AM (secondary) processor. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

W |

Initialized Value: |

0 |

Operational Settings: |

The host writes a command message to the AM Command FIFO Buffer and it is read out by the secondary processor. The secondary processor acts on the 1553 core based on the command that was read out. The AM processor will be unaware any new command messages in the AM Command FIFO Buffer until an update is performed by writing a 1 to the AM Command FIFO Update register. |

AM Command FIFO Count |

|

Function: |

This register contains the value representing the number of 32-bit words that are currently loaded in the AM Command FIFO Buffer. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

When the host writes a command message to the AM Command FIFO Buffer, the value of the AM Command FIFO Count represents the number of 32-bit words contained in the command message. Once the message is fully read out by the AM processor, the AM Command FIFO Count goes to zero. |

AM Command FIFO Update |

|

Function: |

This register is used to update the AM Command FIFO count as it is presented to the AM processor. The purpose of this register is to ensure that the AM Command FIFO Buffer does not present incomplete command messages to the AM processor. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 0001 |

Read/Write: |

W |

Initialized Value: |

0 |

Operational Settings: |

The user should write a 1 to this register to update the AM Command FIFO count as it is seen from the AM processor. The proper way to handle sending commands to the AM processor is to write a full command message to the AM Command FIFO Buffer, then update the count by writing a 1 to the AM Command FIFO Update register. |

AM Response FIFO Buffer |

|

Function: |

Used by the AM (secondary) processor to send response messages to the host. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

After the host writes a valid command message to the AM Command FIFO Buffer and it is read out by the AM processor, the AM processor acts on the 1553 core based on the command type. Once the action is completed, the AM processor sends a response to the host processor via the AM Response FIFO Buffer. |

AM Response FIFO Count |

|

Function: |

This register contains the value that represents the number of 32-bit words that are present in the AM Response FIFO Buffer. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

When a command is sent from the host to the AM processor and it completes the commanded task, it loads the AM Response FIFO with a response message and the AM Response FIFO Count is updated with the number of 32-bit words that are contained in the response message. Once the host reads out the full response message from the AM Response FIFO Buffer, the AM Response FIFO Count will read zero. |

AM 1553 Message FIFO Registers

The Message FIFO Management registers consists of the FIFO Buffer, FIFO Count, FIFO Clear command, and the FIFO Threshold which specify threshold associated with for the “1553 Message FIFO Almost Full” status bits in the Channel Status register.

AM 1553 Message FIFO Buffer |

|

Function: |

When the channel is operating in Message FIFO mode, 1553 messages are stored in the 1553 Message FIFO Buffer. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

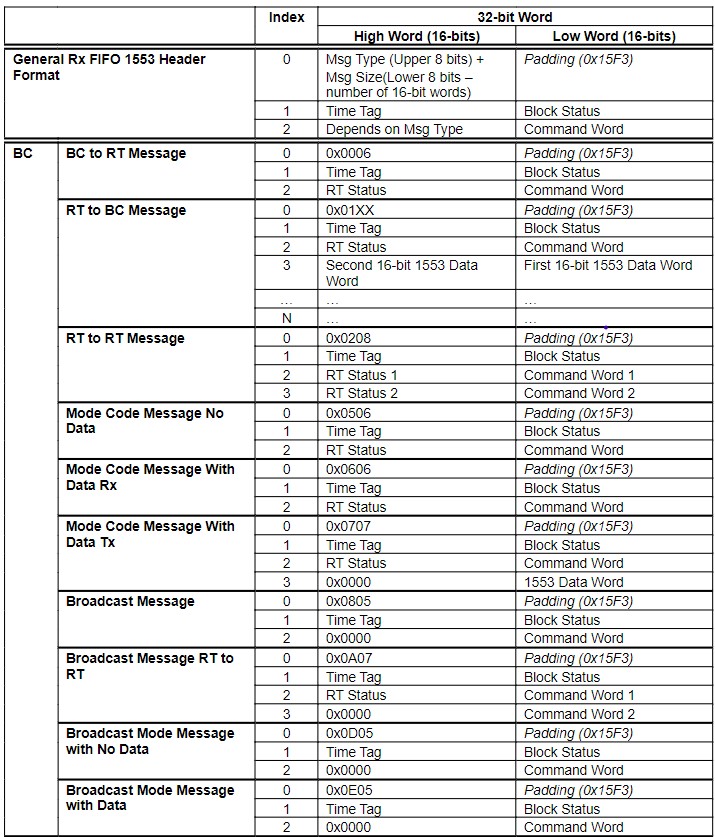

When the channel is configured for Message FIFO mode, new 1553 messages (comprising 1553 data words, 1553 status words, timestamp and message status information) are stored in the 1553 Message FIFO Buffer and the host can perform a block read on this register to read out a chain of 1553 messages in a single transaction. The number of 32-bit words to read out of the 1553 Message FIFO Buffer is reported in the 1553 Message FIFO Count register. Refer to Appendix A: 1553 Receive Message FIFO to decode the single 1553 message or a chain of 1553 messages read from this buffer. |

AM 1553 Message FIFO Count |

|

Function: |

While the channel is operating in Message FIFO mode, the number of 32-bit words in the 1553 Message FIFO Buffer is reported in this register. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

When the channel is configured for Message FIFO mode, new 1553 messages (comprising 1553 data words, 1553 status words, timestamp and message status information) are stored in the 1553 Message FIFO Buffer. The 32-bit count of a 1553 message can vary depending on the 1553 message type and 1553 data payload size. This register provides the count of 32-bit words that are currently present in the 1553 Message FIFO Buffer instead of providing the count of 1553 messages. When retrieving data from the 1553 Message FIFO Buffer, use the 1553 Message FIFO Count to obtain all 1553 messages and refer to Appendix A: 1553 Receive Message FIFO to decode 1553 messages. |

AM 1553 Message FIFO Clear |

|

Function: |

When the channel is operating in Message FIFO mode, this register is used to clear the 1553 Message FIFO Buffer. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

W |

Initialized Value: |

0 |

Operational Settings: |

Write a 1 to this register to clear the 1553 Message FIFO Buffer. Once the buffer is cleared, the 1553 Message FIFO Count register should read zero. |

AM 1553 Message FIFO Threshold |

|

Function: |

Set the “1553 Message FIFO Almost Full” status threshold value. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

1 to 1002 Read/Write: |

R/W |

Initialized Value: |

512 |

Operational Settings: |

Auxiliary Registers

Reset |

|

Function: |

A write to this register causes a reset of the channel/core. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 000F |

Read/Write: |

W (Reset) |

Initialized Value: |

0 |

Operational Settings: |

Reset - Write a 1 to reset the core. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

RT Address from Backplane |

|

Function: |

Provides the Remote Terminal address and the parity. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

See table |

Read/Write: |

R |

Initialized Value: |

0 |

Operational Settings: |

The RT values are set at the backplane and read from this register. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

D |

D |

D |

D |

D |

Bit |

Description |

D31:D6 |

Reserved |

D5 |

RT Parity Bit: 1=Even Parity, 0=Odd Parity |

D4:D0 |

RT Address of the channel. |

Miscellaneous Bits |

|

Function: |

Provides various control and configuration functions as well as status. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

See table |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

Refer to table for definitions. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

Bit |

Description |

D31:D16 |

Reserved |

D15 |

If set, overrides external BC_DISABLE (Bus Controller Mode) with the value from bit 14 |

D14 |

BC_DISABLE override value |

D13 |

If set, overrides external M1760 hardware input (Standard) with the value from bit 12 |

D12 |

M1760 override value |

D11 |

Reserved |

D10 |

Mode value from backplane (Read Only) |

D9 |

Standard value from backplane (Read Only) Default |

D8 |

Terminate RS-422 : 0=No termination, 1=termination |

D7 |

Transceiver Type : 0=Sital, 1=COTS (Read Only) |

D6 |

BC_DISABLE setting at the core (Read Only) |

D5 |

SSFLAG: RT Mode Only - Sets the Sub System flag (bit 2) high in the status word |

D4 |

RTAD_SW_EN: |

D3 |

RT_ADR_LAT: |

D2 |

M1760 Setting at the core (Read Only) |

D1 |

Tx_inhB: |

D0 |

Tx_inhA: |

Module Common Registers

Refer to “Module Common Registers Module Manual” for the register descriptions.

Status and Interrupt Registers

The FTA-FTF Modules provides status registers for BIT and Channel Status.

BIT Status

There are four registers associated with the BIT Status: Dynamic, Latched, Interrupt Enable, and Set Edge/Level Interrupt.

BIT Status |

|

Function: |

Sets the corresponding bit associated with the channel’s BIT register. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0x0000 000F |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt) |

Initialized Value: |

0 |

BIT Dynamic Status |

|||||||||||||||

BIT Latched Status |

|||||||||||||||

BIT Interrupt Enable |

|||||||||||||||

BIT Set Edge/Level Interrupt |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Ch4 |

Ch3 |

Ch2 |

Ch1 |

Channel Status

There are four registers associated with the Channel Status: Dynamic, Latched, Interrupt Enable, and Set Edge/Level Interrupt. Use this register to read current or real-time status.

Channel Status |

|

Function: |

Sets the corresponding bit associated with the event type. There are separate registers for each channel. |

Type: |

unsigned binary word (32-bit) |

Range: |

0 to 0x0000 001F |

Read/Write: |

R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt) |

Initialized Value: |

N/A |

Bit |

Description |

Notes |

D0 |

1553 Core Interrupt |

An interrupt has been signaled from the 1553 core. The specific interrupt signaling event(s) can be identified by reading the core status registers. |

D1 |

1553 Message FIFO Full |

The 1553 Message FIFO is full and will not store any additional messages until messages are read out or the FIFO is cleared. |

D2 |

1553 Message FIFO Almost Full |

The 1553 Message FIFO is almost full. The almost full threshold may be set by writing a value between 1 and 1002 to the Message FIFO Almost Full Threshold register. |

D3 |

1553 Message FIFO Empty |

The 1553 Message FIFO does not contain any messages. |

D4 |

1553 Message FIFO Rx Available |

The 1553 Message FIFO contains one or more messages. |

D31:D5 |

Reserved |

Channel Dynamic Status |

|||||||||||||||

Channel Latched Status |

|||||||||||||||

Channel Interrupt Enable |

|||||||||||||||

Channel Set Edge/Level Interrupt |

|||||||||||||||

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

D |

D |

D |

D |

Interrupt Vector and Steering

When interrupts are enabled, the interrupt vector associated with the specific interrupt can be programmed (typically with a unique number/identifier) such that it can be utilized in the Interrupt Service Routine (ISR) to identify the type of interrupt. When an interrupt occurs, the contents of the Interrupt Vector registers is reported as part of the interrupt mechanism. In addition to specifying the interrupt vector, the interrupt can be directed (“steered”) to the native bus or to the application running on the onboard ARM processor.

|

Note

|

The Interrupt Vector and Interrupt Steering registers are mapped to the Motherboard Common Memory and these registers are associated with the Module Slot position (refer to Function Register Map). |

Interrupt Vector |

|

Function: |

Set an identifier for the interrupt. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, this value is reported as part of the interrupt mechanism. |

Interrupt Steering |

|

Function: |

Sets where to direct the interrupt. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

See table Read/Write: R/W |

Initialized Value: |

0 |

Operational Settings: |

When an interrupt occurs, the interrupt is sent as specified: |

Direct Interrupt to VME |

1 |

Direct Interrupt to ARM Processor (via SerDes) |

2 |

Direct Interrupt to PCIe Bus |

5 |

Direct Interrupt to cPCI Bus |

6 |

FUNCTION REGISTER MAP

KEY

Configuration/Control |

Status |

| AM COMMANDS REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x10B0 |

AM Command FIFO Buffer Ch 1 |

W |

0x10B4 |

AM Command FIFO Count Ch 1 |

R |

0x18B0 |

AM Command FIFO Buffer Ch 2 |

W |

0x18B4 |

AM Command FIFO Count Ch 2 |

R |

0x20B0 |

AM Command FIFO Buffer Ch 3 |

W |

0x20B4 |

AM Command FIFO Count Ch 3 |

R |

0x28B0 |

AM Command FIFO Buffer Ch 4 |

W |

0x28B4 |

AM Command FIFO Count Ch 4 |

R |

0x10B8 |

AM Command FIFO Update Ch 1 |

W |

|||

0x18B8 |

AM Command FIFO Update Ch 2 |

W |

|||

0x20B8 |

AM Command FIFO Update Ch 3 |

W |

|||

0x28B8 |

AM Command FIFO Update Ch 4 |

W |

|||

0x10C0 |

AM Response FIFO Buffer Ch 1 |

R |

0x10C4 |

AM Response FIFO Count Ch 1 |

R |

0x18C0 |

AM Response FIFO Buffer Ch 2 |

R |

0x18C4 |

AM Response FIFO Count Ch 2 |

R |

0x20C0 |

AM Response FIFO Buffer Ch 3 |

R |

0x20C4 |

AM Response FIFO Count Ch 3 |

R |

0x28C0 |

AM Response FIFO Buffer Ch 4 |

R |

0x28C4 |

AM Response FIFO Count Ch 4 |

R |

| AM 1553 MESSAGE FIFO REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x10D0 |

AM 1553 Message FIFO Buffer Ch 1 |

R |

0x10D4 |

AM Message FIFO Count Ch 1 |

R |

0x18D0 |

AM 1553 Message FIFO Buffer Ch 2 |

R |

0x18D4 |

AM Message FIFO Count Ch 2 |

R |

0x20D0 |

AM 1553 Message FIFO Buffer Ch 3 |

R |

0x20D4 |

AM Message FIFO Count Ch 3 |

R |

0x28D0 |

AM 1553 Message FIFO Buffer Ch 4 |

R |

0x28D4 |

AM Message FIFO Count Ch 4 |

R |

0x10D8 |

AM Message FIFO Clear Ch 1 |

W |

0x10DC |

AM Message FIFO Threshold Ch 1 |

R/W |

0x18D8 |

AM Message FIFO Clear Ch 2 |

W |

0x18DC |

AM Message FIFO Threshold Ch 2 |

R/W |

0x20D8 |

AM Message FIFO Clear Ch 3 |

W |

0x20DC |

AM Message FIFO Threshold Ch 3 |

R/W |

0x28D8 |

AM Message FIFO Clear Ch 4 |

W |

0x28DC |

AM Message FIFO Threshold Ch 4 |

R/W |

| AUXILIARY REGISTERS | |||||

|---|---|---|---|---|---|

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x1080 |

RT Address from Backplane Ch 1 |

R |

0x1080 |

Reset Ch 1 |

W |

0x1880 |

RT Address from Backplane Ch 2 |

R |

0x1880 |

Reset Ch 2 |

W |

0x2080 |

RT Address from Backplane Ch 3 |

R |

0x2080 |

Reset Ch 3 |

W |

0x2880 |

RT Address from Backplane Ch 4 |

R |

0x2880 |

Reset Ch 4 |

W |

0x1084 |

Miscellaneous Bits Ch 1 |

R/W |

|||

0x1884 |

Miscellaneous Bits Ch 2 |

R/W |

|||

0x2084 |

Miscellaneous Bits Ch 3 |

R/W |

|||

0x2884 |

Miscellaneous Bits Ch 4 |

R/W |

|||

| MODULE COMMON REGISTERS | |||||

|---|---|---|---|---|---|

Refer to “Module Common Registers Module Manual” for the Module Common Registers Function Register Map. |

| BIT STATUS REGISTERS | |||||

|---|---|---|---|---|---|

*When an event is detected, the bit associated with the event is set in this register and will remain set until the user clears the event bit. Clearing the bit requires writing a 1 back to the specific bit that was set when read (i.e., write-1-to-clear, writing a “1” to a bit set to “1” will set the bit to “0). |

|||||

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x0800 |

Dynamic Status |

R |

|||

0x0804 |

Latched Status* |

R/W |

|||

0x0808 |

Interrupt Enable |

R/W |

|||

0x080C |

Set Edge/Level Interrupt |

R/W |

|||

| 1553 CHANNEL STATUS REGISTERS | |||||

|---|---|---|---|---|---|

*When an event is detected, the bit associated with the event is set in this register and will remain set until the user clears the event bit. Clearing the bit requires writing a 1 back to the specific bit that was set when read (i.e., write-1-to-clear, writing a “1” to a bit set to “1” will set the bit to “0”). |

|||||

NOTE: Base Address - 0x4000 0000 |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x0810 |

Channel Dynamic Status Ch 1 |

R |

0x0820 |

Channel Dynamic Status Ch 2 |

R |

0x0814 |

Channel Latched Status Ch 1* |

R/W |

0x0824 |

Channel Latched Status Ch 2* |

R/W |

0x0818 |

Channel Interrupt Enable Ch 1 |

R/W |

0x0828 |

Channel Interrupt Enable Ch 2 |

R/W |

0x081C |

Channel Set Edge/Level Interrupt Ch 1 |

R/W |

0x082C |

Channel Set Edge/Level Interrupt Ch 2 |

R/W |

0x0830 |

Channel Dynamic Status Ch 3 |

R |

0x0840 |

Channel Dynamic Status Ch 4 |

R |

0x0834 |

Channel Latched Status Ch 3* |

R/W |

0x0844 |

Channel Latched Status Ch 4* |

R/W |

0x0838 |

Channel Interrupt Enable Ch 3 |

R/W |

0x0848 |

Channel Interrupt Enable Ch 4 |

R/W |

0x083C |

Channel Set Edge/Level Interrupt Ch 3 |

R/W |

0x084C |

Channel Set Edge/Level Interrupt Ch 4 |

R/W |

| INTERRUPT REGISTERS | |||||

|---|---|---|---|---|---|

The Interrupt Vector and Interrupt Steering registers are located on the Motherboard Memory Space and do not require any Module Address Offsets. These registers are accessed using the absolute addresses listed in the table below. |

|||||

OFFSET |

REGISTER NAME |

ACCESS |

OFFSET |

REGISTER NAME |

ACCESS |

0x0500 |

Module 1 Interrupt Vector 1 - BIT |

R/W |

0x0600 |

Module 1 Interrupt Steering 1 - BIT |

R/W |

0x0504 |

Module 1 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0604 |

Module 1 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0508 |

Module 1 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0608 |

Module 1 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x050C |

Module 1 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x060C |

Module 1 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0510 |

Module 1 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0610 |

Module 1 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0514 to 0x057C |

Module 1 Interrupt Vector 6 to 32 - Reserved |

R/W |

0x0614 to 0x067C |

Module 1 Interrupt Steering 6 to 32 - Reserved |

R/W |

0x0700 |

Module 2 Interrupt Vector 1 - BIT |

R/W |

0x0800 |

Module 2 Interrupt Steering 1 - BIT |

R/W |

0x0704 |

Module 2 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0804 |

Module 2 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0708 |

Module 2 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0808 |

Module 2 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x070C |

Module 2 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x080C |

Module 2 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0710 |

Module 2 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0810 |

Module 2 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0714 to 0x077C |

Module 2 Interrupt Vector 6 to 32 - Reserved |

R/W |

0x0814 to 0x087C |

Module 2 Interrupt Steering 6 to 32 - Reserved |

R/W |

0x0900 |

Module 3 Interrupt Vector 1 - BIT |

R/W |

0x0A00 |

Module 3 Interrupt Steering 1 - BIT |

R/W |

0x0904 |

Module 3 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0A04 |

Module 3 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0908 |

Module 3 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0A08 |

Module 3 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x090C |

Module 3 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x0A0C |

Module 3 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0910 |

Module 3 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0A10 |

Module 3 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0914 to 0x097C |

Module 3 Interrupt Vector 6 to 32 - Reserved |

R/W |

0x0A14 to 0x0A7C |

Module 3 Interrupt Steering 6 to 32 - Reserved |

R/W |

0x0B00 |

Module 4 Interrupt Vector 1 - BIT |

R/W |

0x0C00 |

Module 4 Interrupt Steering 1 - BIT |

R/W |

0x0B04 |

Module 4 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0C04 |

Module 4 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0B08 |

Module 4 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0C08 |

Module 4 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x0B0C |

Module 4 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x0C0C |

Module 4 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0B10 |

Module 4 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0C10 |

Module 4 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0B14 to 0x0B7C |

Module 4 Interrupt Vector 6 to 32 - Reserved |

R/W |

0x0C14 to 0x0C7C |

Module 4 Interrupt Steering 6 to 32 - Reserved |

R/W |

0x0D00 |

Module 5 Interrupt Vector 1 - BIT |

R/W |

0x0E00 |

Module 5 Interrupt Steering 1 - BIT |

R/W |

0x0D04 |

Module 5 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x0E04 |

Module 5 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0D08 |

Module 5 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x0E08 |

Module 5 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x0D0C |

Module 5 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x0E0C |

Module 5 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0D10 |

Module 5 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x0E10 |

Module 5 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0D14 to 0x0D14 |

Module 5 Interrupt Vector 6 to 32 - Reserved |

R/W |

0x0E0C to 0x0E7C |

Module 5 Interrupt Steering 6 to 32 - Reserved |

R/W |

0x0F00 |

Module 6 Interrupt Vector 1 - BIT |

R/W |

0x1000 |

Module 6 Interrupt Steering 1 - BIT |

R/W |

0x0F04 |

Module 6 Interrupt Vector 2 - Channel Status Ch 1 |

R/W |

0x1004 |

Module 6 Interrupt Steering 2 - Channel Status Ch 1 |

R/W |

0x0F08 |

Module 6 Interrupt Vector 3 - Channel Status Ch 2 |

R/W |

0x1008 |

Module 6 Interrupt Steering 3 - Channel Status Ch 2 |

R/W |

0x0F0C |

Module 6 Interrupt Vector 4 - Channel Status Ch 3 |

R/W |

0x100C |

Module 6 Interrupt Steering 4 - Channel Status Ch 3 |

R/W |

0x0F10 |

Module 6 Interrupt Vector 5 - Channel Status Ch 4 |

R/W |

0x1010 |

Module 6 Interrupt Steering 5 - Channel Status Ch 4 |

R/W |

0x0F0C to 0x0F7C |

Module 6 Interrupt Vector 6 to 32 - Reserved |

R/W |

0x100C to 0x107C |

Module 6 Interrupt Steering 6 to 32 - Reserved |

R/W |

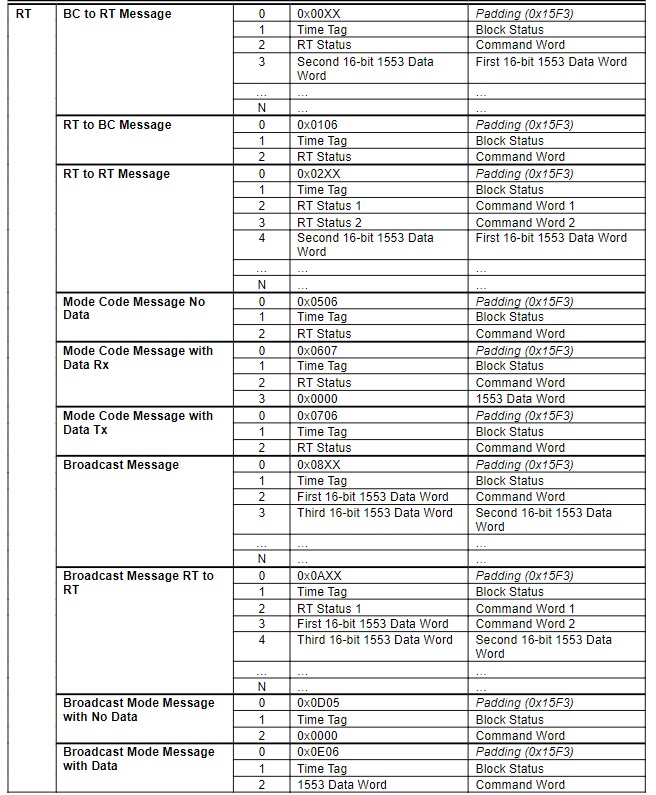

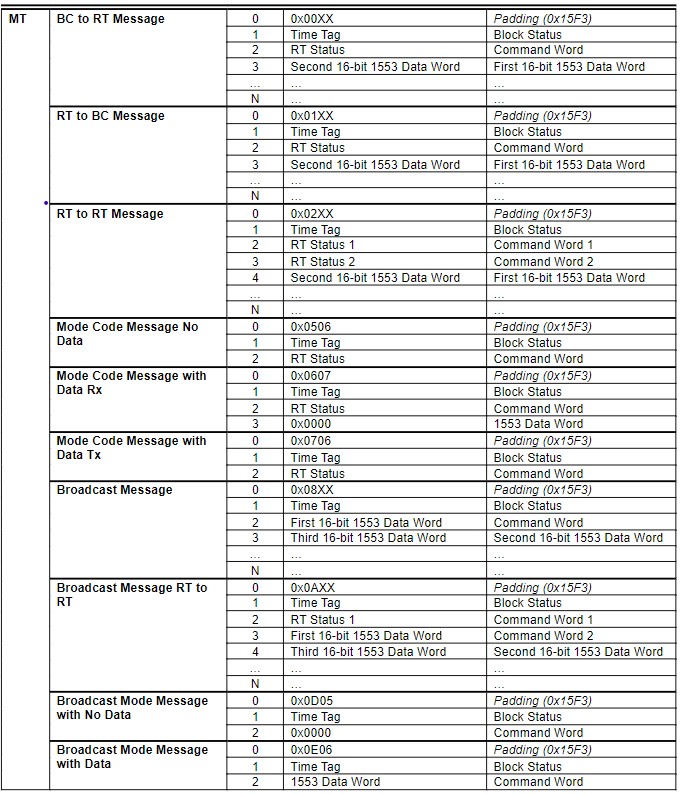

APPENDIX A: 1553 RECEIVE MESSAGE FIFO FORMAT

1553 Memory Map with Buffers Example: BC Mode - 4 1553 Message

1553 Message FIFO Buffer (Packed as 32-bit Words to improve data transfer speeds - message padded to end on 32-bit boundaries |

||||

32-Bit Word Index |

16-Bit Word Index |

- |

- |

- |

0 |

1,0 |

BC to RT Msg |

0x0006 |

Padding (0x15F3) |

1 |

3,2 |

- |

Time Tag |

Block Status |

2 |

5,4 |

- |

RT Status |

Command Word |

3 |

7,6 |

RT to BC Msg |

0x0105 |

Padding (0x15F3) |

4 |

9,8 |

- |

Time Tag |

Block Status |

5 |

11,10 |

- |

RT Status |

Command Word |

6 |

13,12 |

- |

1553 Data Word 2 |

1553 Data Word 1 |

7 |

15,14 |

- |

1553 Data Word 4 |

1553 Data Word 3 |

8 |

17,16 |

- |

Padding (0x0000) |

1553 Data Word 5 |

9 |

19,18 |

RT to RT Msg |

0x0208 |

Padding (0x15F3) |

10 |

21,20 |

- |

Time Tag |

Block Status |

11 |

23,22 |

- |

RT Status 1 |

Command Word 1 |

12 |

25,24 |

- |

RT Status 2 |

Command Word 2 |

13 |

27,26 |

Broadcast Message RT to RT |

0x0A07 |

Padding (0x15F3) |

14 |

29,28 |

- |

Time Tag |

Block Status |

15 |

31,30 |

- |

RT Status 1 |

Command Word 1 |

16 |

33,32 |

- |

0x0000 |

Command Word 2 |

1553 Message FIFO Count |

17 |

APPENDIX B: PIN-OUT DETAILS

Pin-out details (for reference) are shown below, with respect to DATAIO. Additional information on pin-outs can be found in the Motherboard Operational Manuals.

Module Signal (Ref Only) |

44-Pin I/O |

50-Pin I/O (Mod Slot 1-J3) |

50-Pin I/O (Mod Slot 2-J4) |

50-Pin I/O (Mod Slot 3-J3) |

50-Pin I/O (Mod Slot 3-J4) |

MIL-STD-1553+ (FTA-FTF)* |

DATIO1 |

2 |

10 |

1 |

2 |

BUSAP-CH1 |

|

DATIO2 |

24 |

35 |

26 |

27 |

BUSAN-CH1 |

|

DATIO3 |

3 |

11 |

2 |

3 |

BUSBP-CH1 |

|

DATIO4 |

25 |

36 |

27 |

28 |

BUSBN-CH1 |

|

DATIO5 |

5 |

13 |

4 |

5 |

CH1-RT-ADDR2/ANP1 |

|

DATIO6 |

27 |

38 |

29 |

30 |

CH1-RT-ADDR3/ANN1 |

|

DATIO7 |

7 |

14 |

5 |

6 |

BUSAP-CH2 |

|

DATIO8 |

29 |

39 |

30 |

31 |

BUSAN-CH2 |

|

DATIO9 |

8 |

15 |

6 |

7 |

BUSBP-CH2 |

|

DATIO10 |

30 |

40 |

31 |

32 |

BUSBN-CH2 |

|

DATIO11 |

10 |

17 |

8 |

9 |

CH1-STANDARD/BNP1 |

|

DATIO12 |

32 |

42 |

33 |

34 |

CH1-MODE0/BNN1 |

|

DATIO13 |

12 |

18 |

9 |

17 |

BUSAP-CH3 |

|

DATIO14 |

34 |

43 |

34 |

42 |

BUSAN-CH3 |

|

DATIO15 |

13 |

19 |

10 |

18 |

BUSBP-CH3 |

|

DATIO16 |

35 |

44 |

35 |

43 |

BUSBN-CH3 |

|

DATIO17 |

15 |

21 |

12 |

20 |

CH3-RT-ADDR2/ANP3 |

|

DATIO18 |

37 |

46 |

37 |

45 |

CH3-RT-ADDR3/ANN3 |

|

DATIO19 |

17 |

22 |

13 |

21 |

BUSAP-CH4 |

|

DATIO20 |

39 |

47 |

38 |

46 |

BUSAN-CH4 |

|

DATIO21 |

18 |

23 |

14 |

22 |

BUSBP-CH4 |

|

DATIO22 |

40 |

48 |

39 |

47 |

BUSBN-CH4 |

|

DATIO23 |

20 |

25 |

16 |

24 |

CH3-STANDARD/BNP1 |

|

DATIO24 |

42 |

50 |

41 |

49 |

CH3-MODE0/BNN1 |

|

DATIO25 |

4 |

12 |

3 |

4 |

CH1-RT-ADDR0/APP1 |

|

DATIO26 |

26 |

37 |

28 |

29 |

CH1-RT-ADDR1/APN1 |

|

DATIO27 |

9 |

16 |

7 |

8 |

CH1-RT-ADDR4/BPP1 |

|

DATIO28 |

31 |

41 |

32 |

33 |

CH1-RT-PARITY/BPN1 |

|

DATIO29 |

14 |

20 |

11 |

19 |

CH3-RT-ADDR0/APP3 |

|

DATIO30 |

36 |

45 |

36 |

44 |

CH3-RT-ADDR1/APN3 |

|

DATIO31 |

19 |

24 |

15 |

23 |

CH3-RT-ADDR4/BPP3 |

|

DATIO32 |

41 |

49 |

40 |

48 |

CH3-PARITY/BPN3 |

|

DATIO33 |

6 |

|||||

DATIO34 |

28 |

|||||

DATIO35 |

11 |

|||||

DATIO36 |

33 |

|||||

DATIO37 |

16 |

|||||

DATIO38 |

38 |

|||||

DATIO39 |

21 |

|||||

DATIO40 |

43 |

|||||

N/A |

NOTES:

* |

FTA & FTD - single channel MIL-STD-1553 communication modules are referenced/controlled as “CH1” FTB & FTE - dual channel MIL-STD-1553 communication modules are referenced/controlled as “CH1 & CH3” FTC & FTF - quad channel MIL-STD-1553 communication modules are referenced/controlled as “CH1 - CH4” For the FTC & FTF CH1&2 and CH3&4 are paired. The address of the even channel is set at the odd channel hardwire address +1. |

REVISION HISTORY

Module Manual - FTA-FTF Revision History |

||

Revision |

Revision Date |

Description |

C |

2023-11-15 |

ECO C10945, transition to docbuilder format. Pg.5-6, replaced specifications section with data sheet. Pg.7, updated Introduction; replaced Features with FTA-FTF Overview. Pg.16, added Status and Interrupts. Pg.16/21/26, added Module Common Registers. Pg.20, added column headings to bit description table; changed 'B' to 'D' in table. Pg.21, added column headings to bit description table; changed 'B' to 'D' in table. Pg.24, added Interrupt Vector and Steering. Added Appendix B. |

DOCS.NAII REVISIONS

Revision Date |

Description |

2026-03-23 |

Added duplicate pinouts for DATIO11, DATIO12, DATIO17, and DATIO18 to allow for I/O over the first 24 pins of module; added note to indicate duplicate pins; additional formatting updates throughout manual (no technical info changed). |

STATUS AND INTERRUPTS

Edit this on GitLab

Status registers indicate the detection of faults or events. The status registers can be channel bit-mapped or event bit-mapped. An example of a channel bit-mapped register is the BIT status register, and an example of an event bit-mapped register is the FIFO status register.

For those status registers that allow interrupts to be generated upon the detection of the fault or the event, there are four registers associated with each status: Dynamic, Latched, Interrupt Enabled, and Set Edge/Level Interrupt.

Dynamic Status: The Dynamic Status register indicates the current condition of the fault or the event. If the fault or the event is momentary, the contents in this register will be clear when the fault or the event goes away. The Dynamic Status register can be polled, however, if the fault or the event is sporadic, it is possible for the indication of the fault or the event to be missed.

Latched Status: The Latched Status register indicates whether the fault or the event has occurred and keeps the state until it is cleared by the user. Reading the Latched Status register is a better alternative to polling the Dynamic Status register because the contents of this register will not clear until the user commands to clear the specific bit(s) associated with the fault or the event in the Latched Status register. Once the status register has been read, the act of writing a 1 back to the applicable status register to any specific bit (channel/event) location will “clear” the bit (set the bit to 0). When clearing the channel/event bits, it is strongly recommended to write back the same bit pattern as read from the Latched Status register. For example, if the channel bit-mapped Latched Status register contains the value 0x0000 0005, which indicates fault/event detection on channel 1 and 3, write the value 0x0000 0005 to the Latched Status register to clear the fault/event status for channel 1 and 3. Writing a “1” to other channels that are not set (example 0x0000 000F) may result in incorrectly “clearing” incoming faults/events for those channels (example, channel 2 and 4).

Interrupt Enable: If interrupts are preferred upon the detection of a fault or an event, enable the specific channel/event interrupt in the Interrupt Enable register. The bits in Interrupt Enable register map to the same bits in the Latched Status register. When a fault or event occurs, an interrupt will be fired. Subsequent interrupts will not trigger until the application acknowledges the fired interrupt by clearing the associated channel/event bit in the Latched Status register. If the interruptible condition is still persistent after clearing the bit, this may retrigger the interrupt depending on the Edge/Level setting.

Set Edge/Level Interrupt: When interrupts are enabled, the condition on retriggering the interrupt after the Latch Register is “cleared” can be specified as “edge” triggered or “level” triggered. Note, the Edge/Level Trigger also affects how the Latched Register value is adjusted after it is “cleared” (see below).

-

Edge triggered: An interrupt will be retriggered when the Latched Status register change from low (0) to high (1) state. Uses for edge-triggered interrupts would include transition detections (Low-to-High transitions, High-to-Low transitions) or fault detections. After “clearing” an interrupt, another interrupt will not occur until the next transition or the re-occurrence of the fault again.

-

Level triggered: An interrupt will be generated when the Latched Status register remains at the high (1) state. Level-triggered interrupts are used to indicate that something needs attention.

Interrupt Vector and Steering

When interrupts are enabled, the interrupt vector associated with the specific interrupt can be programmed with a unique number/identifier defined by the user such that it can be utilized in the Interrupt Service Routine (ISR) to identify the type of interrupt. When an interrupt occurs, the contents of the Interrupt Vector registers is reported as part of the interrupt mechanism. In addition to specifying the interrupt vector, the interrupt can be directed (“steered”) to the native bus or to the application running on the onboard ARM processor.

Interrupt Trigger Types

In most applications, limiting the number of interrupts generated is preferred as interrupts are costly, thus choosing the correct Edge/Level interrupt trigger to use is important.

Example 1: Fault detection

This example illustrates interrupt considerations when detecting a fault like an “open” on a line. When an “open” is detected, the system will receive an interrupt. If the “open” on the line is persistent and the trigger is set to “edge”, upon “clearing” the interrupt, the system will not regenerate another interrupt. If, instead, the trigger is set to “level”, upon “clearing” the interrupt, the system will re-generate another interrupt. Thus, in this case, it will be better to set the trigger type to “edge”.

Example 2: Threshold detection

This example illustrates interrupt considerations when detecting an event like reaching or exceeding the “high watermark” threshold value. In a communication device, when the number of elements received in the FIFO reaches the high-watermark threshold, an interrupt will be generated. Normally, the application would read the count of the number of elements in the FIFO and read this number of elements from the FIFO. After reading the FIFO data, the application would “clear” the interrupt. If the trigger type is set to “edge”, another interrupt will be generated only if the number of elements in FIFO goes below the “high watermark” after the “clearing” the interrupt and then fills up to reach the “high watermark” threshold value. Since receiving communication data is inherently asynchronous, it is possible that data can continue to fill the FIFO as the application is pulling data off the FIFO. If, at the time the interrupt is “cleared”, the number of elements in the FIFO is at or above the “high watermark”, no interrupts will be generated. In this case, it will be better to set the trigger type to “level”, as the purpose here is to make sure that the FIFO is serviced when the number of elements exceeds the high watermark threshold value. Thus, upon “clearing” the interrupt, if the number of elements in the FIFO is at or above the “high watermark” threshold value, another interrupt will be generated indicating that the FIFO needs to be serviced.

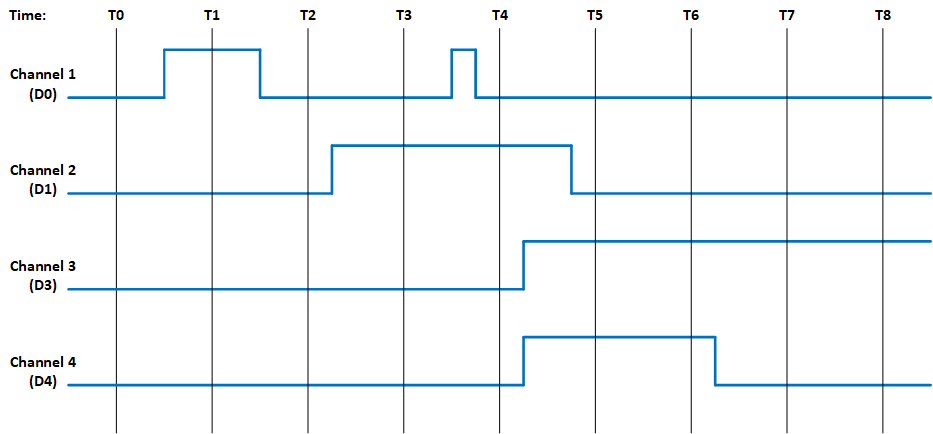

Dynamic and Latched Status Registers Examples

The examples in this section illustrate the differences in behavior of the Dynamic Status and Latched Status registers as well as the differences in behavior of Edge/Level Trigger when the Latched Status register is cleared.

Figure 1. Example of Module’s Channel-Mapped Dynamic and Latched Status States

| No Clearing of Latched Status | Clearing of Latched Status (Edge-Triggered) | Clearing of Latched Status(Level-Triggered) | ||||

|---|---|---|---|---|---|---|

Time |

Dynamic Status |

Latched Status |

Action |

Latched Status |

Action |

Latched |

T0 |

0x0 |

0x0 |

Read Latched Register |

0x0 |

Read Latched Register |

0x0 |

T1 |

0x1 |

0x1 |

Read Latched Register |

0x1 |

0x1 |

|

T1 |

0x1 |

0x1 |

Write 0x1 to Latched Register |

Write 0x1 to Latched Register |

||

T1 |

0x1 |

0x1 |

0x0 |

0x1 |

||

T2 |

0x0 |

0x1 |

Read Latched Register |

0x0 |

Read Latched Register |

0x1 |

T2 |

0x0 |

0x1 |

Read Latched Register |

0x0 |

Write 0x1 to Latched Register |

|

T2 |

0x0 |

0x1 |

Read Latched Register |

0x0 |

0x0 |

|

T3 |

0x2 |

0x3 |

Read Latched Register |

0x2 |

Read Latched Register |

0x2 |

T3 |

0x2 |

0x3 |

Write 0x2 to Latched Register |

Write 0x2 to Latched Register |

||

T3 |

0x2 |

0x3 |

0x0 |

0x2 |

||

T4 |

0x2 |

0x3 |

Read Latched Register |

0x1 |

Read Latched Register |

0x3 |

T4 |

0x2 |

0x3 |

Write 0x1 to Latched Register |

Write 0x3 to Latched Register |

||

T4 |

0x2 |

0x3 |

0x0 |

0x2 |

||

T5 |

0xC |

0xF |

Read Latched Register |

0xC |

Read Latched Register |

0xE |

T5 |

0xC |

0xF |

Write 0xC to Latched Register |

Write 0xE to Latched Register |

||

T5 |

0xC |

0xF |

0x0 |

0xC |

||

T6 |

0xC |

0xF |

Read Latched Register |

0x0 |

Read Latched |

0xC |

T6 |

0xC |

0xF |

Read Latched Register |

0x0 |

Write 0xC to Latched Register |

|

T6 |

0xC |

0xF |

Read Latched Register |

0x0 |

0xC |

|

T7 |

0x4 |

0xF |

Read Latched Register |

0x0 |

Read Latched Register |

0xC |

T7 |

0x4 |

0xF |

Read Latched Register |

0x0 |

Write 0xC to Latched Register |

|

T7 |

0x4 |

0xF |

Read Latched Register |

0x0 |

0x4 |

|

T8 |

0x4 |

0xF |

Read Latched Register |

0x0 |

Read Latched Register |

0x4 |

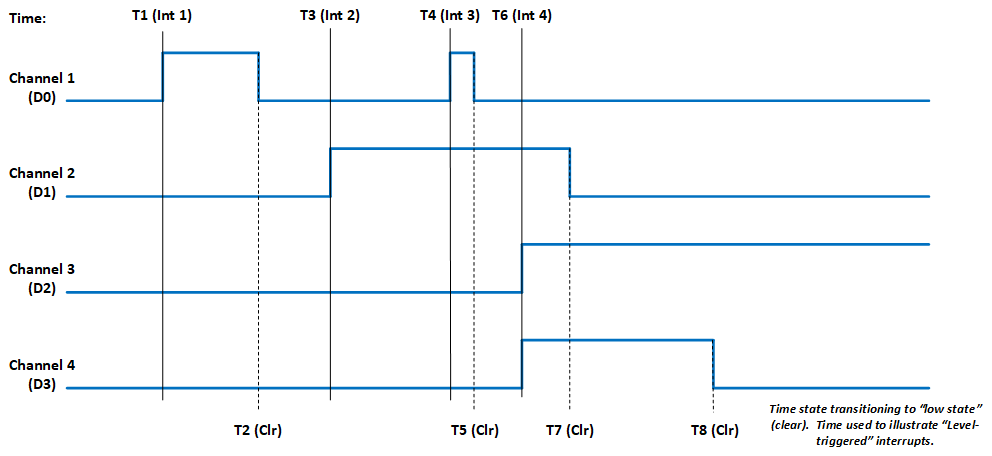

Interrupt Examples

The examples in this section illustrate the interrupt behavior with Edge/Level Trigger.

Figure 2. Illustration of Latched Status State for Module with 4-Channels with Interrupt Enabled

Time |

Latched Status (Edge-Triggered - Clear Multi-Channel) |

Latched Status (Edge-Triggered - Clear Single Channel) |

Latched Status (Level-Triggered - Clear Multi-Channel) |

|||

Action |

Latched |

Action |

Latched |

Action |

Latched |

|

T1 (Int 1) |

Interrupt Generated Read Latched Registers |

0x1 |

Interrupt Generated Read Latched Registers |

0x1 |

Interrupt Generated Read Latched Registers |

0x1 |

T1 (Int 1) |

Write 0x1 to Latched Register |

Write 0x1 to Latched Register |

Write 0x1 to Latched Register |

|||

T1 (Int 1) |

0x0 |

0x0 |

Interrupt re-triggers Note, interrupt re-triggers after each clear until T2. |

0x1 |

||

T3 (Int 2) |

Interrupt Generated Read Latched Registers |

0x2 |

Interrupt Generated Read Latched Registers |

0x2 |

Interrupt Generated Read Latched Registers |

0x2 |

T3 (Int 2) |

Write 0x2 to Latched Register |

Write 0x2 to Latched Register |

Write 0x2 to Latched Register |

|||

T3 (Int 2) |

0x0 |

0x0 |

Interrupt re-triggers Note, interrupt re-triggers after each clear until T7. |

0x2 |

||

T4 (Int 3) |

Interrupt Generated Read Latched Registers |

0x1 |

Interrupt Generated Read Latched Registers |

0x1 |

Interrupt Generated Read Latched Registers |

0x3 |

T4 (Int 3) |

Write 0x1 to Latched Register |

Write 0x1 to Latched Register |

Write 0x3 to Latched Register |

|||

T4 (Int 3) |

0x0 |

0x0 |

Interrupt re-triggers Note, interrupt re-triggers after each clear and 0x3 is reported in Latched Register until T5. |

0x3 |

||

T4 (Int 3) |

0x0 |

0x0 |

Interrupt re-triggers Note, interrupt re-triggers after each clear until T7. |

0x2 |

||

T6 (Int 4) |

Interrupt Generated Read Latched Registers |

0xC |

Interrupt Generated Read Latched Registers |

0xC |

Interrupt Generated Read Latched Registers |

0xE |

T6 (Int 4) |

Write 0xC to Latched Register |

Write 0x4 to Latched Register |

Write 0xE to Latched Register |

|||

T6 (Int 4) |

0x0 |

Interrupt re-triggers Write 0x8 to Latched Register |

0x8 |

Interrupt re-triggers Note, interrupt re-triggers after each clear and 0xE is reported in Latched Register until T7. |

0xE |

|

T6 (Int 4) |

0x0 |

0x0 |

Interrupt re-triggers Note, interrupt re-triggers after each clear and 0xC is reported in Latched Register until T8. |

0xC |

||

T6 (Int 4) |

0x0 |

0x0 |

Interrupt re-triggers Note, interrupt re-triggers after each clear and 0x4 is reported in Latched Register always. |

0x4 |

||

REVISION HISTORY

Motherboard Manual - Status and Interrupts Revision History |

||

Revision |

Revision Date |

Description |

C |

2021-11-30 |

C08896; Transition manual to docbuilder format - no technical info change. |

DOCS.NAII REVISIONS

Revision Date |

Description |

2026-03-02 |

Formatting updates to document; no technical changes. |

MODULE COMMON REGISTERS

Edit this on GitLab

The registers described in this document are common to all NAI Generation 5 modules.

Module Information Registers

The registers in this section provide module information such as firmware revisions, capabilities and unique serial number information.

FPGA Version Registers

The FPGA firmware version registers include registers that contain the Revision, Compile Timestamp, SerDes Revision, Template Revision and Zynq Block Revision information.

FPGA Revision |

|

Function: |

FPGA firmware revision |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Value corresponding to the revision of the board’s FPGA |

Operational Settings: |

The upper 16-bits are the major revision and the lower 16-bits are the minor revision. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Major Revision Number |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Minor Revision Number |

|||||||||||||||

FPGA Compile Timestamp |

|

Function: |

Compile Timestamp for the FPGA firmware. |

Type: |

unsigned binary word (32-bit) |

Data Range: |

N/A |

Read/Write: |

R |

Initialized Value: |

Value corresponding to the compile timestamp of the board’s FPGA |

Operational Settings: |

The 32-bit value represents the Day, Month, Year, Hour, Minutes and Seconds as formatted in the table: |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

day (5-bits) |

month (4-bits) |

year (6-bits) |

hr |

||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

hour (5-bits) |

minutes (6-bits) |

seconds (6-bits) |

|||||||||||||

FPGA SerDes Revision |

|

Function: |

FPGA SerDes revision |

Type: |

unsigned binary word (32-bit) |

Data Range: |

0x0000 0000 to 0xFFFF FFFF |

Read/Write: |

R |

Initialized Value: |

Value corresponding to the SerDes revision of the board’s FPGA |

Operational Settings: |

The upper 16-bits are the major revision, and the lower 16-bits are the minor revision. |

D31 |

D30 |

D29 |

D28 |

D27 |

D26 |

D25 |

D24 |

D23 |

D22 |

D21 |

D20 |

D19 |

D18 |

D17 |

D16 |

Major Revision Number |

|||||||||||||||

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Minor Revision Number |

|||||||||||||||

FPGA Template Revision |

|

Function: |

FPGA Template revision |

Type: |

unsigned binary word (32-bit) |